刚挠印制板高速信号布线设计研究

鲜明

【摘要】 通过某刚挠印制板上高速信号线走线设计研究,解决刚挠印制板高速信号传输的阻抗匹配、信号完整性及电磁干扰等瓶颈问题。

【关键词】 刚挠印制板 高速信号线 阻抗匹配 信号完整性

前言

随着装备用户对设备小型化的要求越来越高,产品研制过程中刚挠印制板应用已非常广泛,但都是利用刚挠印制板传输低速信号(信号速率≤100Mbps)。利用刚挠印制板传输高速信号(信号速率≥400Mbps),调研国内印制板厂家来看,该技术多数应用于商业消费领域,在其他行业应用较少。

刚挠印制板传输高速信号的瓶颈在于信号在挠性区域及刚挠结合处的信号完整性问题:高速信号在挠性区域传输时因阻抗匹配易造成噪声问题,比如振铃、反射及衰减等;高速信号在穿越刚挠结合区域时易产生未知的信号突变。

针对以上问题,我们的设计研究必须保证高速信号线传输的阻抗匹配及防止信号突变。

高速信号线板间传统传输方式

电缆连接

板与板之间连接的高速信号全部用外置电缆连接进行传输。电缆体积较大,会大量占据本来就狭小的设备空间,而且增加设备重量,非常不利于小型化设计。大量电缆线缠绕又影响工艺走线美观和造成EMI电磁干扰等诸多问题;同时在振动冲击较大的恶劣环境下,电缆与普通刚板之间的焊接存在焊点断裂等隐患。

连接器连接

多个模块子板通过连接器与背板连接来传输高速信号。这种方式的连接质量很大程度上依赖于连接器的质量,如果连接器质量不稳定的话,在热冲击和振动冲击的环境下在连接器处很容易引起接触不良和信号传输失真,尤其对高速信号来说这种影响即为严重。

刚挠印制板高速信号线布线需求

某项目提出以刚挠印制板做母板传输3.125Gbps等高速差分信号在内的多类型信号。

随着此类设计需求的增多,迫切需要进行高速刚挠印制板设计研究,以解决工程应用问题,并推广应用。该技术主要应用于有减量和减小体积要求的小型化设备,尤其适用于航空、航天及弹载、箭载等热冲击振动冲击环境恶劣的领域。

布线设计技术

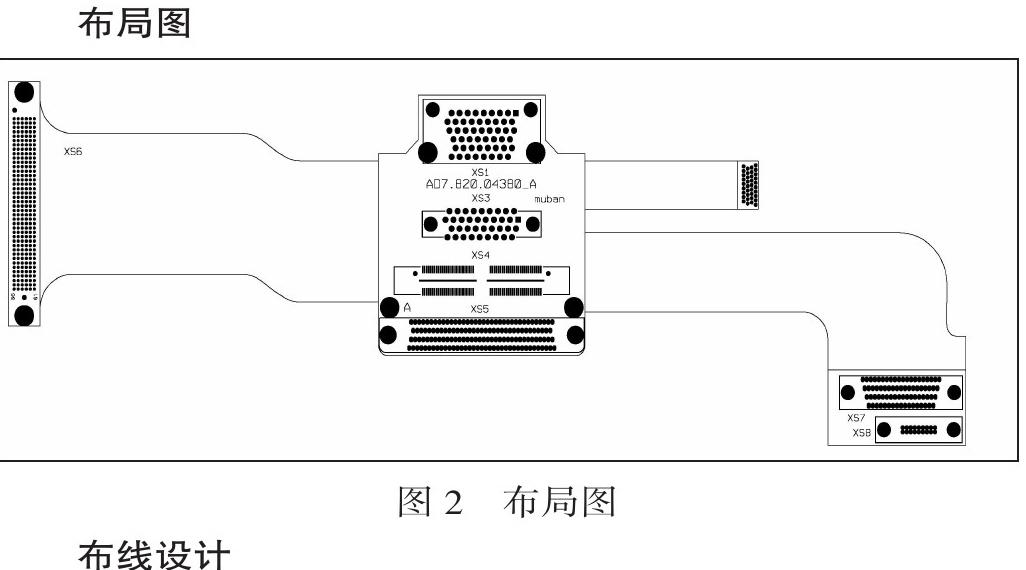

本次我们选取的研究对象为某型号母板。该母板涵盖300Mbps、1Gbps及3.125Gbps等多种高速差分信号,且信号传输环境复杂,成品板刚板层数高达16层(挠板层数高达8层),因此选取该母板作为我们的研究对象具有非常典型的意义。

调研印制板加工厂家,分析刚挠板设计规范,提炼高速信号阻抗匹配要求

分析刚挠印制板设计标准规范,提炼与高速信号线相关的内容,目前行业内高速刚挠印制板加工最高可以做到24层。

刚挠板阻抗影响因素主要包括:叠层结构、介电常数、介质厚度、铜厚、铜箔类型、线宽及间距等。

总体方案设计

本次设计为某型号母板。该设备机箱结构紧凑,减重要求高,震动环境恶劣,系统分支多,该母板总共由四个模块组成,模块之间连接关系复杂。以往常规做法是各模块分别设计,最后通过电缆在母板上进行对接和调试。这样做设备体积难以减小且重量难以减轻,布线较多,用导线进行连接,焊接难度大,可靠性也不高。

对此,我们采用刚挠印制板对母板进行一体化设计,将原来采用电缆或光纤的部分全部采用挠性板来替代,即母板会根据结构空间位置伸出三个分支刚挠印制板,大量的电缆使用薄薄的三个分支刚挠印制板就可完全代替,不仅节约了结构空间,更大大简化了整体设计思路,同时还可将不同类型和频率的信号分门别类地布线,大大减小了相互干扰,提高了产品可靠性。

该刚挠印制板总体方案设计的三维空间模型如图 1所示。

详细设计

对板上传输的信号种类进行梳理,既有4Mbps,又有300Mbps、1Gbps及3.125Gbps等高速差分信号,且这些高速信号在传输过程中将多次穿越不同的刚挠结合区域,因此易造成严重的信号完整性问题:一为高速信号在挠性区域传输时因阻抗匹配易造成噪声问题,比如振铃、反射及衰减等;二为高速信号在穿越刚挠结合区域时易产生未知的信号突变。

根据电路设计要求梳理高速信号种类。

3.125Gbps、1Gbps及300Mbp三种差分信号属于高速敏感信号,若设计不合理,易造成严重的信号完整性问题,是本次研究重点关注对象。

高速信号线详细布线设计

高速差分线阻抗严格控制为100Ω±10%(包含挠性区域)。

高速差分线在传输路径上跨越不同的刚撓结合区域时走线宽度和间距避免突兀过渡,同时采用平滑走线变化设计,避免信号突变。

高速差分线传输路径上避免打过孔、合理的叠层设置、加工时采用压沿铜箔这种延展性好的材料来加工及挠板张与张之间不粘接,保证弯折性。

结束语

普通刚挠印制板在机载、船载、弹载、星载及箭载等各类平台已经得到大量工程化应用。后期经过环境适应性实验后,高速刚挠印制板将在机载、船载、弹载、星载及箭载等平台得到工程化推广应用。

参 考 文 献

[1] 申德骏,谭超.多层印制板叠层设计对信号完整性的影响研究.电子设计工程,2015,15(05):154-157.

[2] 陈世金,邓宏喜,杨诗伟等.铜箔质量对印制板阻抗线宽控制失效影响分析.印制电路信息,2014,12(02):51-54.