基于FPGA的硬件测试电路设计

李富国,宁 凯,徐安俊

(长春大学 机械与车辆工程学院,长春130022)

进入21 世纪,集成电路技术飞速发展,推动了FPGA 的发展。FPGA 集成度高,编程灵活,适用于较大规模的电路设计中,其设计开发周期短,制造成本低,质量稳定,被广泛运用在产品生产中[1-4]。 随着以FPGA 为核心的产品不断上线, 产品的质量问题又成为人们关注的焦点, 而所设计的基于FPGA 的硬件测试电路正是在这一背景下应运而生。 该测试电路可用于实现对各类产品设计过程中可能会出现的问题进行及时调试、检测,从而大大提高生产效率,同时还能满足对不同使用环境的需要,在当下具有广阔的应用前景。

1 硬件测试电路原理

整个硬件测试过程在上位机(PC)控制下完成,并由FPGA 实现逻辑控制测试。 硬件测试电路主要包括触发器、数码管、计数器和寄存器等元器件。 其中,触发器按照触发方式的不同进行区分,分为脉冲触发、电平触发、以及边沿触发,且其可以按照控制方式或者逻辑功能的不同来进行分类[5-6];数码管广泛应用于日常的生产和生活中,其分类主要依据其段数;计数器可以用来分频、定时、对时钟脉冲计数、数字运算等,是一种在时序逻辑电路中应用十分广泛的元器件[7];寄存器是集成电路中非常重要的一种存储单元,可用来暂存指令、数据和地址[8]。

2 硬件测试电路总体方案设计

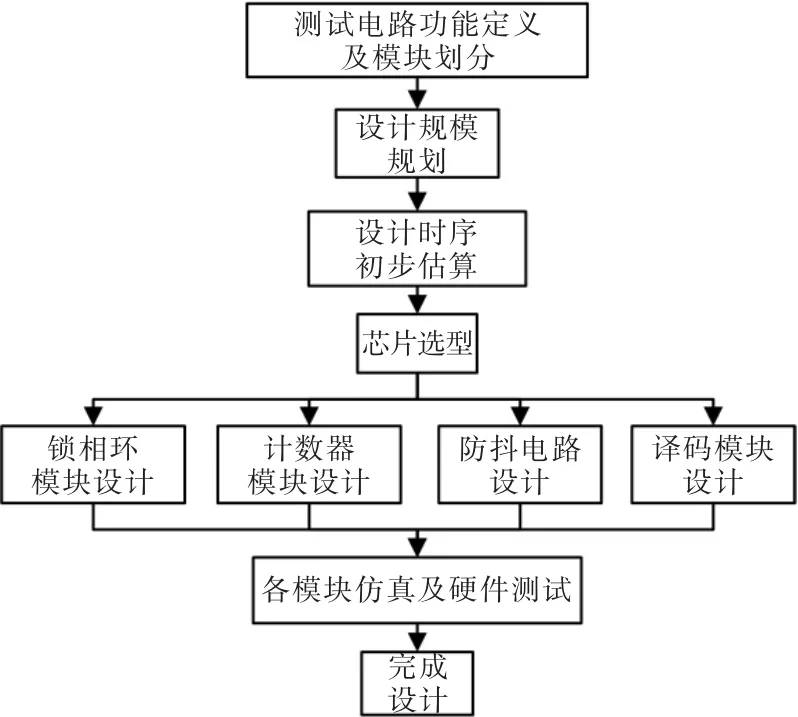

经过对比分析过往硬件电路测试平台的优缺,结合自身设计要求并依据设计目标,制定了总体设计方案。 硬件测试电路总体设计流程如图1 所示。

图1 硬件测试电路总体设计流程Fig.1 Hardware test circuit general design flow chart

3 硬件测试电路设计

硬件测试电路设计以FPGA 为核心, 其硬件部分主要由4 个模块组成:锁相环模块、计数器模块、防抖电路设计、译码器模块。

3.1 锁相环模块设计

锁相环即锁定相位的环路,FPGA 中自带高性能的嵌入式模拟锁相环,其最突出的优点就是能够输出多个同步倍频或分频的片内时钟[9-10]。该片内时钟可大大降低时钟延时对输入输出信号的影响,避免对其它时钟信号产生干扰;还可以通过改善时钟建立时间和保持时间, 以保证系统稳定工作。 Cyclone/Ⅱ/Ⅲ系列和Statix/Ⅱ/Ⅲ/Ⅳ系列器件中的锁相环能直接输入所需要输出的频率,并提供任意相移和输出信号占空比。 锁相环模块如图2 所示。

3.2 计数器模块设计

图2 锁相环模块Fig.2 Phase-locked loop module

计数器模块包括2 个计数器模块,其工作原理一致。 在此以CNT16 模块为例,介绍计数器模块的工作原理。 当输入信号CLK 有效时, 计数器模块CNT16 进行加法计数。输入信号CLK 定义为标准逻辑位STD_LOGIC,输出信号DOUT 的数据类型明确定义为32 位标准逻辑位矢量STD_LOGIC_VECTOR(31 DOWNTO 0)。 计数器内部先定义1 个信号SIGNAL Q1。Q1 为内部的信号,流动不受方向限制,Q1 不断累加。 当满足要求时,将Q1 的值向端口DOUT 输出。 计数器模块如图3 所示。

图3 计数器模块Fig.3 Counter module

3.3 防抖电路设计

防抖电路由4 个D 触发器和1 个4 输入与门构成。4 个D 触发器的时钟输入端都连在一起,工作时与时钟同步工作,输入信号以移位串行方式向前传递。 按键K1 的信号经过非门后成为输入信号,ck是防抖电路自身的工作时钟。 该电路“滤波”功能的关键在于:当信号被串入电路后,能在输出端输出脉冲信号的条件是,必须在4 个D 触发器的输出端Q 都同时为1,从而4 输入与门才能输出高电平。 正因为干扰抖动信号都是一群宽度狭窄的随机信号,在串入时,不可能使与门的输出都为1,因此只有正常信号才有足够的宽度通过此电路,从而起到“滤波”的功能。 防抖电路如图4 所示。

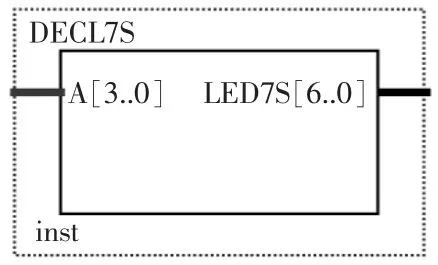

3.4 译码模块设计

译码模块设有七段数码管,并采用动态显示方式。 其中,输出信号LED7S 的7 位分别接数码管的7 个段,高位在左,低位在右。 ,模块的输入信号为4位,输出信号为7 位,最终决定着数码管上显示的结果。

图4 防抖电路Fig.4 Stabilization circuit

例如,当LED7S 输出为“1001111”时,数码管的7 个段为g,f,e,d,c,b,a 分别接于1,0,0,1,1,1,1;接有高电平的段发亮,于是数码管显示“3”。 与此同时,从CNT16 输出的32 位数据中任取8 位,这8 位信号作为输入信号用来测试数码管A 和B。 由于数码管B 在外部电路已经设置了16 进制7 段译码器,所以当信号输入时可直接显示计数值。 译码模块如图5 所示。

图5 译码模块Fig.5 Decoding module

4 硬件测试电路主要模块仿真

利用ALTERA 综合布线工具Quartus Ⅱ,对各主要功能模块以及整体电路进行编译、仿真测试,并使用EP3C5E144C8 芯片对硬件测试电路进行调试。

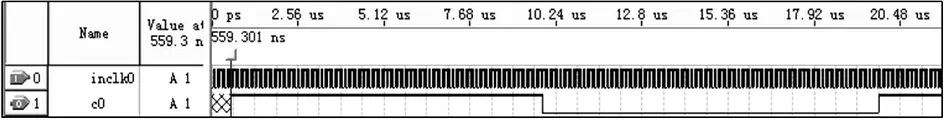

锁相环模块仿真首先对锁相环模块进行仿真。 模块参数设置如下:时序仿真开始时间为0 ps,结束时间为1.0 ms,输入激励inclk0 周期为10.0 ns。单击“start simulation”按钮,即可得到输出波形。 仿真起始延迟时间为559.301 ns, 程序运行过程中无错误警告,仿真成功。 其仿真结果如图6 所示。

图6 锁相环模块仿真Fig.6 PLL module simulation

计数器模块仿真对计数器模块进行仿真,模块参数设置如下:时序仿真开始时间为0 ps,结束时间为1.0 μs,输入激励CLK 周期为10.0 ns。单击“start simulation”按钮,即可得到输出DOUT 的波形图(用十六进制表示)。 仿真起始延迟时间为13.526 ns,程序运行过程中无错误警告,仿真成功。 其仿真结果如图7 所示。

图7 计数器模块仿真Fig.7 Counter module simulation

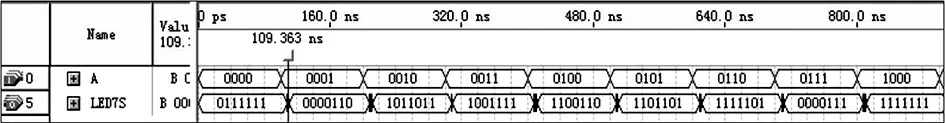

译码器模块仿真对译码器模块进行仿真,模块参数设置如下:时序仿真开始时间为0 ps,结束时间为50.0 μs,输入激励A 周期为10.0 ns。单击“start simulation”按钮,即可得到输出LED7S 的波形图(用十六进制表示)。 仿真起始延迟时间为109.363 ns,程序运行过程中无错误警告,仿真成功。 其仿真结果如图8 所示。

图8 译码器模块仿真Fig.8 Decoding module simulation

整体电路仿真整体电路仿真模块参数设置如下:时序仿真开始时间为0 ps,结束时间为1.0 ms,输入激励CLK 周期为50.0 ns,按键K8 随机选择一段时间并置为1。 单击“start simulation”按钮,即可得到输出CKK,L,LA,LED,PP 以及spk 的波形图。仿真起始延迟时间为10.175 μs,程序运行过程中无错误警告,仿真成功。 其仿真结果如图9 所示。

图9 整体电路仿真Fig.9 Overall circuit simulation

5 硬件电路测试

仿真测试后,还需要进行硬件测试以进一步验证系统性能。 引脚锁定并下载程序后方可进行硬件电路测试。 硬件电路测试有2 个输入信号, 一个是内部时钟信号,另一个是通过外部手动按压K1 按键产生的信号。 其中内部时钟信号频率为20 MHz,通过锁相环来减少时钟延时、时钟变形和片外干扰,改善时钟的建立时间和保持时间。 随着内部时钟不断输入信号,计数器持续计数,当计数器满足要求时,开发板最上面一排的LED 小灯便会依次亮起。 并且,2 个并排的数码管会显示数字, 左边的数码管显示数据高4位,右边的数码管显示数据低4 位,同时蜂鸣器也会响起。 接着,从右到左依次按动按键让最下方的数码管显示数字。 由于非门的作用,当不按动按键时小数点是亮着的;反之,小数点不亮。 PCB 板测试如图10 所示。

图10 PCB 板测试Fig.10 Test pattern of PCB board

6 结语

通过硬件测试电路原理、总体方案设计、硬件模块化设计、仿真测试以及PCB 板实测,完成了基于FPGA 的硬件测试电路的设计, 实现了设计的预期功能,仿真中的实现时间达到了ns 级别。此外,所设计操作界面简单,操作易学易用,具有良好的抗干扰性能,能够适应不同的生产环境,为顺利完成生产任务提供及时的检测、调试功能,在市场推广中备受青睐。