基于垂直互联工艺的小型化低相噪毫米波频率源设计∗

(中国船舶重工集团公司第七二三研究所 扬州 225001)

1 引言

频率源被誉为无线电系统的心脏,其性能的优劣直接影响到整机的性能。随着毫米波无线电通信、雷达、电子对抗等系统迅猛发展,对于频率合成源也提出了越来越高的要求[1]。

本文设计了一款低相噪多路输出毫米波频率源,为某毫米波测速雷达系统提供本振信号,其主要指标如下:1)四路固定频点输出:29.8GHz、30.8GHz、31.8GHz、32.8GHz;2)输出功率 ≥ 10dBm;3)杂散 ≤ -55dBc;4)输出相噪 ≤ -100dBc/Hz@1kHz(参考频率 100MHz,相噪为-155dBc/Hz@1kHz);5)尺寸为145mm×110mm×18mm。

该频率源的难点主要在于:1)低相位噪声输出;2)尺寸小通道多,射频走线存在交叉。国内现有低相噪频率源大多采用倍频器(尺寸大)或者PDRO(功耗大、电压高)来实现,且货架产品中极少有毫米波源。直接采用四个倍频器/PDRO组成多通道毫米波源,会带来体积大、功耗大、成本高、信号串扰严重等问题。因此,研制低相噪小型化的多路输出毫米波频率源产品具有很重要的工程实用价值。

2 频率源原理方案

从形成理论到发展至今,频率合成技术可以分为以下四种:直接模拟合成(DAS)、间接合成(PLL)、直接数字合成(DDS)、混合频率合成。对于本文所设计的频率源,相位噪声是非常重要的指标,以下是几种情况下相噪的计算方法[2~3]。

理想倍频器的输出相噪可表示为[4]

其中,Lout为输出信号相位噪声,Lref为输入参考信号相位噪声,N为倍频系数(反映输出信号与参考信号的恶化程度)。以32.8GHz频点为例,理论直接倍频输出时相位噪声为:L=-155+20log(32.8/0.1)≈-104dBc/Hz@1kHz。

对于理想混频器,其输出信号相位噪声为两个不相关的输入信号相噪相加[5]:

Sφ1(f)与 Sφ2(f)为混频器两个输入信号相噪,即理想混频器的输出相噪具有叠加性。

对于锁相环输出信号,在环路带宽以内的相位噪声计算如下[6~7]:

其中,L(1 Hz)为鉴相器的基底噪声,Fp为锁相环鉴相频率,N为倍频系数。受参考相噪、鉴相器基底噪声、电源纹波等影响,PLL实际输出相噪远高于倍频信号相位噪声。

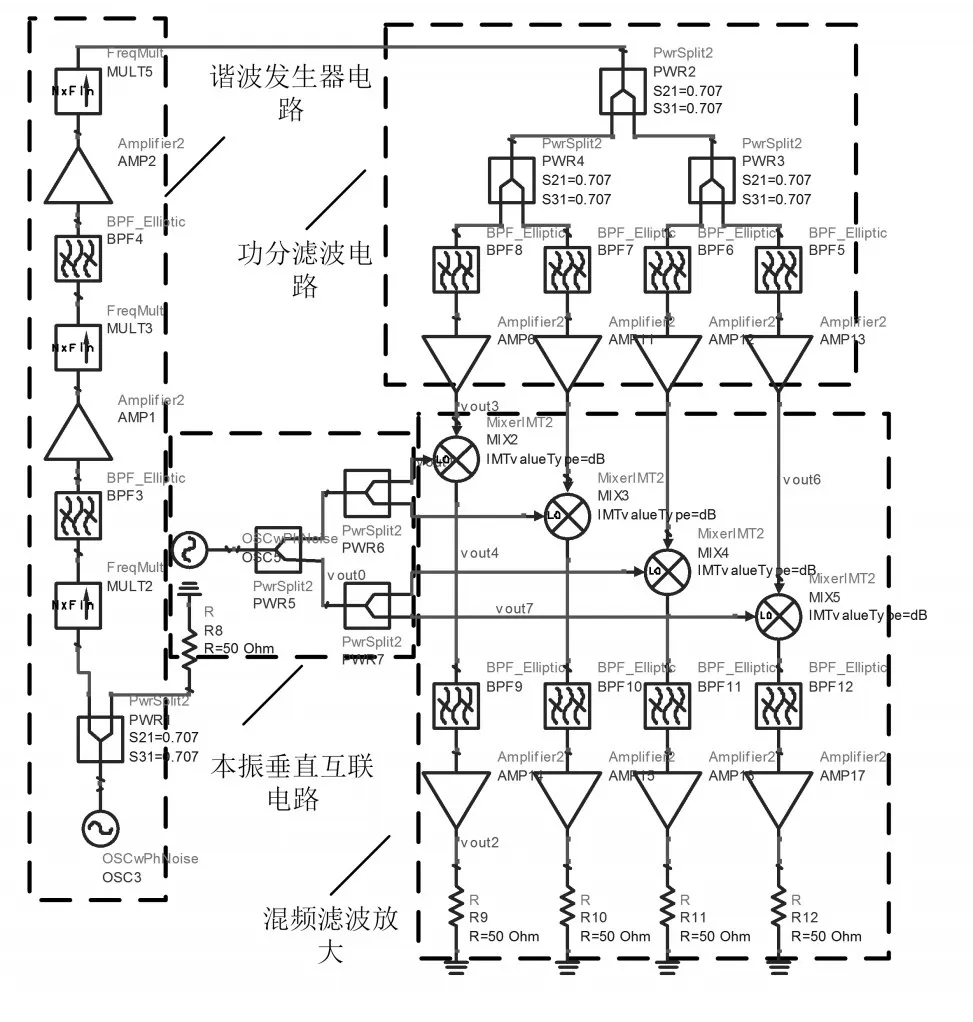

根据以上分析,直接倍频输出32.8GHz,其理论相噪与指标相比仅有4dB的余量。为满足相位噪声指标,该频率源需采用DAS或者混合频率合成技术。毫米波DAS电路包含多级倍频滤波放大电路,尺寸、功耗、体积均比较大。本文提出了一种谐波+混频的频率合成设计方案:1)中频信号由谐波发生器产生,经过功分滤波器输出四路,IF1(5GHz)、IF2(6GHz)、IF3(7GHz)、IF4(8GHz);2)本振信号LO(24.8GHz)由参考信号直接无源倍频产生,功分四路至混频器与上述四路中频信号混频;3)对混频后的四路射频信号滤波、放大处理,最终输出四路低相噪毫米波射频信号RF1(29.8GHz)、RF2(30.8GHz)、RF3(31.8GHz)、RF4(32.8GHz),其设计原理图如图1所示。

图1 毫米波频率源设计原理图

3 关键电路仿真设计与整机ADS仿真

3.1 高频垂直互联结构设计

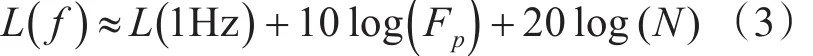

从方案设计原理图1中可以看出,对于多通道混频电路来说,必定面临着射频走线交叉的问题。为保证传输性能,在电路设计时,可以采用图2所示垂直互联的方式:将中频部分电路、毫米波混频部分电路布置在微波壳体顶层,本振电路布置在底层,在各通道混频器附近通过垂直互联结构将本振信号传输至壳体顶层,既可避免射频走线交叉,又能减小本振泄露的影响。

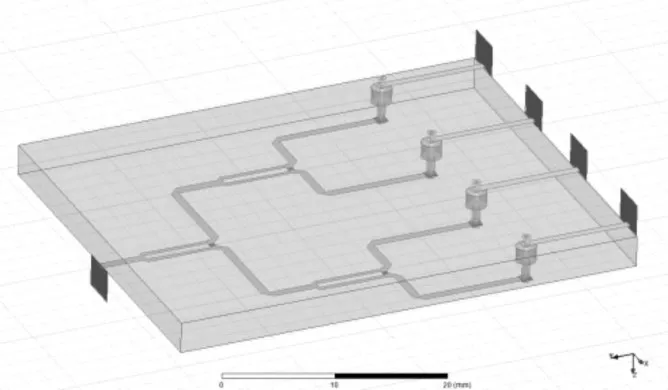

图2 垂直互联结构模型

图2 所示的垂直互联结构,为微带-同轴-微带的过渡形式。图中圆圈范围内,同轴内导体延伸部分及微带末端会引入寄生电感,在传输TEM模的同轴传输线与准TEM的微带线间,不可避免地引入阻抗不连续[8~9]。随着频率的增加,这一不连续性会导致较大的插损与回波损耗,严重限制了该过渡结构在Ku以上波段的应用。

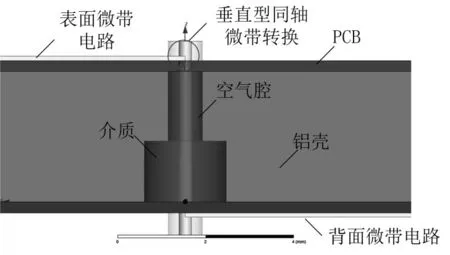

无损耗传输线的等效模型如图3所示,利用基尔霍夫电压和电流定律得到以下两式:

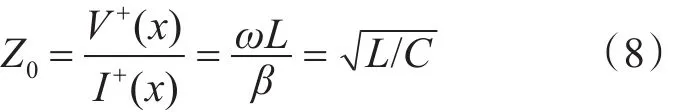

传输线特征阻抗Z0计算可表示为[10]

图3 无损传输线等效模型

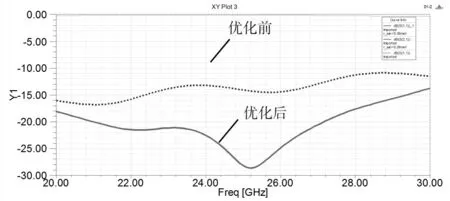

由式(8)可知,无损传输线特征阻抗的平方正比于单位长度的等效电感与等效电容之比。同轴线与微带线等效参数如表1所示。为减小寄生电感带来不连续性,可以通过增加等效电容,即改变同轴空气腔的直径与微带末端传输线尺寸来实现[11~12]。

表1 无损传输线的参数

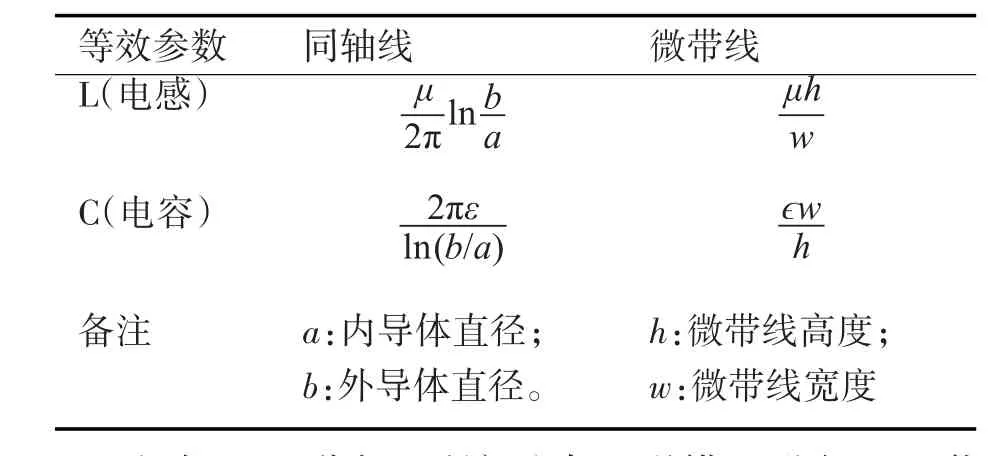

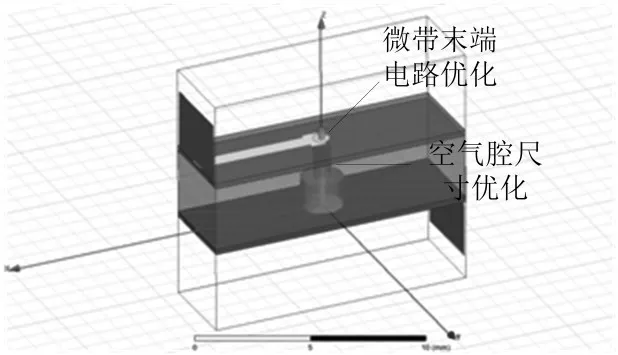

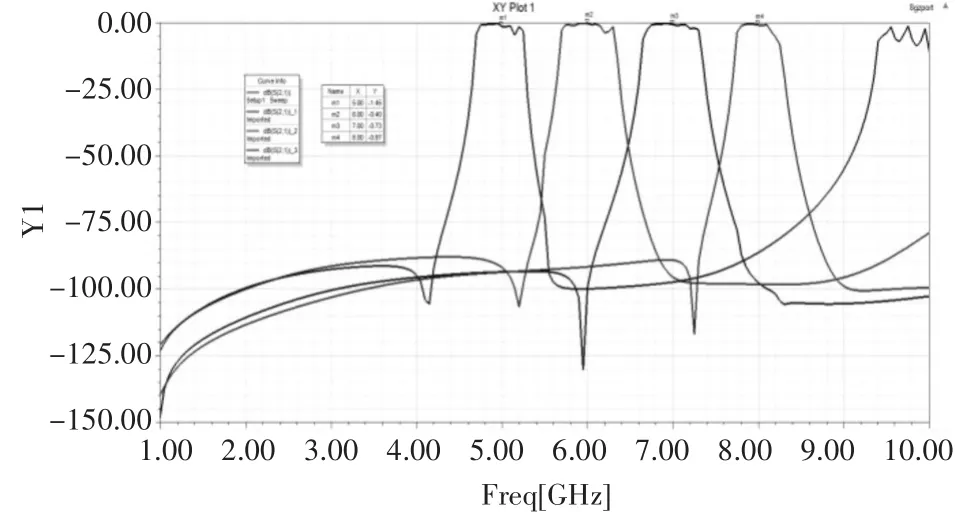

根据以上分析,对该垂直互联模型进行匹配优化,其仿真模型如图4所示,仿真优化结果如图5所示。图5中虚线为优化前过渡结构回波损耗,实线为优化后过渡结构回波损耗与插损。优化后的过渡结构回波损耗得到明显改善,尤其是工作频点附近,从原来的-15dB降低到了-27dB,插损也降低至0.3dB。

图4 优化后垂直互联电路HFSS模型

图5 优化与未优化垂直互联结构回波损耗对比

3.2 垂直互联与毫米波功分器联合仿真

本振信号功分四路后,经垂直互联结构传输至混频单元。该功分器对于回波损耗、通道隔离度的指标要求很高:垂直互联结构对驻波很敏感,功分器的回波损耗会严重影响互联信号的插损;通道间信号频率相近,经混频器泄露的信号会通过功分器串入相邻通道,引入难以滤除的杂散。将传统威尔金森功分器优化后,与互联结构联合仿真,仿真电路与结果如图6、图7所示。

从图7可以看出,该结构的插损约7.3dB,通道间隔离度最差约-35dB,满足使用要求(本振驱动放大器反向隔离度-30dB)。

图6 联合仿真电路模型

图7 电路HFSS仿真结果

3.3 高抑制度滤波器的设计

中频电路部分为链路提供四路中频信号,其频率分别为 5GHz、6GHz、7GHz、8GHz。四路信号均由谐波发生器生成,经过功分、滤波后输出。中频信号滤波器组使用发夹线滤波器结构,其结构简单、指标性能好且工程上易实现,仿真模型如图8所示。

仿真结果如图9所示,可以看出,滤波器带内插损 ≤1.4dB,带外抑制(距中心点 ≥1GHz)>75dBc,满足本文设计要求。

图8 带通滤波器仿真模型

图9 低通滤波器仿真结果

3.4 射频链路仿真

根据图1所示原理图,在ADS中设计了射频链路仿真电路,如图10所示。放大器、倍频器设置为理想器件,混频器与滤波器输入仿真数据或者厂商手册中的数据。

图10 射频链路仿真电路图

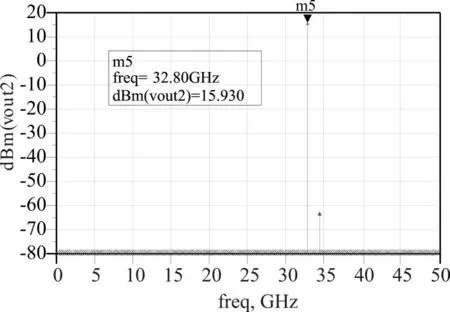

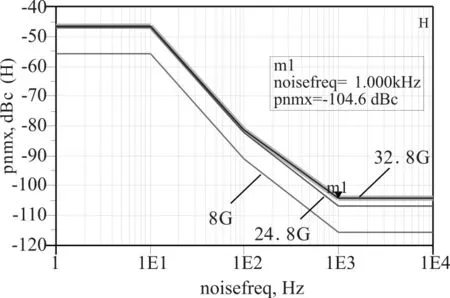

图11 与图12给出了最高频点的仿真结果。从图11中可以看出输出功率达到15.9dBm,杂散<-75dBc,实测结果会因为器件非理想性有所恶化。图12为相位噪声仿真图,从上至下三条线分别为32.8GHz、24.8GHz、8GHz对应相噪,可以看出最高频点32.8GHz的输出相位噪声约-104.6dBc/Hz@1kHz,满足使用要求。

图11 32.8GHz杂散与功率

图12 32.8GHz相位噪声

4 实物制作与测试

4.1 实物加工

本组件采用微组装工艺加工电路,整个电路射频部分制作在RO 5880的软基片上,并采用裸芯片键合等工艺来实现微波信号的处理与传输。滤波器、功分器等采用同样厚度同样型号的PCB基板,可直接集成在微带电路中。

将设计好的频率源进行电路和腔体的加工,组装完成后的实物图如图13所示,实物尺寸为145mm×110mm×18mm。

图13 频率源实物图

4.2 测试数据

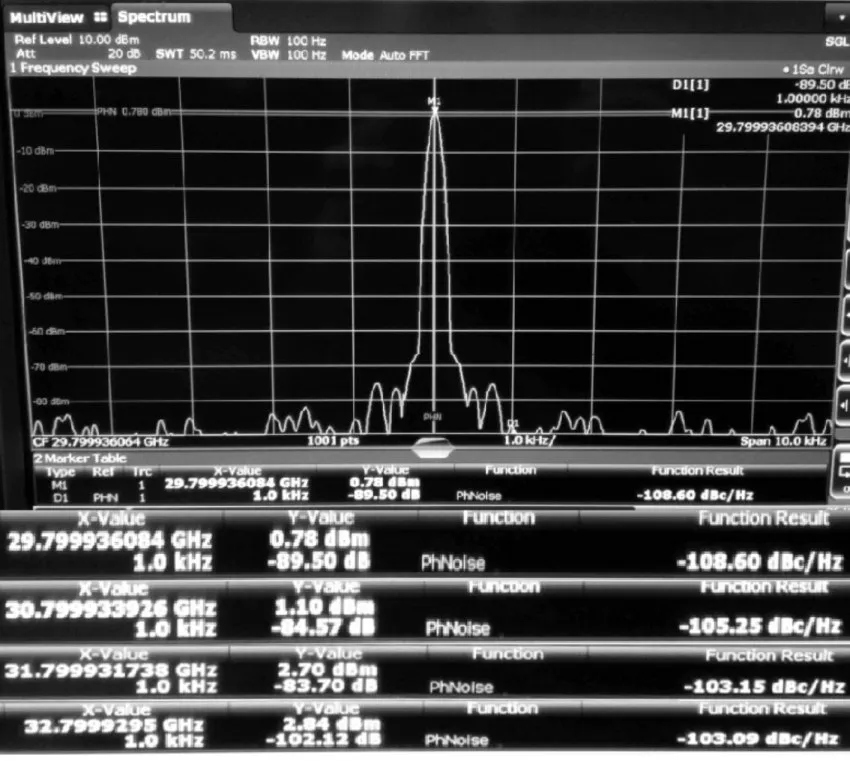

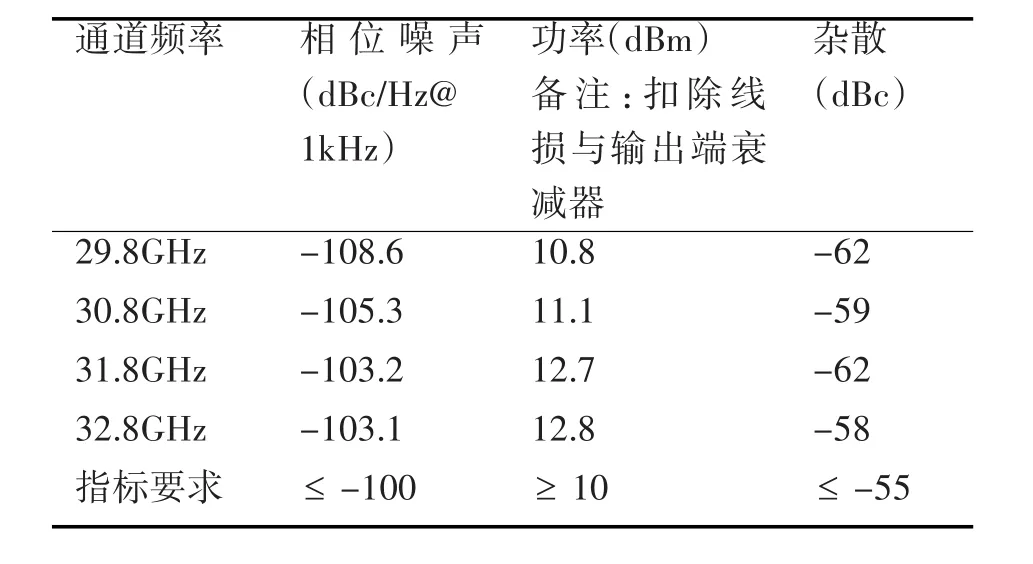

图14 与表2所示为该频率源的实测结果。常温下该组件正常工作电压、电流值为+6V/1.6A。四个频点的相位噪声最差为-103.1 dBc/Hz@1kHz,功率 ≥10dBm,杂散均能满足-55dBc的要求。

图14 频率源相位噪声测试结果

从表2可以看出,四个通道相位噪声最差为-103.1dBc/Hz@1kHz,与仿真计算相比,指标几乎没有恶化;输出功率均 ≥10dBm,杂散抑制最差点为-58dBc,满足指标要求,充分说明了本组件电路设计的合理性。

表2 测试结果及指标对比

5 结语

本文提出了一种毫米波频段低相噪小型化频率源的设计方案,该方案利用谐波发生器产生多路中频信号,与倍频信号混频,得到多路低相位噪声毫米波信号。在组件设计过程中,利用HFSS三维电磁仿真软件设计了组件中使用的滤波器、功分器等无源器件;利用绝缘子垂直对穿电路,避免了射频电路的交叉。从实测结果可以看出,该频率合成组件具有相噪低、尺寸小、功耗低等优点,能很好地满足实际工程应用需求。