基于FPGA的暂态信号可定制精细化实时时频关联分析算法

林伟

基于FPGA的暂态信号可定制精细化实时时频关联分析算法

林伟

(自由职业者,山东省 济南市 250100)

针对电力系统故障信号中暂态分量的精细化实时分析需求,提出一种不同于Mallat算法频域分段方式的时频关联分析算法。这一算法可以实时运行,既对频带进行了精细化的、可灵活设置的、有重点的划分,又实现了全频带的高时域分辨率,同时保持了输出数据的时频关联特性。基于现场可编程门阵列(field-programmable gate array,FPGA)设计了一个实现这一算法的范例模块,基于MATLAB建立了一个简化的分布式参数电网模型。在这一模型上以生成500kHz的故障信号采样值序列作为输入范例模块的数据流,对范例模块进行仿真,初步验证了该算法的性能、实用性。就该算法在继电保护算法设计中的应用策略提出了建议,对该算法涉及的其他后续工作进行了展望。

继电保护;暂态量保护;小波变换;时频关联分析;现场可编程门阵列(FPGA)

0 引言

电力系统故障信号的高频暂态分量非常丰富,有可能隐藏着大量信息,已有多个团队就暂态信号的采集与分析进行了研究并取得了重要成果[1-4]。对暂态信号进行精细化的实时时频关联分析,有可能发现新的、可以提高“四性”的保护特征量,进而有可能研发出性能更先进的基于暂态信号实时分析的新型保护装置[5]。

小波变换是当前对电力系统暂态量故障信号进行实时时频关联分析最重要的数学工具之一,Mallat算法是小波变换得以实用化的基本手段。Mallat算法的基本特征决定了其固有的缺陷:对(0,s/2)(s为采样频率)频带的划分方式是比较粗略的,对高频区域无法细分,只有在分解层数增加的情况下,才能对最低频区域进行比较精细的划分,但代价却是时域分辨率的指数级下降[5]。同时,对于位于特定频段的、不需测量的、必将导致干扰的原始信号分量,也无法排除其影响。

现场可编程门阵列(field-programmable gate array,FPGA)是20世纪80年代出现的一类可编程逻辑器件,内置大量可并行运行的逻辑门、寄存器、运算单元、存储区块,以及为其提供可编程互联的布线资源,相较于当前暂态量保护装置的核心运算器件DSP、CPU,其最大优势是多通道、大运算量的高速并行运算[6]。以FPGA为核心实现暂态信号分析算法,能够以硬件资源换性能、将大量高速运算任务分配给几百上千个运算核心并行执行,为大幅度改善信号分析模块的性能提供了技术基础,为暂态量保护技术的发展提供了重要的机遇。

基于FPGA实现保护算法,此前已有部分研究成果[7-11],其中文献[8]述及了基于FPGA实现小波变换的思想。

本文以FPGA的并行运算能力为基础,借鉴小波变换Mallat算法的频域分段、时频关联思想,提出不同于Mallat算法频域分段方式的暂态信号可定制精细化实时时频关联分析算法,以期为暂态信号的时频关联分析提供更好的数据预处理工具,为暂态量保护中新特征量的发现、新特征量提取算法的研究提供新的基础、新的思路。

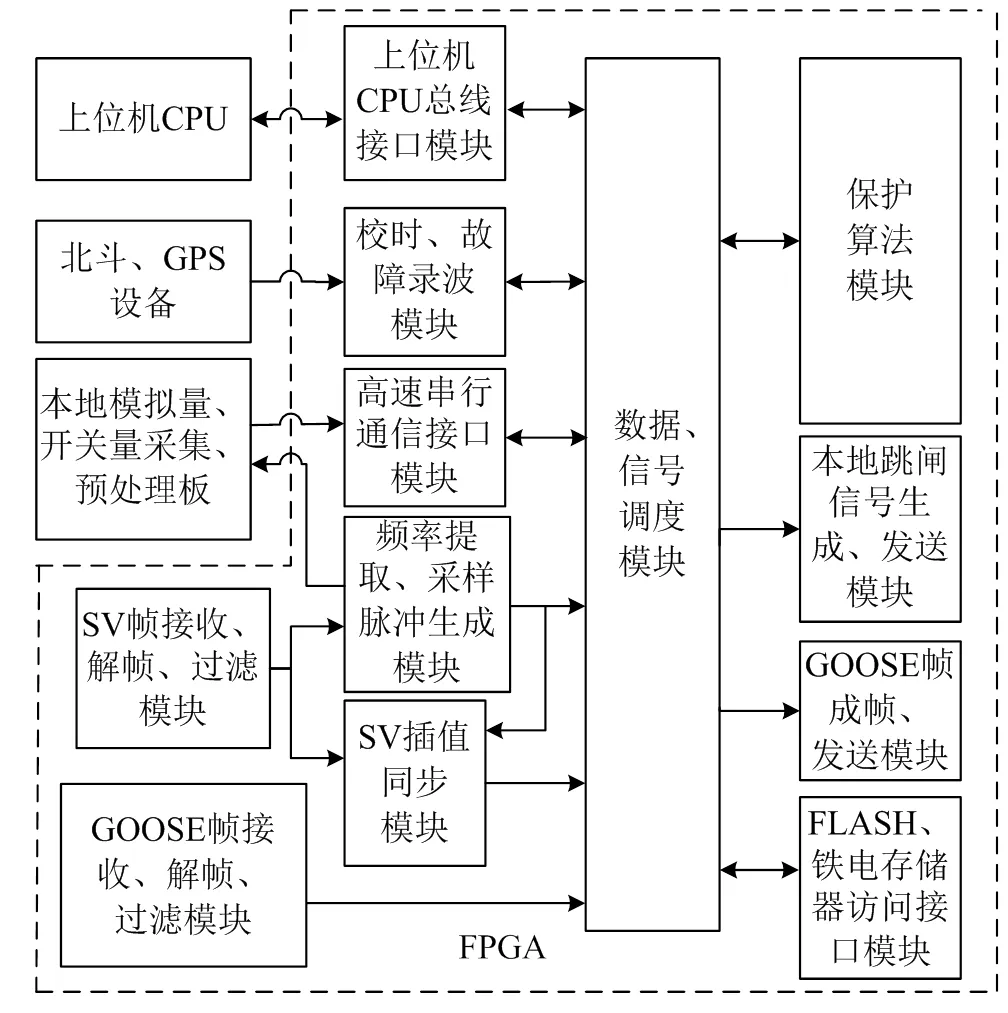

1 基于FPGA实现继电保护装置的系统架构

基于FPGA实现继电保护装置的系统架构如图1所示。其中包含了智能变电站过程层设备的通讯接口模块、数据预处理模块。虚线框内是在主FPGA芯片中实现的功能。

图1 基于FPGA实现继电保护装置的系统架构图

图1中各模块分别占用FPGA中的一部分硬件资源,在上位机CPU的配置下各司其职、互相协作、并行运行。近年来研究人员已经在智能变电站二次设备的通信接口、数据预处理环节中用FPGA实现了其中的一些模块[9-11],本文不再赘述。

本架构着眼于构建继电保护装置中具有共性的功能框架,把位于主数据通道上的、实时处理采样值数据流的各算法模块整合到FPGA芯片中,FPGA片内数据处理过程的特征是分布式运算、基于流水线协作的并行处理,核心理念是“以硬件资源换性能”。

与此同时,由上位机CPU实现系统初始化、人机界面、保护定值获取及下发等慢速、非实时功能,以节省FPGA硬件资源、简化系统架构、管控开发难度。

2 暂态信号可定制精细化实时时频关联分析算法

2.1 算法在继电保护装置算法流程中的位置及任务

暂态信号可定制精细化实时时频关联分析算法是图1中“保护算法模块”中执行特征量提取任务的子模块的下级子模块,对暂态信号采样值序列进行预处理,实时输出包含时频关联信息的暂态信号信息流,实时为提取故障信号特征量的子模块提供基础数据:与时域坐标精确关联的精细化全频段信号频谱。

2.2 算法结构

暂态信号可定制精细化实时时频关联分析算法的结构非常简单,就是几十个(视市场竞争情况可以多至几百个)并行运行、同时处理同一暂态信号采样值序列的高阶FIR带通数字滤波器,每个滤波器负责将暂态信号处于某一频段内的频率成分实时过滤出来,发往后续的子模块。在最简单的情况下,各个滤波器的通带范围前后衔接,各通带连在一起,覆盖整个(0,s/2)频带。

2.3 设计实例

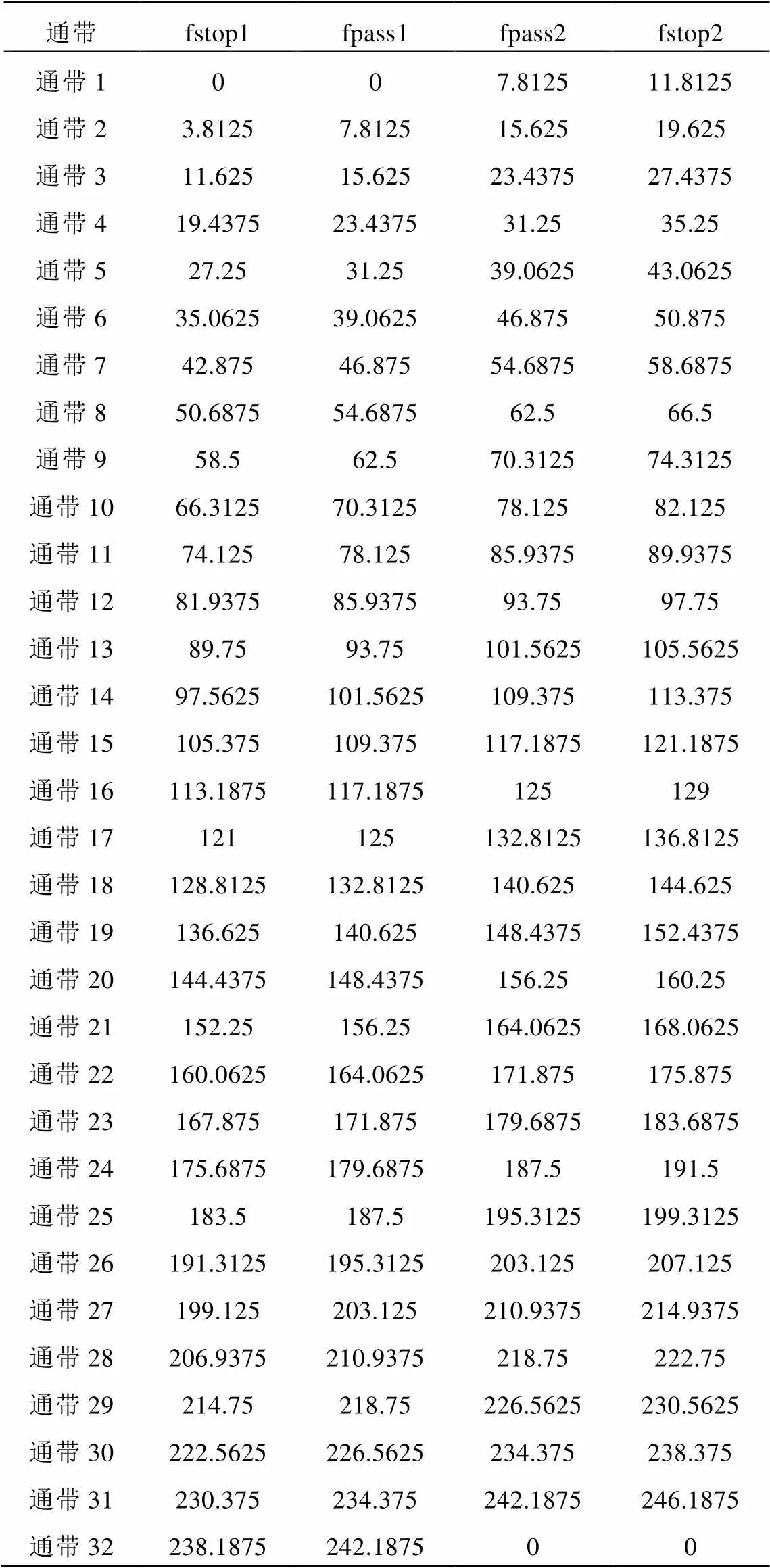

作为对暂态信号可定制精细化实时时频关联分析算法的验证,用MATLAB写了一个算法模块,用于离线处理采样频率s=500 kHz的采样值序列。该算法模块中包含了32个互相独立的FIR带通滤波器,各滤波器在fdatool界面下用等纹波法设计,通带带宽相同,为500kHz/2/32=7.8125kHz,前后衔接覆盖了整个(0,s/2)频带,过渡带宽度为4kHz,通带纹波约为1dB,阻带衰减约为45dB,系数精度取16位,所设计得到的滤波器阶数为212阶。

各滤波器的通带边界参数如表1所示。作为例子,其中第10个滤波器(中心频率74.21875kHz)的fdatool设计页面如图2所示。

表1 各滤波器的通带边界参数

图2 第10个滤波器的fdatool设计页面

本设计实例运行时,各FIR带通滤波器同时接收同一暂态信号采样值序列,输出暂态信号中分别位于32个频段内的各路频率成分,以供后续的特征量提取算法子模块使用。

2.4 算法结构的可定制特性

由于各带通滤波器的运行互不干涉,所以各通带的带宽、各通带在(0,s/2)频带中的位置是可以自由设置的(包括互相包含、部分重合、前后分离等各种方案,2.3节中的例子属于特例),以适应各种运行环境下的故障信号特征。

例如,在某种特定的电网结构下,如果故障仿真、对现场故障录波数据的研究表明某个频段的信号需要特别予以关注,则可以增加在此频段内划分出的通带数量(增加带通滤波器的数量),用更多的硬件资源实现对关键频段的更精细观察(即前述“以硬件资源换性能”);反之,如果故障仿真、现场故障录波数据研究表明不需要关注某个频段的信号,则完全可以在设计带通滤波器时使通带避开这一频段,以排除此频段内的信号对有用频段内信号的干扰,同时节省硬件资源。

也就是说,暂态信号可定制精细化实时时频关联分析算法中的待分析频段的设置、划分是完全可定制的。

具体的通带设置方案,需要依据保护装置所需处理的故障信号的特征来确定。

2.5 与小波包变换的效果对比

部分文献中将小波变换的Mallat算法直接应用于小波包变换,方法是:借助对上级Mallat分解得到的高频分量进行下采样、继续分解,对高频分量进行与低频分量相同的级联分解操作,以此实现对高频分量的继续细分,直至达到所需要的频域分段精度。

与暂态信号可定制精细化实时时频关联分析算法相比,小波包变换Mallat算法的差距主要在频段设置、划分方式上:后者的划分方式固定,每个通带的带宽只能以s/2/2(=1,2,3,...)为单位,且在整个频带中的位置固定[12-13],如果待分析频段与邻近的干扰频段都位于一个最小频段单位内,将无法对干扰频段加以滤除;与此同时,如2.4节所述,前者的划分方式则是完全可定制的。在上述情况下,可以通过自由移动待分析频段在频谱中的位置而“躲开”干扰频段。

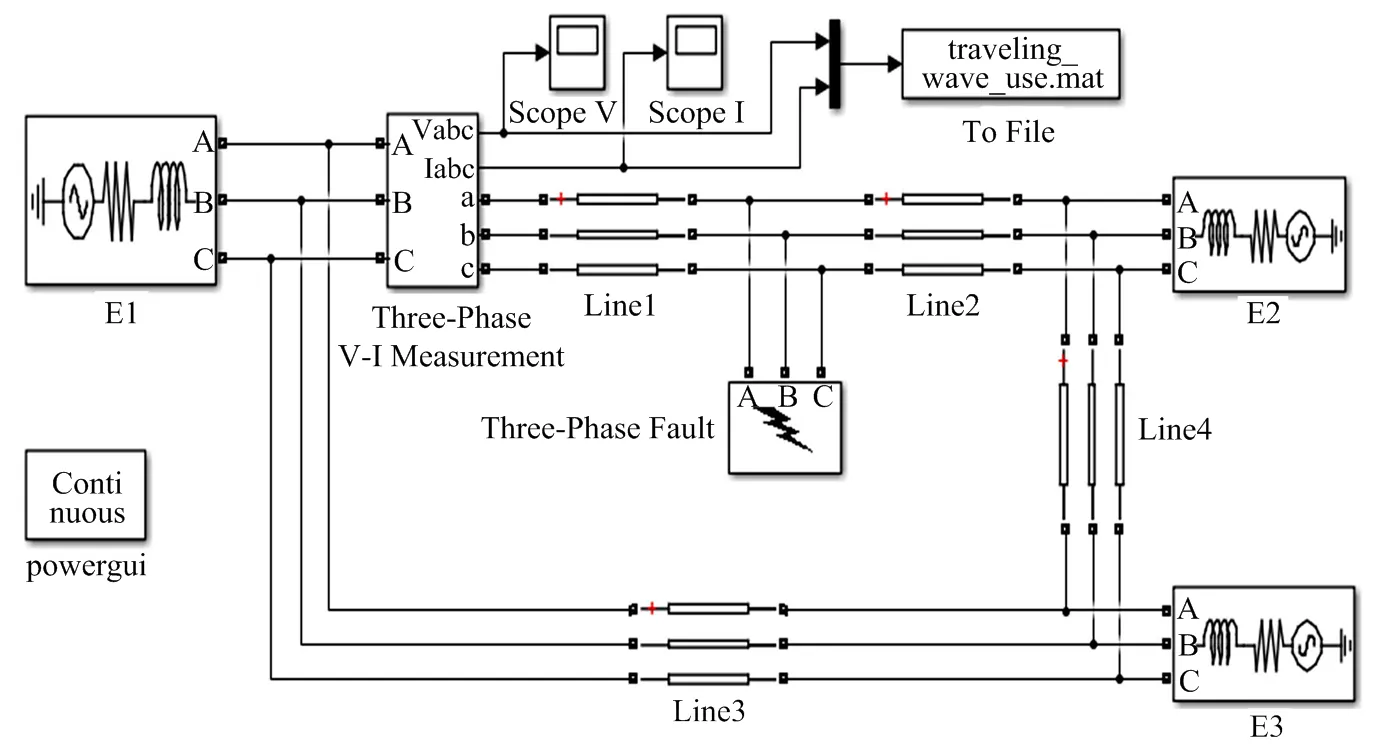

3 基于Simulink建模的仿真验证

为验证暂态信号可定制精细化实时时频关联分析算法处理数据的效果,利用MATLAB- Simulink工具搭建了一个简单的分布参数电网模型,针对一种典型故障情况进行了仿真,将仿真得到的2路暂态量故障信号采样值序列作为待处理数据,在MATLAB环境下输往2.3节所述算法设计实例的数据入口,对其数据处理过程进行了仿真。

3.1 仿真模型的搭建

笔者用Simulink搭建了一个与参考文献[14]中图7—38所举例子几乎完全相同的分布参数电网模型,区别仅在于将故障改为A相单相瞬时接地故障、将故障点的位置移到了距离E2电源1km处,模型架构如图3所示,数据采样频率为500kHz。然后编写MATLAB代码,将2.3节所述32个带通滤波器的系数向量(归算为16位整数、与后续基于FPGA设计的范例模块采用的系数位宽相同)代入filter函数、形成32个带通滤波器,用于处理仿真生成的故障波形数据。

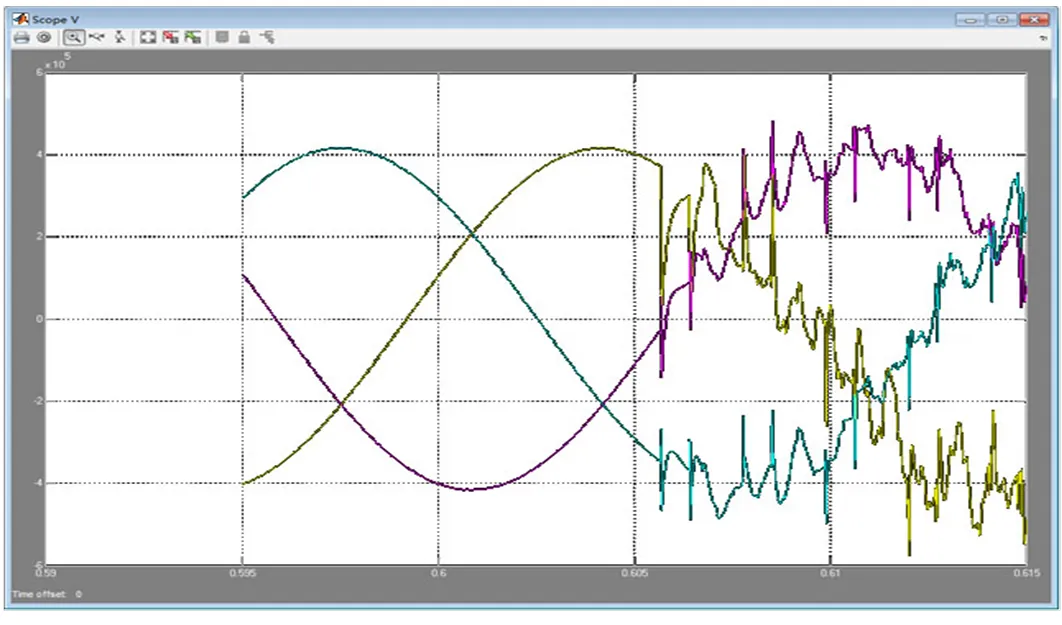

仿真得到的单相接地故障前后的三相电压波形如图4所示。

图3 仿真用分布参数电网模型架构图

图4 仿真得到的A相瞬时接地故障前后的三相电压波形图

3.2 对算法模块功能的仿真

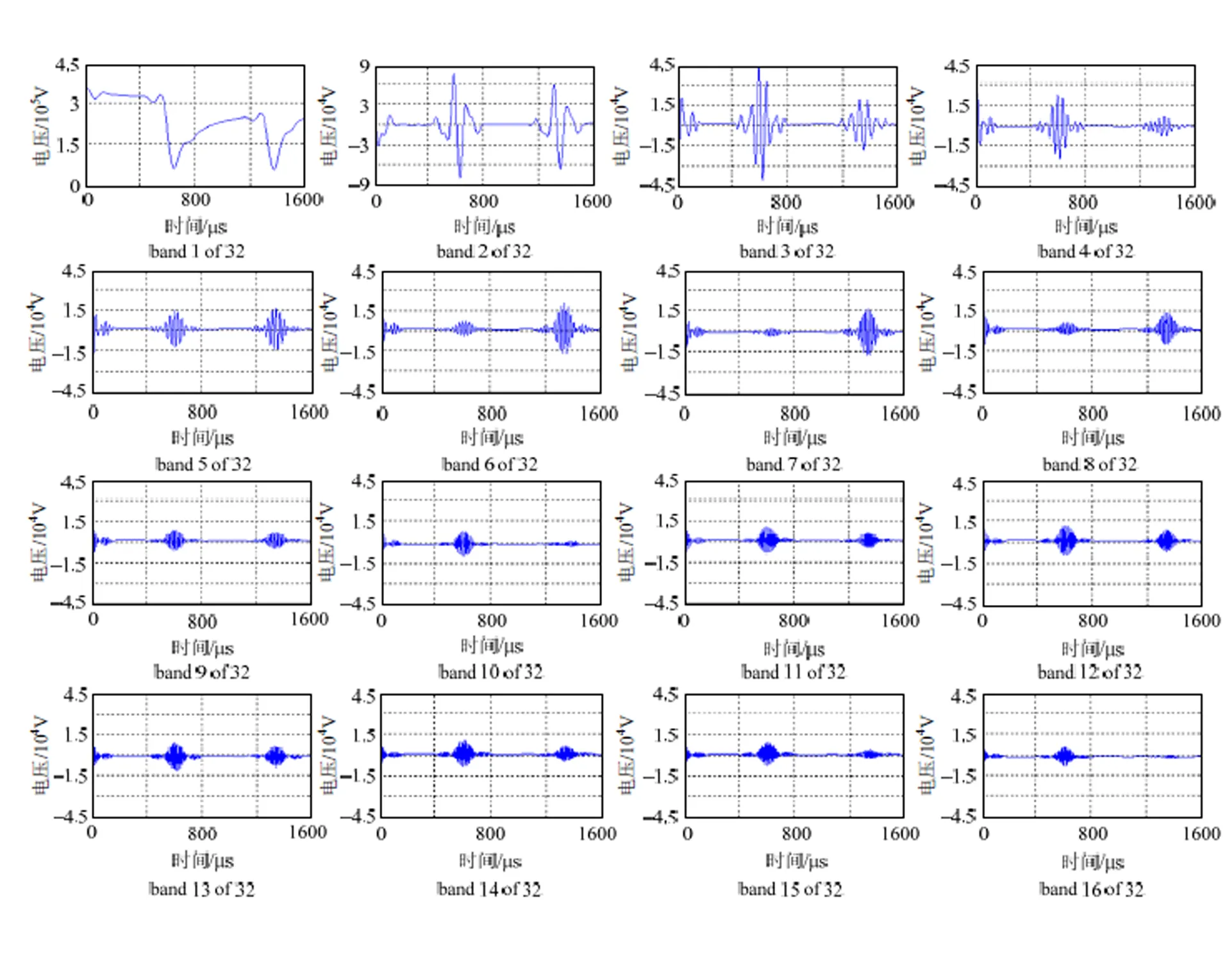

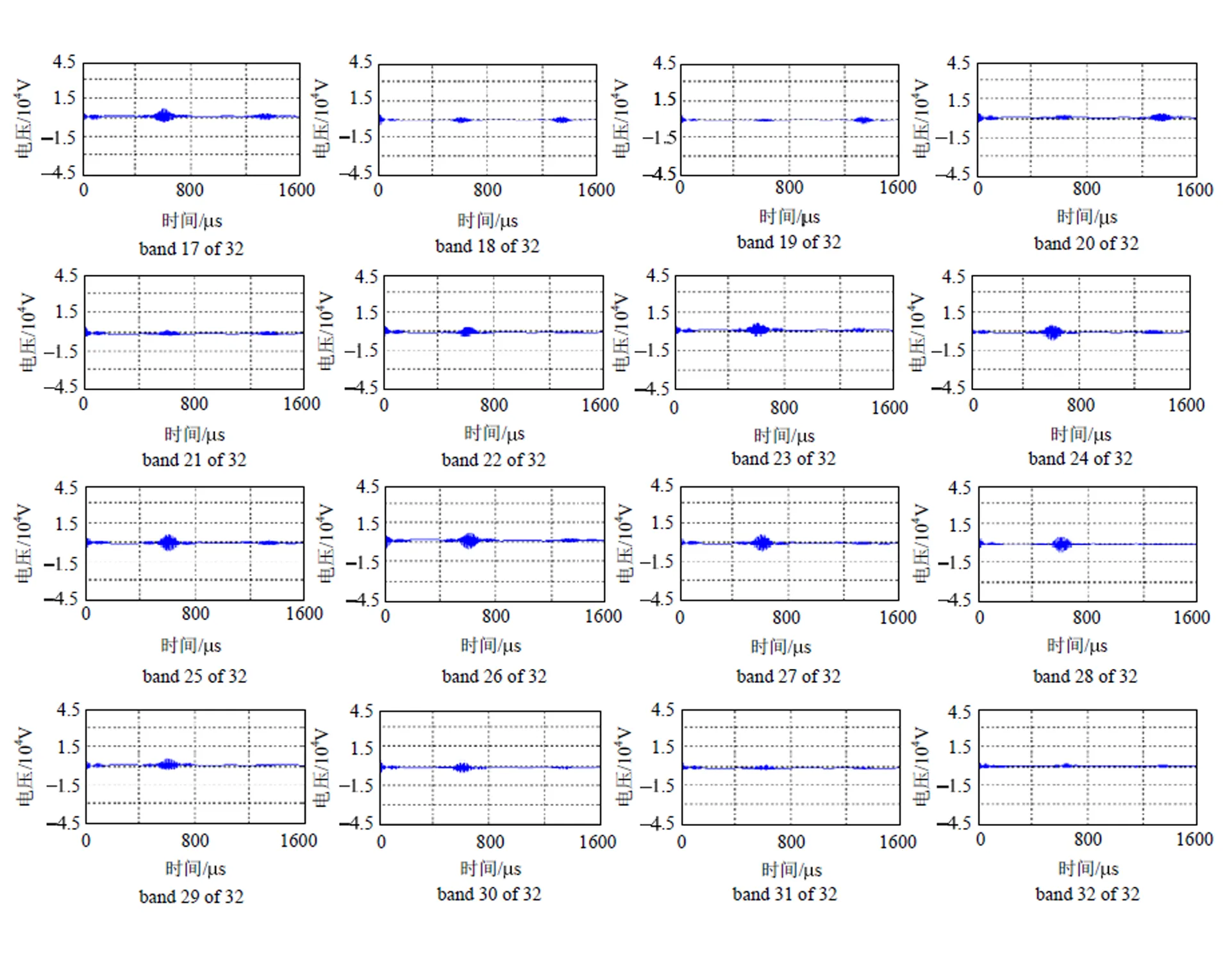

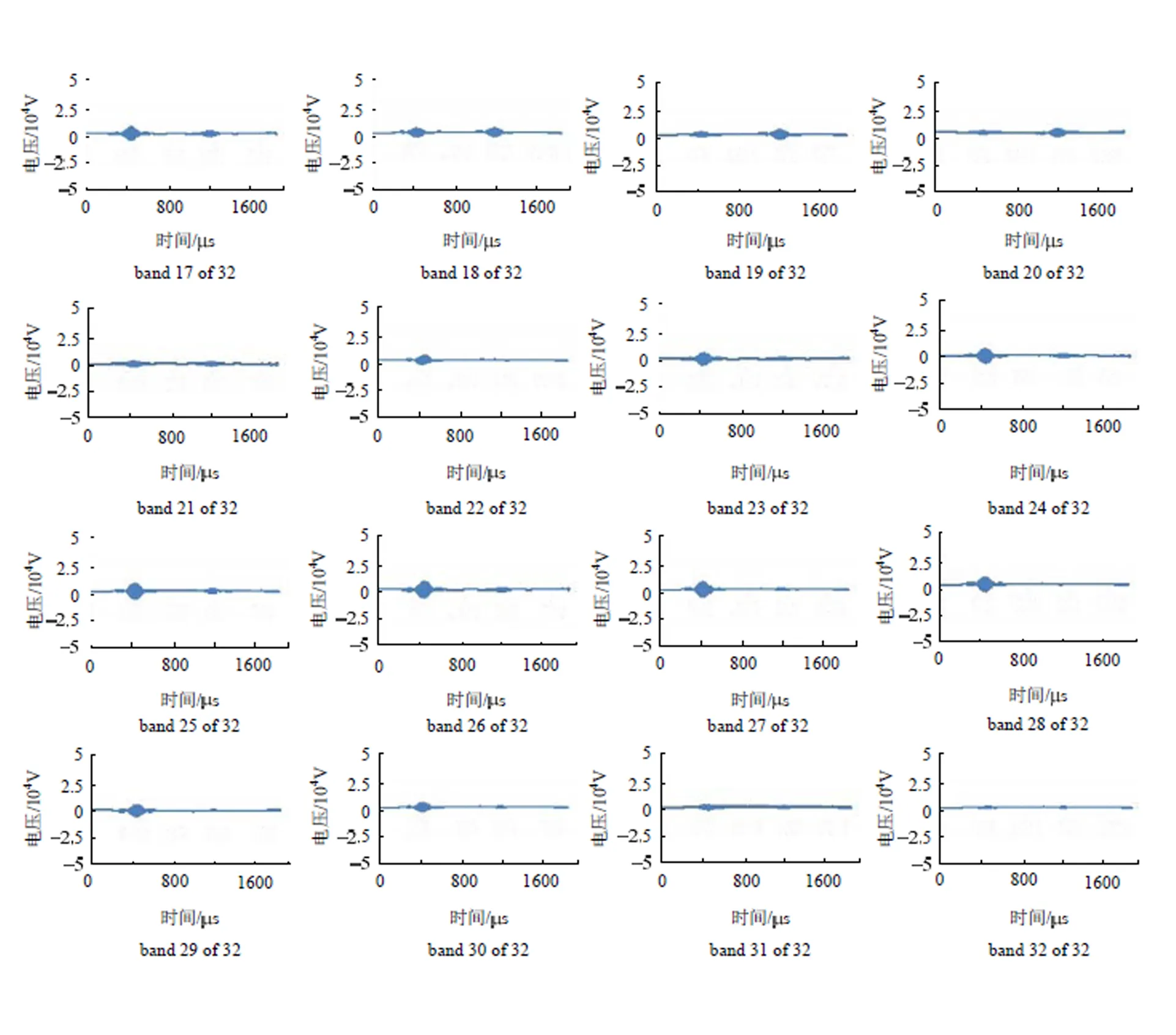

将故障前后的A相电压采样数据提取出来,送入2.3节算法模块的数据输入端,分别打印32个滤波器对应于A相数据的输出信号波形(即A相电压在故障时刻前后的波形数据被算法设计实例处理后得到的第1~32个频带的数据时序波形)如图5、图6所示。

3.3 对仿真结果的说明

图5、图6中突变点区域的波形之所以看上去不如多级Mallat分解提取到的小波系数波形那样“集中”,原因在于这里输出的是在时域上未经“压缩”的信号,这正是暂态信号可定制精细化实时时频关联分析算法在时域上的高分辨率特征的体现(这里提供的是Mallat算法无法提供的所有各频段的时域细节)。

图5、图6中突变点区域的波形之所以看上去不如DB5小波单级Mallat分解提取到的小波系数波形那样“模极大值突出”,原因在于DB5小波Mallat算法高通滤波器的通带几乎覆盖了整个(0,s/2)频段,累加了远为宽广的频带范围内的能量。这种“累加”,可以把更多频率范围内的模极大值重叠在一起,使其更突出。

但是,从另一个角度看,这也是一种“混杂”,使后续模块无法看到暂态信号在各频段内的分量在故障点处的模极大值之间的数量、位置关系等各种关系。也就是说,Mallat算法无法区分暂态信号在各细分频段内的时域特征。这一区别正是暂态信号可定制精细化实时时频关联分析算法在频域上的高分辨率特征的体现。

3.4 算法与小波分析的关系

综合上述算法分析以及2.4节的分析可知,从算法执行的结果来看,暂态信号可定制精细化实时时频关联分析算法可以被看做小波分析算法在频率维度上的精细化、可定制化发展,在时间维度上的精细化发展。

图5 第1~16个频带的数据时序波形图(MATLAB设计实例的仿真输出数据流)

图6 第17~32个频带的数据时序波形图(MATLAB设计实例的仿真输出数据流)

4 基于FPGA的范例模块设计及仿真验证

上述算法设计实例用到了几十个运行在500kHz的高阶带通数字滤波器,必将对执行保护核心算法的芯片的运算能力提出极高的要求。

为验证算法设计实例的可实现性,笔者基于FPGA设计了一个滤波器性能参数与上述算法设计实例相同、各滤波器并行运行、同时处理2通道数据的范例模块,在ISim仿真环境下同时读取上述2路暂态量故障信号采样值序列,对其功能进行了仿真验证,对其输出延迟、运算速度、芯片资源占用情况进行了验证。

4.1 FPGA范例模块的设计

在2.3节的例子述及的32个FIR带通滤波器由Xilinx公司的集成开发软件ISE 14.5,利用FPGA芯片提供的可配置的基础DSP硬核、片内RAM块、逻辑资源、连线资源生成,需调用其提供的用于生成FIR滤波器的IP核[15]。

由于需要处理2路采样值,所以调用IP时设置FIR输入的运算数据通道数为2;由于设计的原始数据采样频率为500kHz,所以调用IP时设置的输入数据速率为500kHz。滤波系数位宽为16,输入、输出数据位宽分别为32、48。驱动整个模块运行的时钟主频为200MHz。

4.2 对FPGA范例模块功能的仿真验证

仿真工具采用ISE集成开发环境中提供的ISim仿真器。编写简单的测试模块,调取3.1节得到的故障前后A相电压、电流采样数据加载到本模块的数据输入端口,从外部向本模块提供时钟信号、运算启动信号,以模拟实际装置中外部环境对本模块施加的基本驱动信号。仿真过程中,调用仿真器支持的系统函数对所关注的信号进行打印,将打印结果整理后贴到excel中,由excel绘制其波形。

在仿真模式下模块的工作过程:收到运算启动信号后,带通滤波器1、子模块1依次读取2块待处理数据存储区(仿真模式下用于存储3.1节得到的故障前后A相电压、电流采样数据,实际运行时由位于图1中的左下角的SV接收、预处理模块以数据流的形式实时提供)中存储的第1个数据,每次读出的存储区(=1、2)的数据同时送入32个处理通道(滤波器)的数据输入口,然后是各存储区的第2个数据、第3个数据......。各通道的滤波后数据流(实时的精细化频谱数据)在一定延迟(与滤波器阶数有关)后出现在滤波器的数据输出端口,供后续模块使用。

4.3 仿真结果

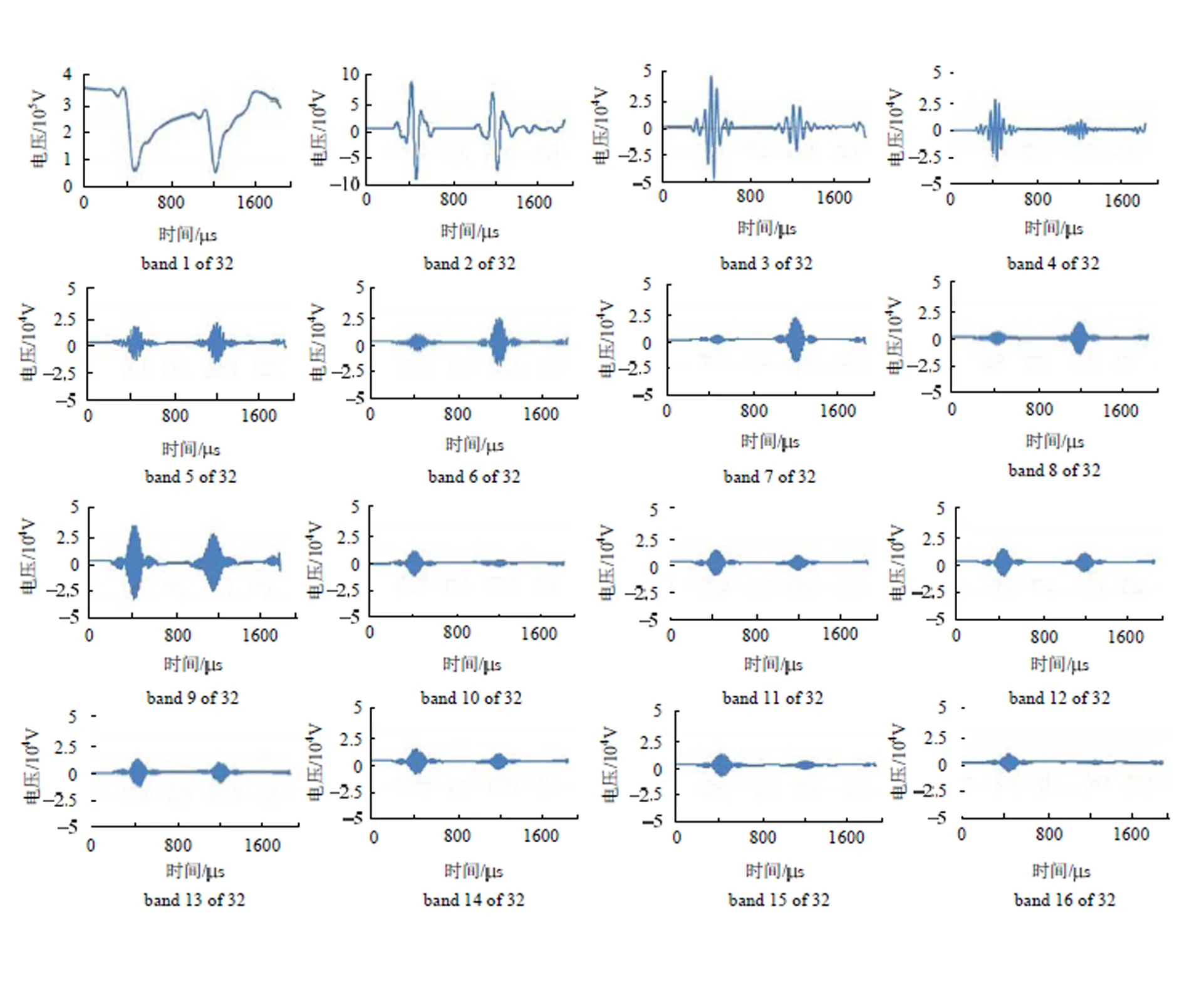

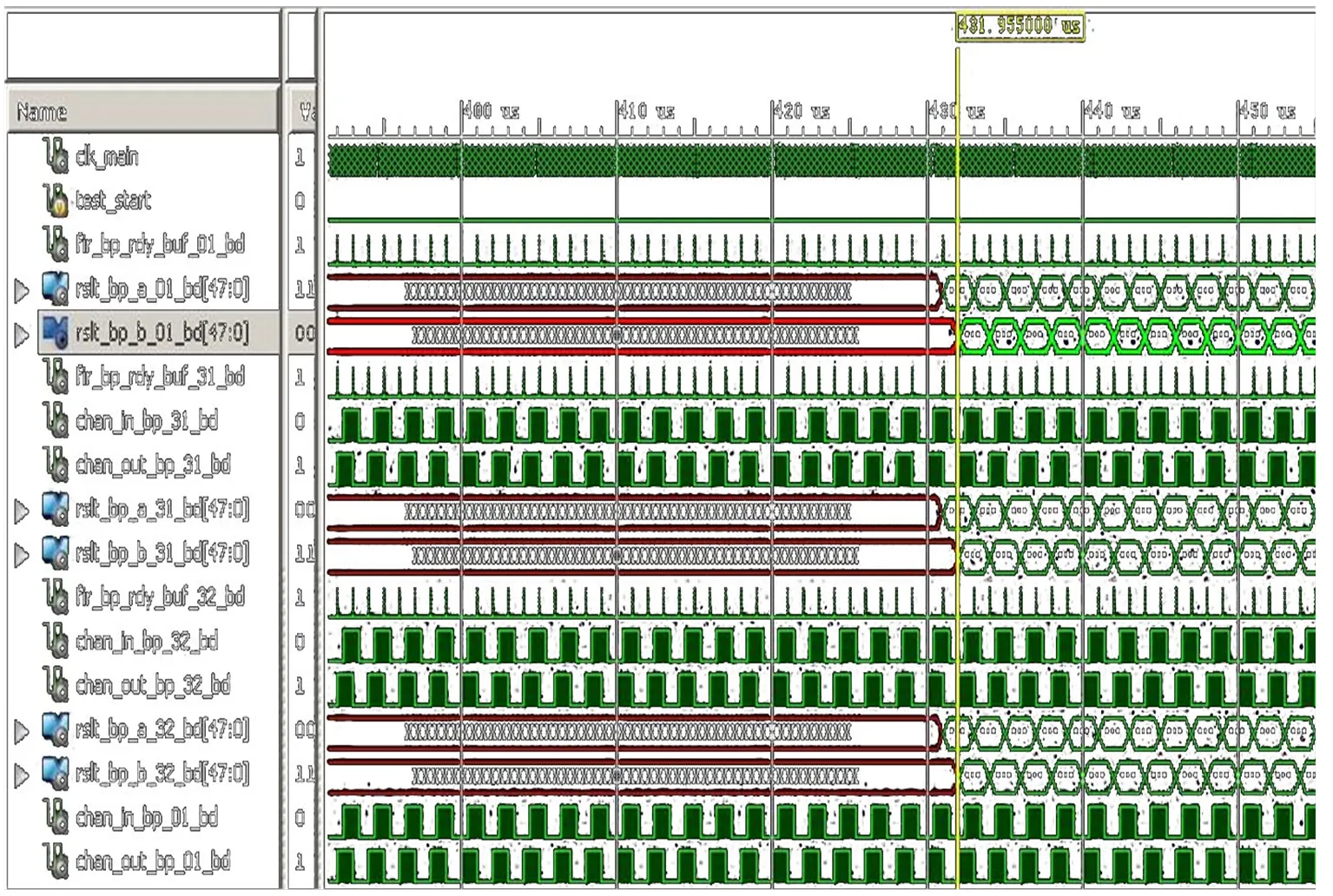

32个带通滤波器的输出信号波形如图7、图8所示。对比图5、图6可知,这一基于FPGA的范例模块完全实现了2.3节所述基于MATLAB的设计实例的算法功能。

4.4 模块的输出延迟、运算速度、芯片资源占用情况

如图9所示,从启动仿真、输入第一个电压采样值开始,第2路采样值滤波的第1个有效数据输出时刻是第432ms。考虑到FIR带通滤波器突出的是位于数据窗中部的输入数据,可以认为,从输入数据发生突变到反映到输出的频段分量(即带通滤波器的输出)的延迟不大于220ms。

在ISE开发环境下对本模块进行综合、布局、布线,在采用Xilinx的中等性能产品系列中速度最慢、运算资源最少的芯片xc7k70t-1fbg676的情况下,最终得到的结果是可以运行在200MHz以上,满足4.1节中调用IP时的要求。片内主要硬件资源的占用比例:Slice Registers,15%;Slice LUTs,17%;occupied Slices,30%;RAM块,48%;DSP硬核,40%。

图7 第1~16个频带的数据时序波形图(FPGA范例模块的仿真输出数据流)

图8 第17~32个频带的数据时序波形图(FPGA范例模块的仿真输出数据流)

图9 FPGA范例模块仿真波形截图

必须指出的是,本文所做工作的目的在于验证可行性、性能优势,而非寻找最优解。具体应用时需要针对实际需求设计FPGA实现方案。

5 算法在继电保护算法设计中的应用策略

在电力系统故障分析阶段、原始保护算法设计阶段,可以基于暂态信号可定制精细化实时时频关联分析算法对故障仿真数据、现场故障录波数据进行全频带、无遗漏、尽可能精细化的分析,以期为分析各种故障所表现出的暂态量特征、从中发现保护算法的新特征量、设计可以实时运行的新特征量提取算法提供关键性的基础信息。针对这一过程,笔者当前能想到的研究方向有:

针对某一路暂态信号的采样值序列,寻找其由各滤波器滤出的位于几十、几百个频段上的实时分量信号的量值随时间或(/和)频率变化的规律,寻找量值对时间或(/和)频率的次导数的变化规律,寻找上述各阶导数曲线之间的交叉关系,寻找各路暂态信号的上述变化规律之间的交叉关系。

6 算法涉及的其他后续工作

本文所做的工作,仅仅完成了暂态信号可定制精细化实时时频关联分析的第一步:实时滤出各频段的分量信号,为后续算法模块提供基础数据,为新特征量的发现、新特征量提取算法的研究拓展思路。后续的数据处理工作将更为复杂、繁重。

在发现保护算法的新特征量、设计新特征量提取算法阶段,需要从大量故障仿真数据、现场故障录波数据中滤出的更大量的频域细分数据流,对其离线进行多维度关联分析,这将有可能必须依赖大型机、云计算、大数据处理等执行大数据量、大运算量计算的最新科学计算工具,从而有可能必须在继电保护行业采用最先进的离线数据分析手段。

在将所设计的新特征量提取算法映射为保护装置可实时执行的实现算法之后,在实现算法的实时执行阶段,将涉及大量的实时数据并行处理工作,很可能需要运用FPGA的并行运算能力予以实现。

FPGA在大量的实时数据并行处理方面比其它技术手段更具性价比优势,而运算量需求的急剧增多,又将导致几千、上万元一片甚至更加昂贵的高端FPGA芯片大量应用于继电保护装备制造业。这一成本有望因为继电保护装置“四性”的提高、整个电力系统运行质量的提高而被客户所接受,进而把整个行业的蛋糕做大。

同时,与实时海量运算伴随而至的片内/多FPGA芯片系统架构设计问题、原始算法向实现算法映射的策略问题、实现算法的优化策略问题、单FPGA芯片多通道/多FPGA芯片多通道工作模式下的可靠性控制问题、冗余运算问题、热备用芯片/热备用通道的实时监测/状态判决/无缝切换问题、片间/板间的高速可靠数据传输问题、运算/传输的容错/前向纠错问题、功耗控制问题、芯片供电问题、EMC问题等等,都将成为无法回避的工作。

7 结语

暂态信号可定制精细化实时时频关联分析算法是可以基于FPGA予以实现的。这一算法对频带进行了精细化的、可灵活设置的、有重点的划分,实现了在所分析的全部频段内的高时域分辨率,同时保持了输出数据的时频关联特性,为暂态信号的实时时频关联分析提供了更精确、更灵活、可实现的数据预处理工具,为暂态量保护装置中新特征量的发现、新特征量提取算法的研究提供了新的基础、新的思路。

[1] 黄丹,陈树勇,王玮.基于广域测量信息的电力系统暂态稳定控制技术研究[J].发电技术,2018,39(5):389-396.

[2] 胡列翔,戚宣威,裘愉涛,等.电网全频域暂态信息记录及分析系统[J].浙江电力,2018,37(7):31-35.

[3] 薄志谦,张保会,董新洲,等.保护智能化的发展与智能继电器网络[J].电力系统保护与控制,2013,41(2):1-12.

[4] 王珺,董新洲,施慎行,等.配电线路单相接地行波保护的实现与试验[J].中国电机工程学报,2013,33(13):172-178.

[5] 何正友.小波分析在电力系统暂态信号处理中的应用[M].北京:中国电力出版社,2011:20-24

[6] 吴继华,王诚.Altera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社,2005:3-9.

[7] 张桂青,冯涛,张杭,等.继电保护系统级专用芯片的设计[J].电力系统自动化,2001,25(20):45-47.

[8] 张桂青,冯涛,王建华,等.基于IP核的智能化电器SOC设计与实现[J].电工技术学报,2003,18(2):27-30.

[9] 何人望,谢丹丹,杨毅波,等.FPGA在基于IEC61850的馈线保护中的应用[J].华东交通大学学报,2010,27(4):52-56.

[10] 阮建国,陈炯.基于FPGA的数字保护中卡尔曼滤波的实现[J].电力系统保护与控制,2009,37(22):121-125.

[11] 陈志敏,曹建.电力系统继电保护的FPGA方案设计与研究[J].华中电力,2007,20(3):11-18.

[12] 黄文清.电能质量扰动在线监测方法研究[D].长沙:湖南大学,2007

[13] 亓学广.基于FFT和小波变换的电力系统谐波检测方法研究[D].青岛:山东科技大学,2007.

[14] 于群,MATLAB/Simulink电力系统建模与仿真[M].北京:机械工业出版社,2011:175-179

[15] 徐文波,田耘.Xilinx FPGA开发实用教程[M] .北京:清华大学出版社,2008:422-427.

The FPGA-Based Customizable Precision Real-Time Time-Frequency Correlation Analyse Algorithm for Transient-Signal Analysis

LIN Wei

(Self-employed, Jinan 250100, Shandong Province, China)

Aiming to the precision and real-time analysis requirement of transient component in power system fault signal, a new time-frequency correlation analysis algorithm was presented, whose frequency domain segmentation is different from Mallat. This algorithm can run in real time, which makes precision, flexible and focused domain segmentation. At the same time, time-frequency correlation in the full frequency-range is maintained. An FPGA-based example module to implement this algorithm was designed. A MATLAB-based distributed parameter grid simple model was established. Simulation on this module provided 500 kHz-sampled-value sequence of fault signal. The capability and practicability was preliminarily proved by providing the sampled-value sequence to the example module. The application strategy for designing relay protection algorithm was suggested, and prospects of the work associated with this algorithm was provided.

relaying protection; transient based protection; wavelet transformation; time-frequency correlation analysis; field-programmable gate array (FPGA)

10.12096/j.2096-4528.pgt.18259

2018-05-15。

林伟(1973),男,工程师,研究方向为以FPGA 为核心实现暂态量继电保护装置、广域暂态量主保护系统,linwei_jinan@126.com。

林伟

(责任编辑 车德竞)