一种高动态双模抗干扰接收机设计方法

王晓光

(中国电子科技集团公司第十研究所,四川 成都 610036)

0 引言

抗干扰接收机基于阵列天线自适应形成动态的方向图,对干扰信号形成零陷进行对消,对信号来向具有一定的增益,以达到抗干扰的接收能力。刘汉超、梁昊等人对抗干扰算法进行了研究,给出了设计的一般原则和方法[1-6];西安电子科技大学康乐设计了一种增益65 dB的接收通道,实现了一定的抗干扰能力[7];狄旻珉、张尔扬设计了一种GPS抗干扰接收机[8-11];汤先鹏等人对前端电路的线性度设计方式进行了分析[12],陈建军设计了一种数控自动增益控制(AGC)的通道,减轻了对ADC的动态范围要求[13],武汉大学李彦迪等人对GPS/Galileo双模进行了研究[14],Wu Y,Wang B,Liu K J R等人在干扰自消上做了新的探索[15-18],这些文献对抗干扰接收机设计从多个方面开展了研究,但针对接收前端指标设计方法需要更进一步的深入。本文在此基础上进一步针对BDII(带宽2.046 MHz)和GPS(带宽2.046 MHz)信道复用、提高线性度和减小功耗以及降低组合频率干扰几个方面进行了新设计。

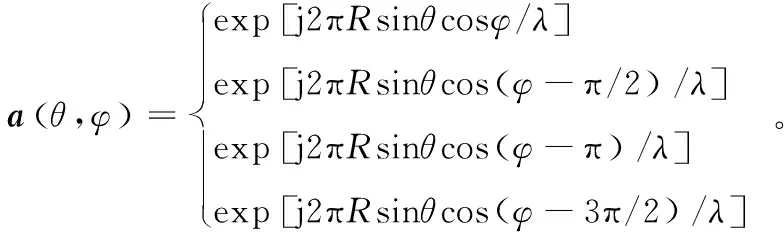

1 天线阵元形式

天线采用了均匀4阵圆形阵列,采用球面坐标系表示入射波的波达方向(DOA),坐标系的原点O在阵列中心,方向矢量a(θ,φ)是关于(θ,φ)的阵列响应,可表示为:

(1)

对于干扰信号数量k的分辨能力,阵元数M应满足:

M≥k+1。

(2)

式(2)的4元阵最多能抗3个不相关干扰。理想的通道电性能完全一致,实际在实现时存在一定的时延和增益相对误差,各通道不完全一致,为此中频输出信号可表示为:

(3)

式中,sp(t)分别是同一个信号入射到不同阵元形成的,信号具有相关性,而nm(t)复高斯白噪声。记

S(t)=[s1(t),s2(t),s3(t),s4(t)],

(4)

N(t)=[n1(t),n2(t),n3(t),n4(t)]。

(5)

则对干扰来向的估计归结为求解矩阵:

X(t)=AS(t-τi)+N(t),

(6)

式中,A为导向矢量矩阵,包含了信号以及干扰的来向信息,考虑到接收通道的幅度相位失真,设通道i(i=1,2,3,4)的幅度及时延响应分别为(Ai,τi),式(2)修正为:

X(t)=AAiS(t-τi)+N(t)。

(7)

由式(7)可知,幅度以及时延的不一致性,将带来信号及干扰来向计算的误差,影响到对干扰零陷的深度及信号来向的增益。因此抗干扰4通道接收机通道间的匹配程度是影响接收机抗干扰性能的关键指标。

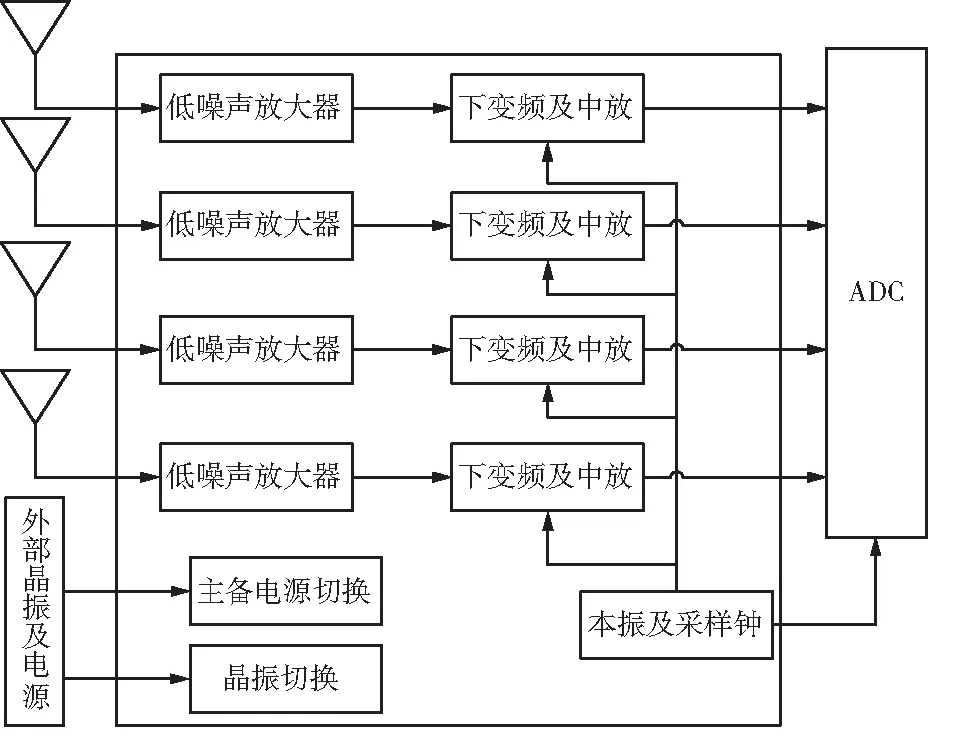

2 抗干扰接收机的基本组成及原理

抗干扰接收机主要由4阵元双频点无源天线、4路低噪声放大器、4路下变频和中放通道、共用本振和采样钟模块、主备电源切换电路以及晶振切换电路等功能模块组成,如图1所示。

图1 双模抗干扰信道原理

3 有源天线设计

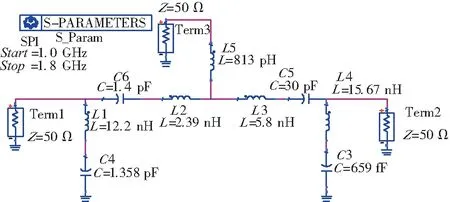

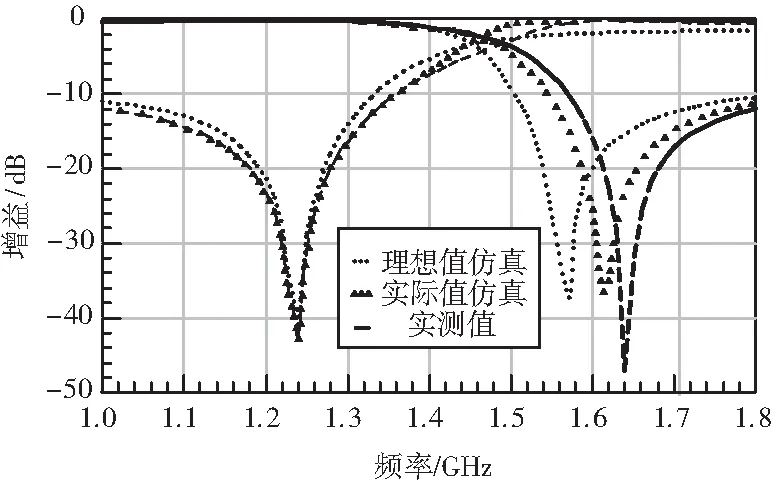

针对存在BDII/GPS双系统的情况,采用独立的硬件通道会大幅增加功耗,考虑到2个频点间隔300 MHz,设计了一种有源器件复用的低噪声放大器(LNA)通道,通过无源的三端口滤波器实现对信号的区分和隔离设计,仿真优化得到的元件需要根据器件标称值来折中实现,LNA有源电路选用2级ATF54143放大器级联设计,该器件呈宽带幅频特性,设计为30 dB增益;通带特性主要由无源电路实现,无源三端口滤波器电路原理图、仿真及实际测量结果如图2和图3所示。

图2 三端口LNA仿真原理

图3 三端口滤波器仿真及测试结果对比

4 通道设计

接收通道将低噪声放大器输出的信号分别进行下变频、滤波及适当的放大以适应ADC的动态范围,同时提供足够高的线性度以减小失真。通道增益的下限应保证中频信号被ADC量化至少有1 bit有效位,通道增益的上限应保证最强的干扰信号被ADC量化同时有一定的功率回退,以免超过ADC量程而使采样数据无效。GPS导航信号采用了BPSK调制及扩频体制,到达地面的强度的最低规范值C/A码为-130 dBm,BDII信号功率与此相当,BDII在通带内的噪声功率为-104 dBm,GPS在通带内的噪声功率为-111 dBm,通带内高斯白噪声功率超过了信号功率,于是ADC量化到的是带内的热噪声功率。经过通道的线性放大后被ADC采样量化,因此要求通道增益的上限为:

Gmax=ADCFS-J/S-(-160+30)。

(8)

对于具有90 dB干信比(J/S)要求的4阵列抗干扰天线,天线端接收的最强信号是带内的干扰信号,高于信号90 dB,同时对于ADC的动态的要求为90 dB-(max(-104 dBm,-111 dBm)+130 dBm)即74 dB,ADC采样的1 bit对应6.02 dB,则选择有效位数在12 bit以上的ADC即可满足要求,而最小增益取决于现有ADC能量化的最小信号,选择有较高有效位数的ADC,有效位数越高其噪底越低,对小信号的分辨率越高,理论上通道的增益可以适当降低,但增益较低的通道对ADC噪声贡献的压制作用减小,不利于包含ADC的整个接收通道噪声系数的改善,因此通道的增益取允许增益的上限。以典型的ADC满量程2 V-Vpp计算,中频输入阻抗200 Ω,则ADCFS=4 dBm,于是Gmax=44 dB,考虑预留一定功率回退,将通道增益设计为40 dB。

增益分配及线性度分析:增益设计的分配原则,应同时考虑通道有尽可能高的线性度,同时有尽可能低的噪声系数。通道总增益设计为40 dB,按照信号的放大链路方向,分别是低噪声放大器(LNA),通常设计为30 dB左右,那么下变频通道的净增益约为10 dB,考虑到下变频通道各级电路之间的匹配损耗2 dB,则通道增益不大于12 dB。根据电路级联的噪声系数(NF)公式及线性度公式:

(9)

(10)

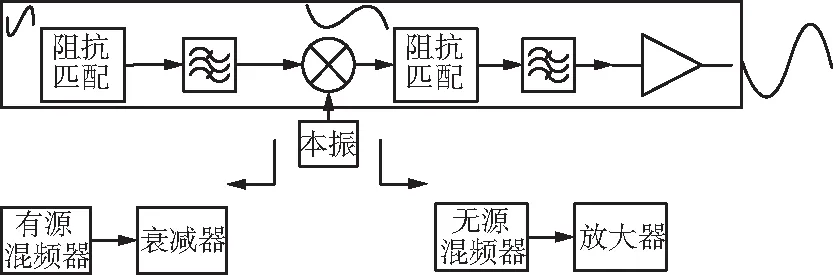

即总的噪声系数主要由前级决定,这是因为前级信号非常微弱相对于噪声比较敏感,而总的线性度主要由后级决定,这是因为随着信号被逐级放大,后级器件的对信号失真贡献越大,要求后级电路有较高的输出三阶截点(OIP3)。综合考虑以上因素,通道由预选滤波器、混频单元和中放单元构成,级与级之间通过阻抗匹配改善驻波(VSWR),通道原理框图如图4所示。

图4 BDII/GPS通道原理

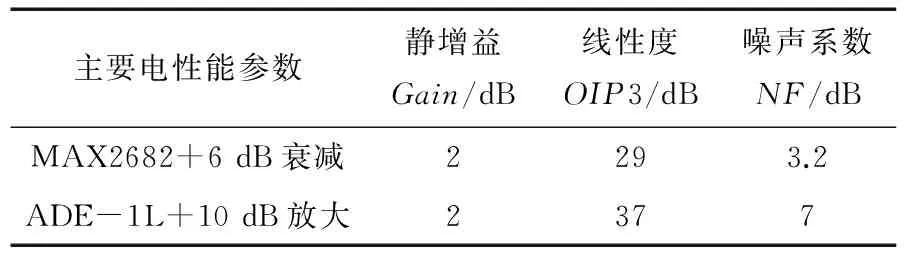

预选滤波器需在较低的差损和较高的选择性之间平衡,射频声表滤波器(SAW)能够同时满足这2个要求,针对BDII和GPS选择了SF2186及B4060,其差损和矩形系数满足系统的使用要求。混频单元有2种方案:① 采用具有较高线性度,类似于MAX2682这类对本振电平要求较低(≥-10 dBm)有源混频器;② 采用类似ADE-1L这类高线性度,带插入损耗,对本振电平要求较高(≥0 dBm)的无源混频器。2种方案通过MAX2682在其后级增加衰减以达到和ADE-1L加后级中放相同的净增益,由于混频器之前信号通过30 dB增益LNA放大后,对混频器的NF不敏感,选取的原则是线性度优先级最高,其次是噪声系数,最后是功耗。通过仿真比较2种方案的参数,如表1所示。

表1 有源混频与无源混频方案对比

主要电性能参数静增益Gain/dB线性度OIP3/dB噪声系数NF/dBMAX2682+6 dB衰减2293.2ADE-1L+10 dB放大2377

由表1可知,无源相对有源混频器线性度高而噪声系数差,因此通道的设计应选择线性度较高的无源混频器ADE-L方案,差损通过下一级的10 dB增益的中频放大器进行补偿。

中放前选择了LC中频滤波器,一方面是为了滤除混频后的带外干扰,另一方面是为了减小差损,由于BDII以及GPS导航信号都采用了BPSK的调制方式,其带内能量主要集中在载波附近;为了提高选择性,可以将LC滤波器的带宽设计得略小于信息带宽(BDII为20.46 MHz),另一方面,带宽变窄又会使得通带内的相位波动加大,导致4个通道之间不一致性变大,影响了调零的深度。综合考虑选择BDII中频滤波器带宽为18 MHz,GPS为2.5 MHz。为满足通道净增益为10 dB的要求,选择了20 dB左右增益的高线性度中放AD8352,中放输出阻抗为200 Ω,通过阻抗匹配电路接入有效位为12.5 bit高性能AD9269。

5 频率流程及本振设计

多通道接收机的总功耗较大,电磁环境复杂,为了降低功耗和减小滤波器的使用种类,双系统接收机需要进一步考虑不同系统之间的串扰,为此选择通道采用了一次变频,大大减少了整机内的频率种类和组合干扰产物,将中频统一到相近的频率,可以选用相同的中频放大器,降低中频滤波器设计难度。整机中存在的频率有参考源fref,一般选择10 MHz或者20 MHz,以与频率合成器的输入频率范围相适应,BDII本振LOB,GPS本振LOG,采样钟fclk,则在系统内产生的组合频率为:

n1fref±n2LOB±n3LOG±n4fclk。

(11)

频率选取原则上应满足:

(12)

依据理论计算式(12)有多组解,采样钟频率fclk范围以50~65 MHz为宜,考虑到本振的输出上升沿较为陡峭,导致输出谐波衰减较慢,选择相应的本振频率LOB≥20fclk,LOB≥20fclk,进一步考虑到统一中频,及对GLONASS系统的组合频率的电磁兼容性,最终分别选定为62,1 220,1 530 MHz,这样将双系统中频中心频率统一到46 MHz附近,减小不同通道之间的组合频率杂散,提高了BDII及GPS通道之间的电磁兼容性。

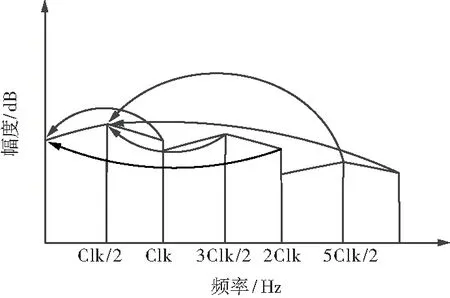

6 采样钟降噪设计

采样钟对中频的采样,等效为对中频的下变频,以及ADC频率响应范围内按照奈奎斯特带宽的频谱折叠,折叠效应如图5所示。

图5 中频及采样钟频谱折叠效果

62 MHz采样钟的相位噪声在对中频采样时,按照上述方式折叠到通带内,产生了噪声的积分累计,其中产生影响的带宽为ADC采样带宽,为了提高采样信号的信噪比,通过先对采样中进行线性放大,再经过30 kHz窄带晶体滤波器衰减带外相位噪声至热噪声的水平,降低了原始采样钟的远端相噪;通过该电路的设计,将近端相噪从-135 dBc@1 MHz提高至-141 dBc@1 MHz。

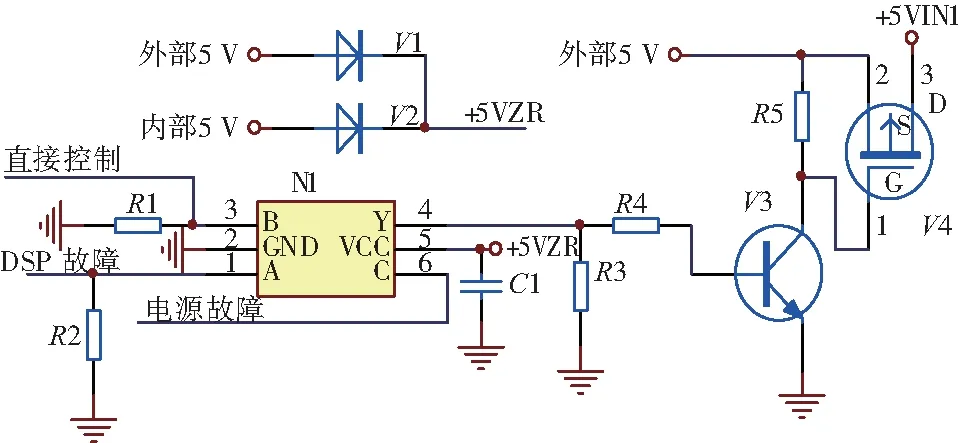

7 主备电源及晶振切换

接收机设计成在内部和外部电源同时输入时,以及内部电源或信号处理硬件故障时可正常工作,为此设计了电源切换电路,切换功能电路如图6所示。

图6 电源切换电路原理

N1选型为NC7SZ11P6X逻辑电路,对接收机内的电源情况综合后给出切换信号,接收机内同时设计了晶振切换电路,在检测到外部高稳定度晶振输入时,自动切换到外部晶振,其主要原理为对外部参考输入进行检波,当超过一定的门限时,通过内部逻辑电路结合射频开关,将晶振输入从内部切换到外部,以输出相位噪声指标相对较高的本振和采样钟信号。

8 电磁兼容设计

通道之间的隔离度是干扰对消的关键指标,同时有源信道包含2个系统多个频点,为此针对每个通道设计了独立的屏蔽腔,将通道间的隔离度提高至相邻通道65 dB以上,相距较远的通道隔离度大于75 dB。接收通道LNA增益30 dB,变频通道12 dB,由于前级增益较高容易引起放大器自激,为此设计成LNA单独分腔,通过屏蔽隔条开小孔的方式耦合;通过对电源的仔细设计,防止杂散通过电源线传导耦合形成信号的正反馈,在印制板中电源层进行了整层单独设计,上下层设计成GND层以去耦,提高了电路的电磁兼容性,BDII/GPS双模接收机设计实现如图7。

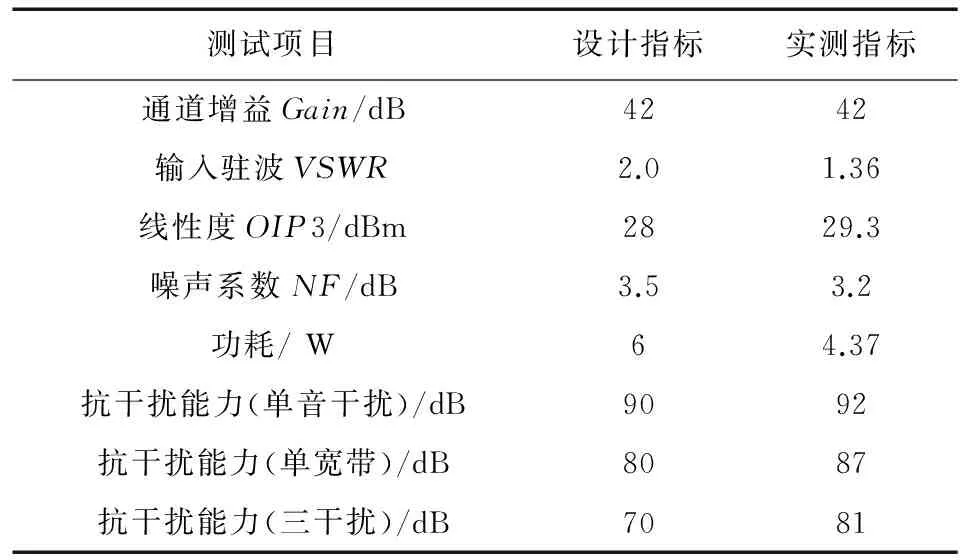

9 系统测试与分析

通过整机抗干扰测试验证,测试结果与设计指标对比如表2所示。

表2 设计指标与实测指标对比

测试项目设计指标实测指标通道增益Gain/dB4242输入驻波VSWR2.01.36线性度OIP3/dBm2829.3噪声系数NF/dB3.53.2功耗/ W64.37抗干扰能力(单音干扰)/dB9092抗干扰能力(单宽带)/dB8087抗干扰能力(三干扰)/dB7081

10 结束语

通过设计双通道LNA,结合独立的变频通道,在同一个射频输入通道内实现了BDII/GPS的放大和下变频,将主要的有源器件减少了40%,通道采用了无源混频器结合放大器的通道电路形式,提高通道的线性度的同时降低了通道的功耗,也减小了由于强本振信号产生的杂散信号;合理的频率规划减少了组合干扰,通道实现了优良的幅相一致性和较高的隔离度。相比已有的抗干扰前端,在解决功耗和线性度的矛盾方面提供了参考,提升了整机的综合性能。该接收机功耗较低,线性度较高,实现了实际抗干扰能力单音干扰90 dB,单宽干扰87 dB,三干扰80 dB以上。通过小批量试制,系统工作稳定,具有较好的应用前景。