雷达通信一体化技术

韩晓娱,刘会红, 张 晖

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;2.中国电子科技集团公司第二十八研究所,江苏 南京 210007)

0 引言

雷达通信一体化设计,是雷达系统和通信系统的有机结合及资源共享,是近年软件无线电平台综合一体化系统的主要发展方向。

根据应用方向的不同,雷达系统和通信系统的差异性主要体现在系统功能、发射功率及信号波形等方面。雷达系统的主要功能是发射雷达信号,通过对接收的目标回波进行处理来获取目标的距离及速度等信息,一般采用强指向性天线,实现在一定发射功率下,快速准确地进行目标定位与目标探测。通信系统的主要功能是将数据调制到载波上进行连续信号的收发,一般采用全双方式,天线指向性强,对信道特性要求较高,在一定信息速率、传输体制下进行高效准确安全的数据传输。由于系统功能的不同,雷达信号和通信信号的行进路程不同,因此各系统对发射功率的要求不同。雷达需要对二次散射的回波进行接收处理,一般要求较大的辐射功率,常规雷达的峰值发射功率一般在千瓦以上。通信系统传输距离相对雷达系统来说较短,因此通信系统对发射功率的需求小很多,一般不超过百瓦级。雷达波形可采用连续波(CW)和脉冲调制波形[2]。脉冲体制雷达收发采用同一天线。通信系统一般采用连续波信号,可采用FDMA,CDMA或TDMA传输体制[3-4],为保证通信质量,一般会有前向纠错,通过纠错编译码,提高通信质量,减少发射功率。

雷达系统和通信系统研究的对象不同,所以长期以来被严格区分,但随着近年软件无线电技术的发展,一体化平台功能越发强大,作为信息获取和处理的电子设备,从工作原理、系统结构及工作频段等方面来说,二者又具有许多相似之处,因此基于信号共享的一体化平台设计成为雷达通信系统的发展方向。

1 一体化系统关键技术

雷达系统和通信系统都是电磁波的发射和接收过程,在系统硬件设计上二者有相当大的相似,都包含天线、射频发射接收及数字信号处理器等。在频率应用范围上,通信系统已经在以前只属于雷达范畴的频段上工作,而雷达系统也在VHF中原属于通信范畴的频率段上工作[1]。因此尽管雷达系统和通信系统间存在许多差异,但在原理和系统结构上仍具有许多相似性。在应用频率和信号的形式上,只要增加变频系统和信号处理措施,可使雷达资源为通信系统所共用。一体化系统涉及传输体制设计、突发解调算法和高校纠错编译码技术几项关键技术。

1.1 雷达通信一体化传输体制设计

本文将雷达系统作为主系统来开展一体化设计。雷达系统采用脉冲体制,脉冲雷达周期性地向开放空间辐射脉冲形式的电磁波信号,其脉冲持续时间仅占发射周期的很小一部分。在脉冲体制下,发射机发射脉冲信号时,接收机的开关工作在“关”的状态;当发射机没有发射脉冲信号时,接收机的开关工作在“开”的状态,可随时接收回波信号[5]。

基于雷达系统,通信系统共用平台的信号处理系统、射频系统和天线系统。在工作体制方面,考虑到雷达功放具有较高的脉冲功率,功放不能长时间连续工作,通信系统选择了脉冲体制工作模式,并按照脉冲工作模式设计了一种半双工高速突发通信体制[6]。

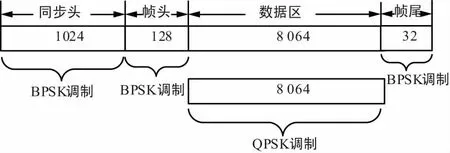

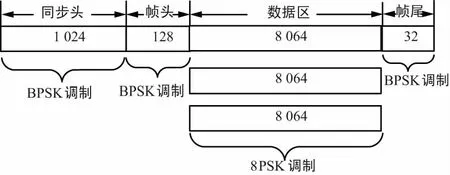

雷达天线孔径收发占空比设为10%,即发送50 μs,接收450 μs。对于通信系统,设计了一种突发通信体制。突发帧结构由同步头、数据区和帧尾组成,同步头采用BPSK调制体制;数据区采用QPSK(或8PSK)调制体制,采用码长为8 064的LDPC编码方式。其中帧同步头为(1 024+128)bit;QPSK调制体制数据区为2个编码块。8PSK调制体制时数据区为3个编码块。帧同步头用于定时、FFT频率校正、载波恢复和数据区定位。帧格式如图1和图2所示[7],传输速率与突发速率关系如表1所示。

图1 QPSK突发帧结构

图2 8 PSK突发帧结构

表1 传输速率与突发速率关系表

1.2 高速突发解调技术

基于高速突发通信体制,高速突发解调涉及2项关键技术:① 突发信号快速检测及定时估计技术;② 突发信号快速载波恢复技术。针对关键技术开展了仿真及算法设计。

1.2.1 基于数据辅助的信号快速检测及定时估计[8]

“010101”形式的单路同步数据长度为256 bit,成形滤波器与匹配滤波器的设计采用常规的平方根升余弦滤波器,滚降系数0.3,Eb/N0=5.3 dB,相对于符号速率的归一化载波频偏为0.1,仿真10 000次,结果如图3所示。经过统计,信号检测同步开销为256 bit时,信号检测概率为100%,虚警概率为4×10-4。通过仿真可以看出,定时估计的同步开销为256 bit时,归一化的定时估计误差范围为±0.06。

图3 归一化定时估计误差的仿真结果

通过仿真得出了该定时估计误差对解调误码率的影响,如图4所示。由仿真结果可以看出,在Eb/N0=5.3 dB时,由±0.06的归一化定时误差造成的信噪比损失为0.2 dB左右。

图4 定时误差对误码率的影响

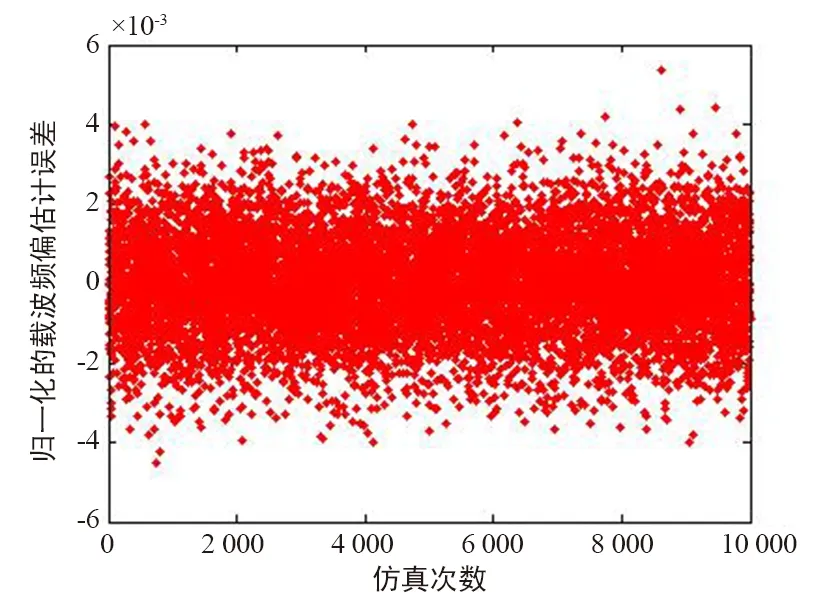

1.2.2 基于数据辅助的载波恢复[9]

单路辅助数据为‘010101’形式,长度为256 bit;成形滤波与匹配滤波滚降系数α=0.3;Eb/N0=5.3 dB;相对于符号周期的剩余归一化定时误差为0.06;相对于符号速率的归一化载波频偏为0.1;仿真10 000次,结果如图5所示。

图5 归一化频偏估计误差的仿真结果

由仿真结果可知,载波频偏估计的同步开销为256 bit时,归一化的载波频偏估计误差≤±1%,可以满足锁相环的入锁要求。经过大量仿真统计,得到单路辅助数据长度为256 bit时锁相环的相位跟踪误差在±π/20左右。仿真得出了该相位误差对误码率的影响,如图6所示。结合仿真图可以看出,载波恢复总同步开销为512 bit,其造成的信噪比损失在Eb/N0=5.3 dB时为0.65 dB左右。

图6 载波相位误差对误码率的影响

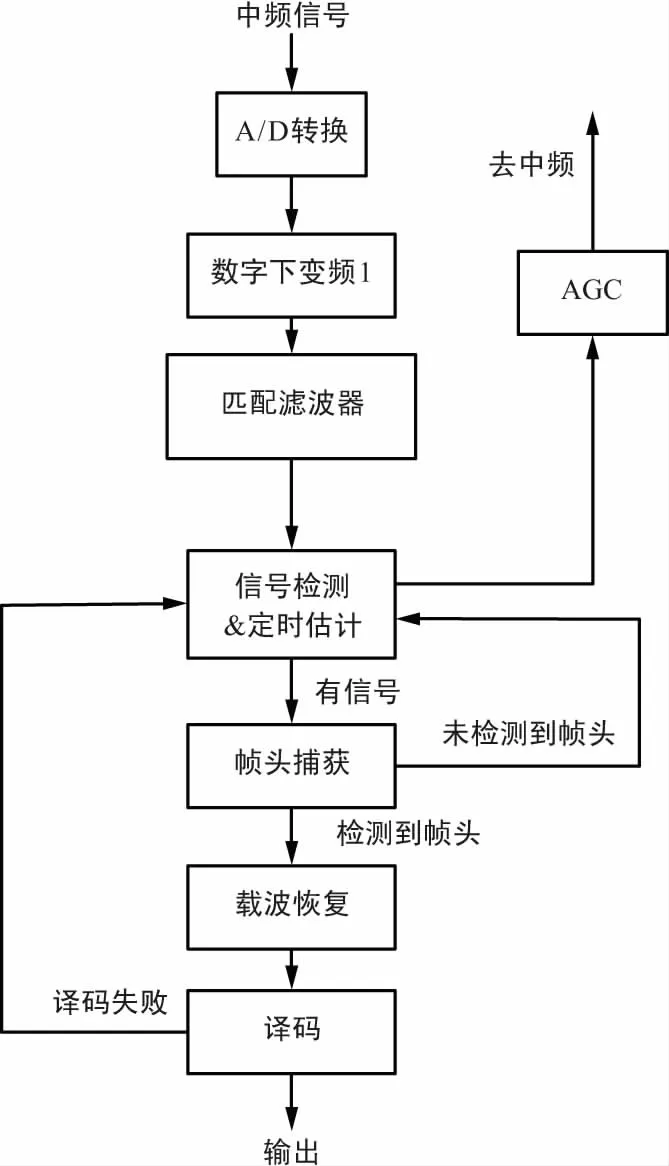

基于以上仿真分析,开展解调方案设计,原理如图7所示,其中信号检测与定时估计采用同步头512个“1010”序列进行数据辅助估计完成的。利用帧捕获模块实现传输帧同步功能。

图7 基带解调单元工作原理图

通过对传输帧帧头一定长度的PN序列进行相关求和与能量值进行比较来判断是否检测到帧头来实现定位。载波恢复采用数据辅助的方法,解调信号首先经过信号检测模块检测到信号后,进行数据缓存,通过对同步头的处理,得到频偏初始估计值,然后启动数据辅助锁相环工作,利用512个的“1010”序列进行快速锁定,512个之后采用通用的判决反馈环进行跟踪。

1.3 高速LDPC编译码技术[10]

采用突发通信体制,收发占空比为10%,即发送50 μs,接收450 μs,突发符号速率达到150 Mbps,因此高速高效LDPC编译码码长选取及并行编译码算法设计是需解决的关键技术。

影响LDPC编译码性能的主要因素主要有以下几点:

① 构造LDPC码的码距是否够长;

② 构造LDPC码的校验矩阵围长(Girth)是否够长;

③ LDPC译码算法的选择。

因此,对校验矩阵的构造和译码算法的设计至关重要的。

1.3.1 编码器校验矩阵构造设计

采用准循环(quasi-cyclic,QC)LDPC码,其H矩阵为[8]:

式中,各子矩阵Ai,j是b×b的循环右移置换矩阵或者是b×b的0矩阵,n固定为24。由于循环置换矩阵Ai,j完全决定于偏移量,因此总可以用母矩阵Hb=[p(i,j)]m×n来表征校验矩阵H,如果p(i,j)>0,则表示H矩阵中对应的Ai,j是右偏移量为p(i,j) 的置换矩阵;若p(i,j)=0 ,则表示Ai,j为单位阵;若p(i,j)<0(一般用-1来表示),则表示Ai,j为全0矩阵[10]。

此设计的LDPC码有以下特点:

① 描述简单,特别适合硬件实现;

② 译码电路具有通用性,不同码长下译码器的基本结构不变;

③ 编码可采用移位寄存器电路快速实现;

④ 所有码都是规则LDPC码,不但易于实现,而且最小码距大;

⑤ Error Floor低,无需再和其他编码级联使用。

因此,设计采用准循环LDPC码,作为编译码实现方案。

1.3.2 译码算法设计

根据编码采用的结构,译码算法可以采用NMSA算法。NMSA算法的执行是按照:更新R阵,接着更新Q阵,再更新R阵……这样循环的顺序来进行迭代的。其优点为更新R阵时用的是最新的Q阵信息,但是增加了很多等待时间。

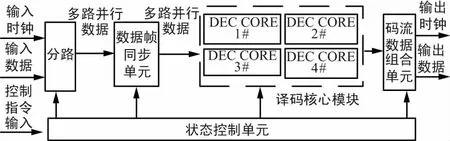

为加快收敛速度,在硬件实现时,可以采用NMSA算法[10]的同步部分并行执行(S-NMSA)算法。S-NMSA算法的主要思想在于同时更新R阵和Q阵,其他方面和NMSA算法几乎一致,可以说它就是NMSA算法的一种Turbo变型。它的优点是如果R阵和Q阵的更新分别是按照串行实现的,那么该算法迭代一次的时间仅仅是NMSA算法的一半。虽然R阵和Q阵的更新无法利用全新的Q阵和R阵信息,以致单纯地从迭代次数上看,该算法的收敛速率大大低于NMSA算法。不过在相同的时间内,该算法可以比NMSA算法获得多一倍的迭代次数,这可弥补它收敛速度慢的缺点。译码总体结构框图如图8所示。

图8 译码器模块划分

1.3.3 仿真测试及结果

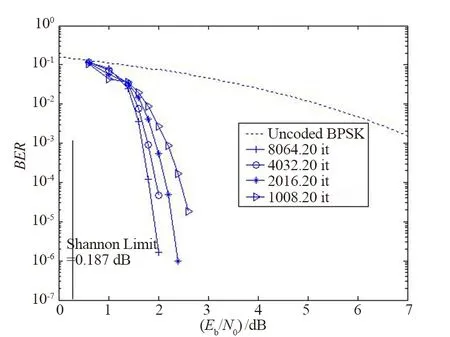

为验证所设计LDPC码的合理性,对其性能进行仿真,采用定点的乘性修正最小和NMSA算法,迭代次数为20次。编码方式为1/2,3/4,仿真结果如图9和图10所示。

图9 码率为1/2下所设计的LDPC码迭代性能

图10 码率为3/4下所设计的LDPC码迭代性能

本文完成了多种码率(1/2,3/4,7/8)及码长(1 008,2 016,4 032,8 064)的LDPC编码和解码功能,通过在数字部分加入高斯白噪声,对不同译码迭代次数(10,15,20)的编码增益进行自环测试。

通过试验测试,采用码长为8 064 bit,码率为3/4和1/2的2种LDPC码码字,在迭代20次后可以提供>8 dB的编码增益,单路译码速率达到80 Mbps,两路并行的情况下,译码速率超过150 Mbps,满足技术要求。

2 实验验证

在实验平台上实现了突发速率为150 Msps的QPSK和8PSK、纠错编译码为LDPC(1/2,3/4)的通信系统数据发送与接收,并进行了自测,测试结果如表2所示。

表2 传输性能测试记录表

达到的技术指标:

① 突发调制解调方式:QPSK、8PSK;

② 信道编译码:LDPC1/2(QPSK),LDPC3/4(8PSK);

③ 传输速率: 20 Mbps(QPSK),40 Mbps(8PSK);(占空比10%条件下)

④ 传输性能:QPSK,LDPC1/2,Eb/N0=5.5 dB情况下,误码率优于10-6。

8PSK,LDPC3/4,Eb/N0=9.5 dB情况下,误码率优于10-6。

3 结束语

根据雷达系统和通信系统特点,设计了一种半双工高速突发通信体制。根据高速突发体制特点,完成基于数据辅助的信号快速检测及定时估计及基于数据辅助的载波恢复算法设计,解决解调器载波快速捕获跟踪问题。完成高效LDPC编码器校验矩阵的设计及LDPC译码算法的仿真及实现,编译码速率超过150 Mbps。搭建了数据传输链路发送与接收验证平台,完成了相关模块的软件设计验证,实现了突发速率150 Msps的通信系统收发。

对利用雷达系统进行通信及数据传输提出了一种可行方案,为雷达通信一体化的发展和建设提供技术借鉴。