基于STM32的DAC信号输出实验设计

陈甸甸, 王 怡, 金小萍

(中国计量大学 信息工程学院, 浙江 杭州 310018)

嵌入式系统原理作为电子信息工程和通信工程等专业的核心课程,理论知识点多,覆盖学科面广,命令操作多,教师讲授难度大,学生感觉内容枯燥乏味,无法产生学习兴趣[7-9]。为改变这种状况,我们在该课程的实验教学过程中采用了ARM Cortex-M3内核的STM32F103微控制器为目标平台,结合相应的实验项目,强化理论与应用实践相结合,引导学生独立思考,培养学生的学习兴趣和学习积极性、主动性。

STM32F103系列主要分为基础性系列与增强型系列,本文使用的STM32F103ZET6属于增强型系列,模拟/数字(A/D)转换、数字/模拟(D/A)转换是该系列处理的重要功能。本文主要利用数字/模拟转换器(DAC)、直接内存访问(DMA)和定时器(TIMER)3个模块,设计了STM32引脚输出不同的模拟波形实验。DAC的作用是将数字量转换成电压,DMA可以不占用CPU资源读取内存中的数字量,输出波形的周期可以通过修改TIMER的定时时间得到。

1 硬件系统

DAC模块是数字输入、电压输出的数字/模拟转换器,可以配置为8位或12位模式,数据格式可以分为8位右对齐、12位左对齐和12位右对齐3种。STM32F103ZET6的DAC模块有2个输出通道并带有DMA功能,每个通道都有单独的转换器。在双DAC模式下,2个通道可以独立地进行转换,也可以同时进行转换并同步地更新2个通道的输出[10]。

DAC功能框图见图1。DAC模块主要分为触发模块、控制逻辑、DAC转换器。触发模块包含7个硬件触发和1个软件触发。DAC中比较重要的寄存器有数据保持寄存器(DHR)、数据输出寄存器(DOR)以及DAC控制寄存器(DAC_CR), DOR不能直接操作,它的值是由控制逻辑从DHR中更新过来。

图1 DAC功能框图

本文利用通道1实现波形输出,数据格式采用12位右对齐,触发采用硬件触发。写入的数据根据相应的位移后被转存到DHR1寄存器,当触发发生后经过3个APB1时钟周期,数据传至寄存器DOR1。经过大约3 μs后,输出即有效,引脚可测得模拟电压。因此,只要改变数据寄存器中的数据就可以实现不同电压信号的输出,产生相应的波形。如果要改变波形的周期,只要通过TIMER改变数据寄存器中数据保持的时间即可。

当DAC的参考电压为Vref+的时候,DAC的输出电压是线性的,从0~Vref+。12位模式下DAC输出电压与Vref+以及DOR的计算公式如下:

A new scheme of blending initial perturbation of the GRAPES regional ensemble prediction system

DAC输出电压=Vref+×(DOR/4095)

2 软件部分设计

本文所设计的实验硬件部分无需外接模块,PA4和PA5引脚即为DAC的两路通道,主要功能通过软件控制实现。软件系统的设计任务:一是利用STM32cubeMX平台进行初始化配置后,生成初始化MDK工程;二是在keilMDK5.24下进行基于HAL(硬件抽象层)库程序的开发。软件的开发流程见图2。

图2 信号输出软件流程图

2.1 信号输出在CubeMX中的配置

STM32cubeMX是一款图形化软件设置工具,支持STM32全系列芯片,用户可以非常方便地配置MCU的引脚、时钟、外设等,并且支持自动生成工程项目文件,可以极大地减轻开发工作、节省时间和费用[11-13]。本实验在STM32CubeMX中配置步骤如下:

(1) 启动STM32CubeMX,点击NewProject新建工程。

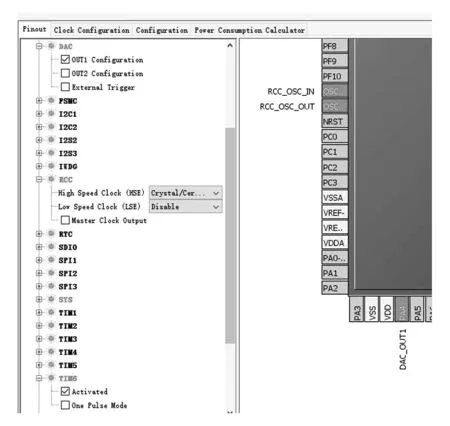

(2) 进入MCU型号选择界面,搜索并双击选择STM32F103ZETx后,进入Pinout引脚配置界面(见图3)。

(3) 选择通道1(DAC有2路通道),启用外部高速时钟晶振,选择定时器TIM6作为DAC的触发源。

图3 STM32引脚配置界面

(4) 进入时钟配置界面。外部晶振通过锁相环(PLL)倍频得到PLLCLK,之后得到系统时钟72MHz,DAC挂载在APB1总线上,该总线下外设的时钟频率最大为36MHz,定时器时钟频率为72MHz。

(5) 在DAC配置界面(见图4)的参数设定选项卡中,选择定时器6作为触发事件,其余两项设置为disable。

(6) 在DMA设定选项卡中,添加DAC通道1的DMA功能,方向从内存到外设,模式为循环模式,内存地址需要自增,数据宽度为HalfWord。DMA参数设置界面见图5。

图5 DMA参数设置界面

(7) 输出引脚PA4的配置设为模拟模式,当DAC通道使能后,相应的GPIO引脚会自动与DAC的模拟输出相连。

(8) 在定时器TIM6(配置界面见图6)的配置选项中,将预分频(Prescaler)设置为72-1,计数方式为向上计数,自动重载寄存器(AutoReloadRegister)的值设置为1000,触发事件设置为更新事件。在该设置模式下,定时器6的计数周期为1ms。如果需要改变DAC输出波形的周期,可根据需要设置预分频和自动重载寄存器的值。

图6 定时器配置界面

各项配置完成后,点击生成工程文件按钮,弹出工程设置窗口,填写工程名与选择目录,选择编译器MDK-ARMV5,即可生成初始化工程文件。

2.2 波形信号的产生

波形信号产生的基本原理是利用数字法来实现的。实验设计中利用STM32F103ZET6单片机的DMA功能,将波形数据表中的数据直接传至DAC的数据寄存器,再通过DAC转化输出。DMA传输数据的时间则由TIM6定时器控制,每经过一段时间传输一个数据。定时器TIM6的计数时间需要大于DAC的转化时间以保证每次DAC转化完成后再传输下一个波形数据。

3 波形信号输出测试

波形数据表中存储的是信号的离散值,可以通过计算直接得到。本实验中设计了3种不同的信号波形,得到的实验测试结果如下:

(1) 正弦波信号。定义一个数组Sine_data[]来存储正弦波信号的离散值:

Sine_data[i]=(sin(2*pi*i/N)+1)*(dac_maxvalue/2)

其中N为采样点数,dac_maxvalue是DOR的最大值,采用12位数据,最大为0xFFF。正弦波的测试波形如下图7,采样点数N=100,周期为100 ms,而STM32F103ZET6的Vref为3.3 V,因此输出波形的峰峰值Vpp也为3.3 V。

图7 正弦波测试信号

(2) 三角波信号。定义数组Triangle[]来存储三角波信号的离散值:

Triangle[i]=i/(N/2)*dac_maxvalue(i<(N/2));

Triangle[i]=(N-i)/(N/2)*dac_maxvalue((N/2) 三角波信号的测试波形见图8,周期和峰峰值测量结果与理论值吻合。 图8 三角波测试信号 (3) 锯齿波信号。定义数组sawtooth[]来存储锯齿波信号的离散值, Sawtooth[i]=i/N* dac_maxvalue 锯齿波的测试波形见图9,测试结果与理论值吻合。 图9 锯齿波测试信号 本文利用STM32单片机中的DAC模块、DMA功能和定时器设计了不同的波形输出实验,主要特点是实验成本低、功耗小、输出的波形稳定性好。同时,将STM32CUBEMX引入嵌入式原理实验教学后,学生可以更加直观、形象地配置初始化程序,这有助于提高实验教学的效率和学生的学习兴趣。通过波形输出实验的学习,可以帮助学生深入理解DAC的原理、应用和实践操作方法,为学生进一步学习与开展课外科技活动打下良好基础。

4 结语