固态硬盘及其主控的低功耗设计方法研究

李 炜

(中电海康集团有限公司研究院,浙江 杭州 311121)

0 引言

随着大数据和云计算的发展,海量的数据需要进行存储。另一方面,随着新型存储介质技术的发展,NAND闪存(NAND FLASH)工艺的进步和良率的不断提升,QLC等先进闪存的不断产品化,固态硬盘(Solid State Disk,下文中简称SSD)的成本已经下降至接近企业级机械硬盘 (Hard Disk Drive)的水平。SSD在服务器、数据中心、存储系统以及日常消费电子产品中的应用越来越广泛。

SSD有两种典型应用场景,即消费级应用和企业级应用。在消费级应用领域,SSD主要是以卡、便携式移动硬盘以及笔记本电脑、手机移动存储的形式出现,比如在苹果手机中,已经内嵌了BGA封装的NVMe SSD。在企业级应用领域,SSD主要是以PCIe接口的板卡、SAS/SATA企业存储盘的形式出现,接口形态一般是U.2、EDSFF等。

SSD的功耗指标,直接影响到产品竞争力。在笔记本及手机等便携式移动设备中,SSD过高的功耗会造成待机时间缩短,从而影响用户体验。在企业应用中,由于企业级SSD大多运用在数据中心,一个数据中心里会有成千上万的服务器,每个服务器机柜里都会有几十块乃至上百块固态硬盘,SSD过高的功耗会造成数据中心整体发热量增大、耗电量上升和企业用户整体拥有成本 (Total Cost of Ownership,TCO)增加,也会造成服务器的散热设计难度增大;同时,高温环境会严重影响NAND FLASH介质的寿命,从而减少SSD的寿命,影响整个数据中心的稳定性。

1 固态硬盘的功耗分析

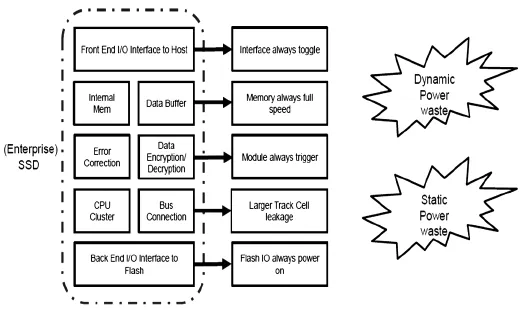

如图1所示,主流的固态硬盘由下面几个主要部件组成。

(1)固态硬盘控制器芯片(SoC)

控制器芯片作为SSD的大脑,控制着数据和命令的传输流程。SSD主控的低功耗设计,直接影响到整个SSD的功耗和性能,这也是我们在低功耗设计方案中需要重点考虑的部分。

SSD主控芯片的功耗,通常由两部分组成:一部分是芯片内部晶体管不断翻转造成的动态功耗;另一部分是芯片内部晶体管在上电状态下源极和漏级产生的漏电流,俗称静态功耗。动态功耗通常跟电压、操作频率有关,静态功耗跟晶体管的工艺、Track值以及标准单元的门限电压有关。

图1 基本的固态硬盘组成

图2描述了SSD主控芯片内部的几大基本组成部分以及基本的SSD数据流、命令流。可以看到,SSD主控芯片的主要功耗产生在下面几个部分:

①由于主机需要通过PCIe控制器发送命令和数据,因此SSD主控内部的PCIe接口模块信号总是在翻转,产生大量的动态功耗;

②内部Memory总是运行在全速模式,产生了大量动态功耗;

③内部逻辑模块,主要是算法IP,比如LDPC编解码部分的晶体管总是在翻转,产生大量的动态功耗;

④芯片内部高Track的CMOS晶体管的高漏电产生了一定的静态功耗;

⑤Flash的IO接口总是处在上电状态,产生一定的静态电流与功耗。

图2 SSD组成部件中的功耗来源

(2)NAND FLASH 颗粒

NAND FLASH颗粒占据整个固态硬盘80%以上的空间,是SSD功耗的最大组成部分。NAND介质颗粒本身的芯片功耗,由提供介质颗粒的厂家自行设计,用户无法改动。通常,对于介质颗粒的功耗控制,是与SSD控制器芯片配合一起进行整体的低功耗设计;主控芯片的设计人员可以通过对Flash IO接口的频率、工作模式以及介质厂家开放的测试模式,来对介质颗粒进行一定的功耗调整和优化。

(3)DRAM 颗粒

DRAM在SSD中用来存储表项和部分重要元数据,在系统不需要DRAM工作的时候,我们尽量让DRAM处在自刷新状态。但是由于DRAM的原理所限,为了维持数据,DRAM还是需要每隔一段时间对所存储的数据进行自刷新,在系统IDLE模式下,DRAM仍然会产生一定的动态功耗。

(4)NOR 颗粒

NOR颗粒在SSD中主要用来存储固件,因此在上电时会产生动态功耗。由于NOR是一种非易失性介质,因此在关闭时没有静态功耗的产生。

总体来讲,DRAM和NOR产生的功耗相对较少,而且无法进行优化。由于NAND FLASH颗粒大多采用英特尔、美光、东芝、三星等原厂颗粒,我们无法对颗粒内部进行改动,所以NAND介质的功耗控制通常结合控制器芯片进行一体化设计。本文主要研究固态硬盘控制器芯片的低功耗设计方法。

2 固态硬盘主控的低功耗设计

对于NVMe SSD的控制器芯片,我们采用了多种设计以降低功耗。

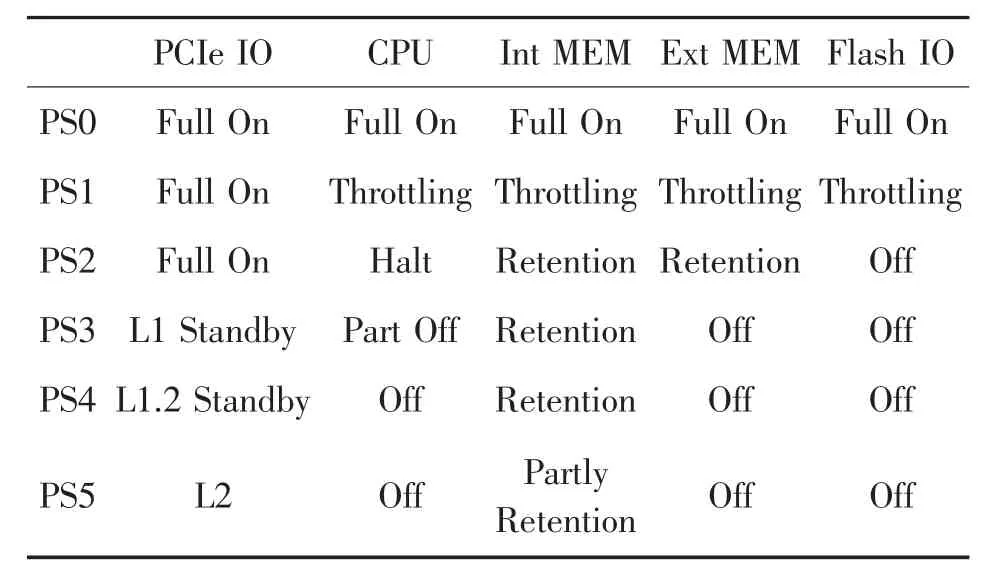

2.1 PCIe接口低功耗以及盘片低功耗模式

当前NVMe SSD的主机接口通常基于PCIe,其功耗在整个主控中所占比例相当大。如表1所示,为了降低PCIe控制器的功耗,PCIe的标准协议规定了几种低功耗模式,允许用户根据实际的负载情况,在几种模式中进行有效地切换,从而达到控制功耗的目的。

我们可以看到,在PCIe协议的规定中,从L0到L2,PCIe接口逐渐从全速工作模式变化到深度节能的低功耗模式,随着性能的不断降低,功耗也在不断降低。结合芯片的其他主要部件的工作模式,我们为整个主控设计了5种低功耗模式,如表2所示。

表1 PCIe低功耗模式

表2 主控芯片的低功耗模式

该方案一共设计有5种功耗模式(Power State),从PS0到PS5,性能和功耗都是逐步降低的。固态工程师可以根据系统的应用场景和IO负载,控制主控芯片在这几种功耗模式之间进行切换,在不同的应用场景下,最小化整个系统的功耗。

2.2 SoC低功耗设计方法

SoC的功耗分为静态功耗和动态功耗。随着半导体工艺的演进,电压越来越低,动态功耗下降很明显,静态功耗所占的比例越来越显著。减少静态功耗的方法通常包括使用门限电压较高的标准单元库、电源门控等;用来减少动态功耗的手段通常有时钟门控、多电压域设计、动态降频调压、衬底电压偏置技术等。

针对SSD主控SoC芯片,我们设计了如下低功耗方案:

(1)为了降低静态功耗,对于逻辑单元比较多的模块,特别是LDPC算法模块,在网表实现时尽可能采用低Track、高门限电压的标准单元。

(2)在各类操作模式下,在用Design Compiler进行逻辑综合时,针对数据路径模块(Data Path)采用自动门控插入(Auto-Clock Gating)技术,减小动态功耗。

(3)针对Flash通道的模块,在该模块功能处于IDLE时,尽可能地进行电源门控(Power-Gating)。

(4)尽可能采用异步时钟设计的高密度Memory单元,特别是针对CPU模块,减少CPU的时钟树上产生的大量动态功耗。

(5)对于Memory的睡眠模式和关断模式要灵活地运用。

(6)在不必要的时候关断整个SoC的顶层,最小化Memory和CPU指令消耗。

总而言之,所有这些手段的核心在于尽量根据应用场景来控制内部逻辑和Memory单元的工作状态,尽量避免内部信号的无谓翻转;同时,在可以关闭的时候尽可能关闭模块的电源,降低整体的漏电流。

2.3 功耗压制技术和通道压制技术

对于NAND介质以及Flash IO通道上的功耗控制,我们采用了如下几种方法:

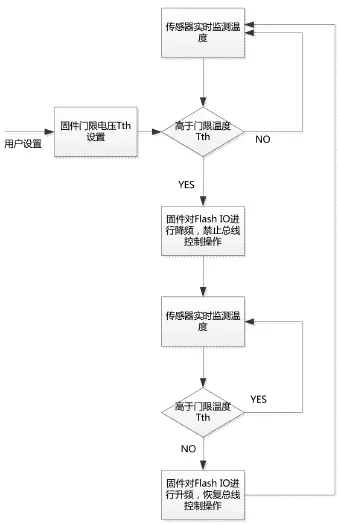

(1)功耗压制技术(Power throttling)

在SSD固件程序中设定一个温度门限值,当主控温度传感器检测到温度高于该门限温度时,固件主动对主CPU和Flash IO进行降频操作,必要时停止对Flash总线上的数据和命令访问。该方案能显著降低NAND介质的动态功耗,提升可靠性和寿命。流程如图3所示。

(2)通道压制技术(Channel throttling)

SSD控制器为了提高并发写入的速度,通常在Flash后端采用多通道并发读写设计。当前主流的企业级SSD控制器一般都采用8通道或者16通道,在提高了并发读写性能的同时,带来的问题是功耗的显著上升。

为了降低Flash功耗,同时也为了保护NAND介质的寿命,我们采用了通道压制技术,即在固件中设置一定的负载门限,如读写带宽值、正在工作的Flash Die的数量等。系统在操作的过程中,由固件实时监控IO的带宽和正在工作的Flash Die的数量并定时上报,当系统检测到所监控数值高于门限时,控制器主动取消对于NAND介质的命令及数据传输,静默总线操作,通过这种方式,有效地降低动态功耗的产生。另外随着生命周期内NAND介质寿命的不断减少,门限值也可以动态地进行调整。该方法能够显著降低Flash介质功耗,但不可避免地牺牲了瞬时性能,在用户看来会有一定的掉速,因此门限数值的选择要非常谨慎。

图3 功耗压制技术操作流程图

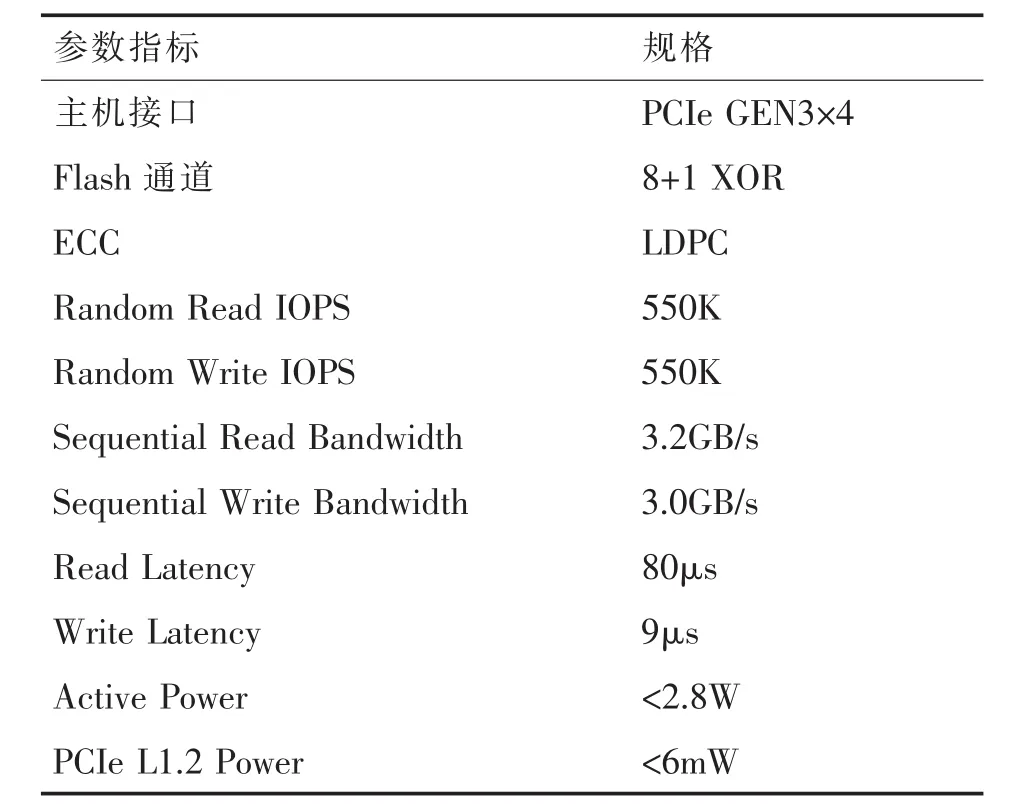

表3 实验数据和指标

结合以上几种低功耗设计方法,我们基于NVMe SSD的原型在EDA里进行仿真,结果如表3所示。结果显示,采用了多种低功耗设计手段的SSD主控配合Flash介质,良好控制了动态功耗和峰值功耗,与主流SSD厂家如美光、三星等在产品相关的参数指标上处在同一档次水平。

3 结语

本文针对固态硬盘及其主控的低功耗设计进行了研究,提出了一系列低功耗设计方法。实验结果显示,综合运用这一系列的低功耗设计方法,可以在固态硬盘的设计中显著地降低整体盘片的动态功耗及待机功耗,具有良好的应用前景和推广价值。