基于FPGA的SDIO信号差分传输系统的实现*

刘继平 ,常 皓 ,李德阳

(1.中国电子科技集团公司第三十研究所,四川 成都 610041;2.96901部队26分队,北京100094)

0 引 言

SDIO安全模块内部集成安全SOC芯片,具备高性能、低功耗、高安全性等特点。为满足SDIO安全模块的可靠性检测需求,需将SDIO信号进行无失真远距离传输。

SDIO是一种IO接口规范,以其传输速度快、兼容性好等优点被广泛应用于手机、PDA等移动手持设备中,出现了多种基于SDIO接口的设备,如相机、录音器、扫描仪、GPS、蓝牙和无线网卡等[1]。

由于SDIO接口总线的抗衰减能力较弱,传输距离短,只能用于近距离数据传输。当距离较远的SDIO接口设备需要进行数据传输时,一般采用直通带缆延长,但延长的最大距离为50 cm左右;或者采取协议转换[2]方式传输,但会增加硬件和软件设计成本。LVDS具有低功耗、低误码率、低串扰和低辐射等特点[3],广泛用于解决高速I/O接口问题。本文主要介绍一种SDIO信号的远距离传输系统的实现方法,并通过实验验证了设计的正确性、可靠性和实用性。

1 SDIO信号差分传输系统分析及设计

SDIO总线分为两端,一端为主机端,另一端为设备端。通信由主机端发起,设备端解析命令并响应。根据SDIO协议规范[4],SDIO总线信号包括CLK时钟线、CMD命令线和DATA[0∶3]四根数据线。其中,CLK时钟线是单向信号,CMD命令线和DATA[0∶3]数据线都为双向信号。对于双向信号,进行差分传输时需要一个控制信号来确定差分信号传输方向。本设计通过FPGA信号处理模块解析SDIO协议,及时产生控制信号,以控制差分信号传输方向的切换,保证数据流向的正确性,从而使整个SDIO总线延长通信链路工作正常。宿主设备为主机端,SDIO安全模块为设备端。主机端通过差分传输系统与安全模块进行数据交互。差分传输系统只对SDIO信号进行物理层转换,进行协议监控而不进行协议转换。

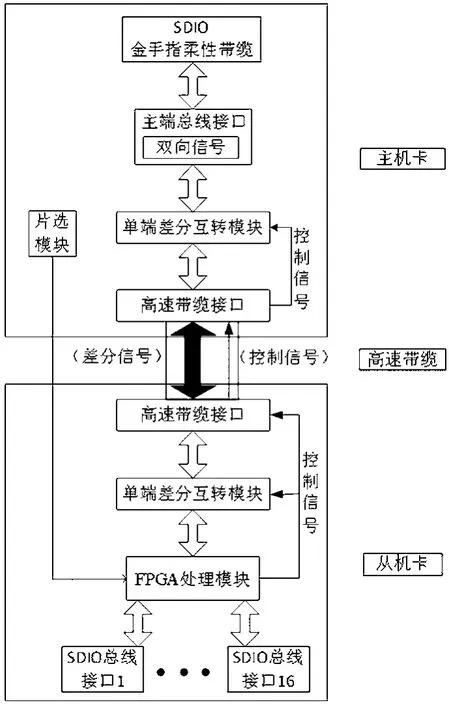

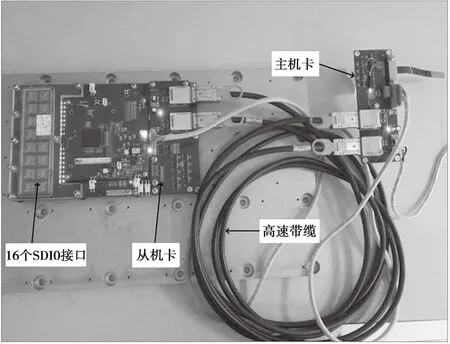

差分传输系统主要由主机卡、高速带缆和从机卡组成,如图1所示。其中,主机卡主要由SDIO金手指柔性带缆、主端总线接口、单端差分互转模块、片选模块和高速带缆接口组成。从机卡主要由高速带缆接口、单端差分互转模块、信号处理模块和SDIO总线接口组成。

图1 差分传输系统

2 差分传输系统的主要硬件实现

2.1 单端差分互转模块

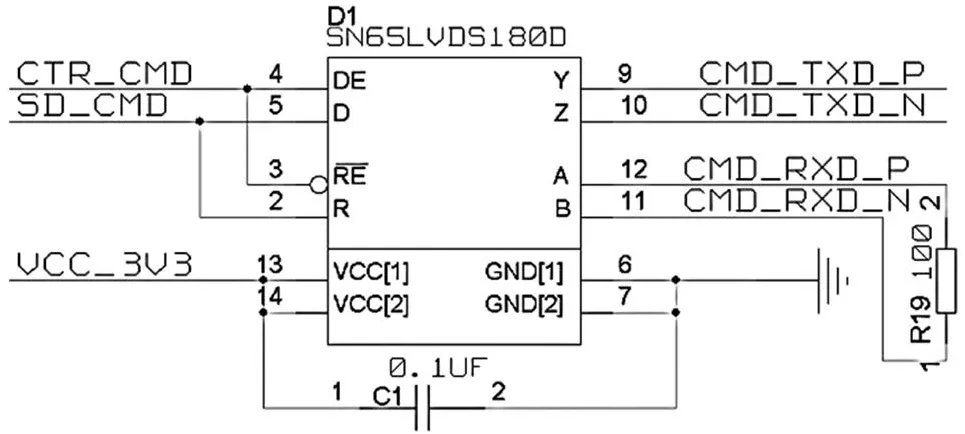

在主机卡和从机卡中都包含单端差分互转模块。它们一个工作在单端转差分发送模式时,另一个必定工作在差分转单端的接收模式。单端差分互转模块主要采用高速差分线驱动器/收发器SN65LVDS180D进行设计[5]。单端差分互转模块具有150Mb/s的传输速率,能够保证20 MHz的SDIO信号无失真传输。

以CMD命令线的传输为例,如图2所示。CTR_CMD为控制信号,主机卡和从机卡中的控制信号相反,一个处于发送状态时,另一个处于接收状态。当主机端发起命令时,主机卡CTR_CMD的电平值为“1”,主机卡处于发送状态;而从机卡的CTR_CMD则为“0”,从机卡处于接收状态。主机卡通过SDIO金手指柔性带缆连接至主机端,将SD_CMD单端信号转为CMD_TXD_P/CMD_TXD_N的LVDS差分信号;再通过高速带缆连接从机卡的CMD_RXD_P/CMD_RXD_N端,将差分信号还原为单端信号;从机卡接收到SD_CMD信号后,通过SDIO总线接口连接至设备端。反之,当主机端接收响应时,主机卡中的CTR_CMD由“1”切换为“0”,处于接收状态;从机卡则处于发送状态。

图2 CMD信号传输硬件

数据线DATA[0∶3]与CMD信号线都是属于双向信号,原理与CMD信号传输原理一致。

CLK信号都属于单端信号,始终从主机端输入到设备端。为了保证信号的一致性,也将CLK信号进行差分传输,而不用切换传输方向。

2.2 FPGA信号处理模块

单端差分互转模块的控制信号CTR_CMD决定SDIO信号在整个差分链路的数据流向,对整个系统的正常通信起着关键作用。而FPGA信号处理模块决定控制信号的输出,决定了单端差分互转模块的收发状态,从而控制SDIO总线信号的数据流向。要产生正确的控制信号,需要对SDIO总线信号进行实时监控与分析。信号处理模块的核心器通过FPGA编程实现[6]。SDIO总线信号的工作时钟一般为20 MHz,因此需要更高的时钟才能采集SDIO信号。FPGA内部集成锁相环,可以把外部时钟倍频,核心频率可以到几百兆赫兹。FPGA信号处理模块主要由集成锁相环、命令解析单元和控制信号输出单元组成。SDIO总线信号包括CLK时钟线、CMD命令线和DATA[0∶3]数据线。信号处理模块主要处理数据信号。SDIO协议有一个特点,任何读写操作都可以通过CMD命令类型来判断。从机卡将CMD命令线的差分信号转换为单端信号后,输入到信号处理模块。信号处理模块在高频时钟下监控分析SDIO总线信号,通过判断CMD命令类型,能够精确产生单端差分互转模块的控制信号,控制单端差分互转模块的工作状态,从而控制SDIO总线信号数据流向,确保整个链路正常工作。

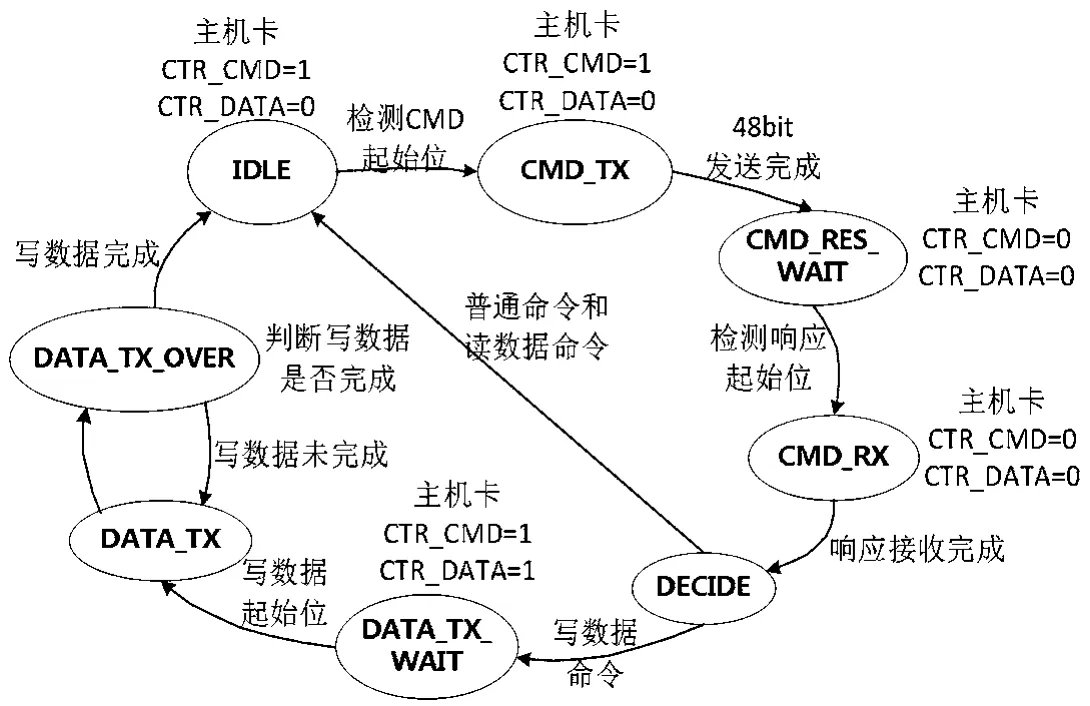

FPGA信号处理模块的处理状态机如图3所示,主要由CMD_TX、CMD_RX、DECIDE和DATA_TX等8个状态组成。

图3 信号处理模块状态机

3 功能仿真和验证

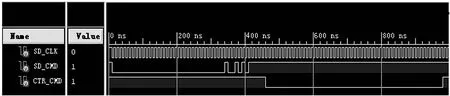

本设计的FPGA信号处理模块用Verilog HDL硬件描述语言编写。为了验证模块的正确性,编写Testbench文件,用仿真软件进行仿真,结果如图4所示。命令线在同步时钟的参考下发送了一个CMD命令,当命令发送完成时,及时给出控制信号;当响应完成时,又及时恢复到初始状态,以等待下一个命令。

图4 CMD控制信号仿真时序

本设计的实现平台采用Xilinx公司的SPARTAN6的XC6SLX150T_2FGG676I,经综合、适配、仿真、布局布线后,占用较少的器件资源。SDIO信号监控模块下载到FPGA后,正常工作,实际环境如图5所示。FPGA可扩展16个SDIO通信接口模块,在主机卡片选模块的控制下,可依次对16个SDIO安全模块进行测试。通过实验验证,设计的差分传输系统可以实现SDIO信号远距离传输,传输距离3 m,且稳定可靠。

图5 SDIO差分传输系统实物

4 结 语

基于FPGA设计的SDIO差分远传系统可满足SDIO安全模块可靠性测试的需求,数据收发正常,各项功能测试正常,且可扩展16个通道,实现批量测试,有效降低了试验成本。在不改变SDIO协议的情况下,可将主机端和从设备进行远距离通信,具有一定的实用价值。