基于FPGA的高精度数字脉冲宽度调制方法

杨 浩,沈晔超,徐冠军

(安徽机电职业技术学院,安徽 芜湖 241002)

随着新一代便携产品和嵌入式系统的不断发展,电子产品在性能上要求更安全可靠,在体积上则日趋小型化[1]。开关电源高频化可以大大减小DC/DC变换器无源元件的体积,数字控制相比较传统的模拟控制可以实现复杂的控制策略,提高了系统的可靠性和灵活性[2]。然而,开关电源高频化带来的一个问题,即数字控制精度问题日趋突出显现。高分辨率DPWM控制器受到了越来越多的关注。随即一些DPWM生成方法被提出,如抖动法、Δ-Σ法、时钟移相法等。这些方法大多将DPWM的分辨率提高到了ns级别。但随着开关电源频率的增加以及系统对开关电源输出电压精度的要求的提高,DPWM的精度必须向着更高级别提升,高分辨率DPWM控制器受到了越来越多的关注[3]。

1 数字脉宽调制器的结构

数字脉宽调制器[4]的结构如图1所示,由加法器延迟模块、低精度DPWM模块以及SR触发器模块等组成[5],其中加法器延迟模块为数字脉宽调制器的核心部分。15位的占空比输入信号被分成两部分,6位MSB和9位的LSB[6],分别作为低精度DPWM模块的输入信号和加法器延迟模块的输入信号[7]。下面对各个环节的功能分别进行介绍。

图1 数字脉宽调制器结构图

1.1 低精度DPWM模块

1.1.1计数器

本设计采用Verilog HDL编程方式实现[8],对于输入时钟信号,只需一个50 MHz的系统时钟信号即可。基于本设计使用的是高频的系统时钟[9],一点细微的误差都会在比较过程中导致错误的发生。在一个同步电路里,所有信号跟随同一个时钟,在二进制数由10000111到10001000的计数过程中,同时会有四个二进制数值发生改变,比较器可能因为通信延迟而认为计数值是由0000到1111之间变化而造成误差,从而影响计数的精度[10]。此时,若能避免电平触发,让比较器只在时钟信号上升沿到来的时候进行边沿触发,即可解决传播延迟问题。本设计采用了格雷码计数器,有效地解决了多个数字同时变化可能带来的信号传输延迟[11]。

1.1.2比较器模块

此模块主要由2个比较器组成,比较器A的功能是将“6位MSB占空比输入值”与计数器A的实时计数值进行比较,输出一个低精度脉宽信号与加法器延迟单元的输出信号进行逻辑与运算[12]。

比较器B是将“开关频率设定值”与格雷码计数器B输出的计数值进行比较,输出另一路脉宽信号作为SR锁存器的输入信号。与此同时,比较器B输出信号的上升沿被用作格雷码计数器B的重置信号以及加法器延迟单元的系统时钟信号[13]。

开关频率设定值是根据系统使用的时钟设定所需的开关频率,设定值在开环时是固定的,在闭环时则根据反馈信号进行修正[14]。例如系统时钟为50 MHz要求的系统开关频率为1 MHz时,此数值设定为50。具体的公式可以写为:

(1)

其中,fclk为时钟频率、fswith为开关频率、n为开关频率设定值如图2所示。

图2 低精度脉宽调制模块系统框图

1.2 加法器延迟线模块

此环节为“加法器进位延迟”实现的具体环节,是本设计的核心部分,由它来为系统提供ps级的脉宽调制信号。高精度延迟线的具体实现方式将在下面进行详细介绍。

1.3 输出模块

输出模块主要由SR锁存器构成,它的功能是将两路已经处理过的脉宽信号进行合成,用高精度加法器延迟模块对低精度DPWM信号进行二次细分,用来提高DPWM的精度,最终得到的高精度脉冲宽度调制信号输出,是整个系统实现高精度脉宽调制的最后环节[15]。

2 加法器进位延迟原理

时钟信号在FPGA内部的逻辑器件之间的传递延迟分为门延迟和连线延迟两种。门延迟指的是信号在逻辑器件自身内部传递过程中产生的电路延迟,门延迟是固定延迟,而连线延迟则是指信号在连接两个逻辑器件之间的连线上传递时带来的时间延迟如图3所示。

图3 FPGA内部逻辑器件延迟

加法器进位延迟DPWM设计的核心思想在于,利用FPGA内部逻辑器件——加法器,在进位时所产生的门延迟,对低精度PWM信号进行二次细分,从而得到高精度的DPWM信号。为了方便理解加法器进位延迟原理,用6位LSB代替9位LSB输入,加法器进位延迟模块的原理如图4所示。

图4 加法器进位延迟原理图

首先,用低精度PWM模块的输出信号作为加法器延迟线模块的开始信号,复加到26=32个与门的输入端,与门的另一个输入为6位LSB经移位寄存器译码后输出的32位数字信号(其中,只有1位为1,其余全为0)。将移位寄存器的32位输出信号按位分别和开始信号进行逻辑与运算,32个与门的输出分别作为32个全加器的一路输入,全加器的另一路输入全部置1。即只有当与门输出高电平时,对应的全加器才会产生进位输出,使其进位位Co=1。

当某个全加器产生第一个进位位时,会直接导致下一个全加器的输出信号S产生一个进位延迟,至此后面的每一个全加器在计算过程中都会产生进位,进而产生一个进位延迟。具体从哪个全加器开始产生进位输出,是由LSB的数值决定。例如二进制LSB是000 011,译码后的数字信号为(00000000000000000000000000001000),即会产生3个进位延迟。图5中,寄存器输出0001000,当开始信号变为高电平时,8路全加器的输入输出对应表如表1所示。

表1 8路全加器输入输出对应表

3 仿真实验

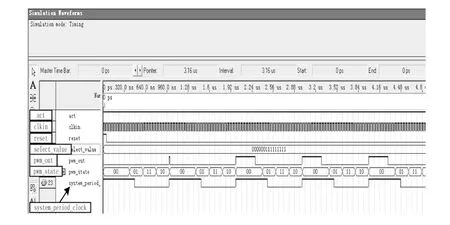

在将程序下载到芯片之前,要对适配生成的结果进行仿真测试。图5是高精度DPWM发生器的时序仿真波形。

其中,act是系统的使能信号;clkin是时钟信号,频率为28MHz;reset是复位信号;select-value是15位占空比输入信号,图中select-value的值是000000111111111;pwm-out为高精度DPWM发生器输出信号波形如表2所示。

图5 高精度脉宽调制输出时序仿真波形

表2 ps级脉宽调制内部资源利用情况

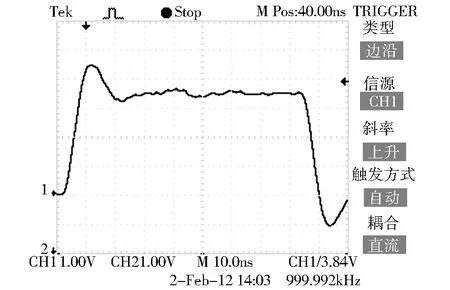

根据仿真实验结果,FPGA内部的加法器的一个进位延迟时间约为70ps。仿真后将此DPWM设计方法在Altera公司DE2-70型FPGA数字平台上进行了实验验证,并与传统的计数比较法生成DPWM方案进行数据分析比较如表3所示。在输入占空比信号分别为110111011000011和110111011010010时,在数字平台输出端得到的波形如图6所示。在实际电路中,因为存在一定的硬件延迟,实测一个加法器进位延迟时间为86ps。

(a)

(b)图6 高精度DPWM波形

表3 两种DPWM生成方案对比

4 结论

本文提出了一种高精度数字脉宽控制方案在FPGA上的实现方法,详细分析了系统中的移位寄存器和加法器进位延迟原理,并提出了有效的实现方法,建立了一套在高开关频率条件下高精度DPWM控制信号产生的解决方案。最后,通过仿真和硬件实验对所提出的方案进行了验证,并与传统的DPWM生成方案进行了对比。