一种新型的固态硬盘控制器芯片架构研究

李 炜,周明政

(中电海康集团有限公司,浙江 杭州 310012)

0 引言

随着大数据和云计算的发展,海量数据需要进行存储。另一方面,随着新型存储介质技术的发展,NAND闪存(NAND FLASH)工艺的进步和良率的不断提升,固态硬盘(Solid State Disk,SSD)的成本已经下降至接近企业级机械硬盘 (Hard Disk Drive)的水平,SSD在服务器、数据中心、存储系统以及日常消费电子中的应用越来越广泛。

传统的SSD控制器,为了节省芯片面积,降低成本、功耗,通常会在设计时采用单核CPU方案,CPU主要用来控制前端与主机侧的接口和通信,FTL表项的分配和管理以及后端介质控制器与NAND存储颗粒中的通信。除此之外,CPU还需要处理日志记录、异常处理流程、FW在线升级等任务。

随着承载的存储数据量的急剧增加,SSD主控芯片计算能力的瓶颈问题越来越凸显,控制器芯片厂家都在设法解决额外的计算任务带来的CPU负载过重问题。如果采用性能更强的CPU,势必造成成本、面积、功耗的上升,同时市场竞争力下降,如果采用多颗性能较弱的CPU来替代,又面临核间通信效率低的问题。

本文采用异构计算的理念,在控制器芯片设计中引入一颗小型 DSP(Cadence Tensilica),应用于SSD控制器芯片架构设计中,能够在不增加过多面积、功耗、成本的同时,分流主CPU的部分计算开销,在提升系统读写性能的同时拥有一定的灵活性。

1 当前固态硬盘控制器架构方案简介

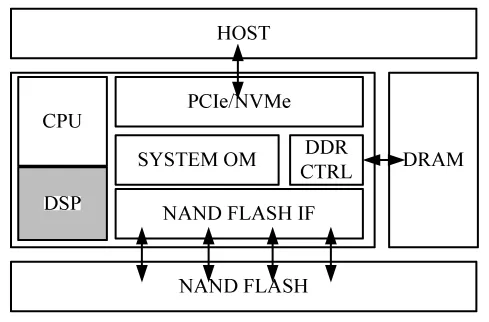

图1为当前主流企业级固态硬盘架构方案示意图。

图1 主流SSD控制器芯片架构图

当前的固态硬盘控制器芯片分为以下几个主要的部分:前端主机接口模块、系统管理模块、后端NAND介质管理接口模块。

前端主机接口模块主要负责接收和处理主机侧下发的读写命令并将数据接收下来存到DRAM中。企业级SSD中,由于对性能要求高,前端主机接口基本上选用基于NVMe(Non-Volatile Memory Express)协议的第三代甚至第四代PCIe(PCI Express)的接口。除此之外,SAS12G(Serial Attached SCSI 12G)和SATA(Serial ATA)接口也是当前SSD前端主机接口的主流协议。

系统管理模块(SYSTEM OM)是SSD控制器芯片的最核心单元,包括闪存地址映射表(Flash Translate Layer,FTL)管理、元数据管理、日志管理、异常处理、读写流程控制、磨损均衡、垃圾回收等。其中FTL表项管理是其中最重要的部分。

FTL主要处理主机下发的逻辑地址(Logic Block Address,LBA)到介质颗粒中存储的物理地址(Physical Block Address,PBA)之间的映射表,是用闪存完全模拟传统硬盘操作的软件层,有了FTL层,闪存设备才能使用,FTL层的效率直接影响设备的性能表现。

系统管理模块的主要作用包括下面几点:

·FTL表项管理;

·垃圾回收的处理;

·增量空间的供给;

·冷/热数据的交换处理;

·Plane、芯片、通道间的并行处理;

·任务请求的排序;

·缓冲区的管理;

·坏块的管理;

·磨损平衡的处理;

·掉电恢复的处理;

·ECC的处理。

NFI(NAND FLASH Interface)主要负责处理跟NAND FLASH颗粒的数据与命令交换。NFI负责把主机侧的读写命令转化成兼容ONFI和Toggle的标准NAND接口协议,并在NAND颗粒和控制器数据缓存之间做数据的读写交互。

ARM系列CPU是当前SSD控制器厂商应用最广泛的CPU种类,其基于RISC精简指令集设计,在功耗方面有着比X86指令集明显的优势,广泛应用在移动端、手持供电系统和对功耗要求较高的产品设计中。

在主流SSD控制器厂商的产品中,ARM 9系列是应用比较广泛的处理器之一。除此之外,有些厂家也采用国产自研CPU如中天微CSKY-CORE等产品来设计自己的控制器芯片。

传统SSD控制器芯片架构的痛点有以下几点:

一是工艺技术的不断进步和成本不断上升的矛盾。随着半导体工艺的不断进步,工艺节点开始下降到16nm、14nm、10nm甚至7nm,在制造过程中的复杂度和光罩成本也越来越高,16nm工艺投片的一次光罩成本就接近350万美元,对于固态存储控制器硬盘的成本来讲,需要大量的出货才能支撑如此之高的MASK费用。因此,为了追求成本和性能的平衡,大部分SSD主控厂商选择28nm工艺作为主流的工艺节点。

二是工艺节点和性能的不匹配。受限于工艺节点,在CPU的选型和CPU运行的主频上,设计人员只能选择中端的CPU种类,而且运行频率受限于工艺,无法提频以提供更高的性能。因此,在数据中心、服务器等高端应用场景中,当前的CPU负载相当重,导致实际应用中带宽和IOPS的波动较大,无法达到企业级应用场景中严格的QoS(Quality of Service)要求。

采用EpiData3.1软件建立数据库并进行数据录入。采用SPSS 22.0软件进行统计学分析。定量资料组间比较采用单因素方差分析,定性资料组间比较采用χ2 检验,以 P< 0.05为差异有统计学意义。

2 Cadence Tensilica DSP的特点

Tensilica IP/DSP系列是Cadence公司开发的一种高性能、低功耗、算法可定制的DSP处理核心。Cadence为其开发了一系列基于特定应用场景的IP,其广泛地应用在音视频处理、汽车电子、高端手机应用处理器、存储设备等。

Tensilica DSP的最大特点在于算法和指令的可定制和可拓展性,从指令集、微结构、接口等方面都提供一些可配置的选项。设计者可以通过菜单选择的方式定制适合自己应用的处理器;在拓展性方面,使用 Tensilica Instruction Extension(TIE)的方法,增加用户的指令、寄存器、寄存器堆等。用户可以使用和verilog类似的TIE语言来描述自己的datapath单元的功能,而相应的RTL代码和工具链自动生成。

基于以上特点,Cadence Tensilica处理器和DSP广泛应用在当前需要异构计算的应用场景中。

3 基于Tensilica DSP的SSD控制器架构方案

如图2所示,为应用Tensilica DSP之后的SSD控制器芯片架构示意图。

本方案的技术特征在于:

硬件层面,在总线上集成Cadence Tensilica DSP的IP核,形成CPU+DSP的双核异构计算架构。

图2 基于Tensilica DSP的SSD控制器芯片架构图

固件层面,基于功能和应用场景对FW进行分类管理。主CPU主要用来处理主机接口的数据命令接收和下发、FTL表项的创建和管理、NAND FLASH介质的读写控制和管理,以及磨损均衡、垃圾回收等介质可靠性算法管理。

Tensilica DSP的主要作用在于:承担部分系统管理模块的功能,如SSD控制器在数据读写过程中,需要记录一些关键状态作为系统日志,在这种经常性需要CPU介入的场景,把日志管理的功能转移到DSP进行处理。

图3显示了采用Tensilica DSP的SSD固件算法内容。

图3 基于Tensilica DSP的固件算法示意图

对于一些近数据处理的应用场景,比如MySQL数据库查询,采用如图3所示的芯片架构和固件方案。

MySQL数据库查询业务,需要SSD主控和跟主机进行频繁的数据和命令交互,并且有大量的主机计算开销。通过改写FW程序,把主机需要处理的SQL查询命令直接下发至SSD主控内的DSP,当待处理的数据信息从NAND FLASH读取到主控缓存后,DSP执行数据库的查询命令直接在片内完成MySQL查询过程,将数据结果存放在主控缓存的OOB空间,然后通知主CPU将其结果返回给主机。在此过程中,实现了将数据库在线计算的业务由主机卸载至SSD主控的Tensilica DSP的过程。

使用固定的读写IO比例数据库基准测试工具BenchmarkSQL在如下两种场景下进行了测试:

第一种,采用市面上已售的SSD盘,其主控芯片为Marvell,主机接口为PCIe GEN3 X 4 lane;

第二种,在FPGA开发板上进行模拟仿真,由于FPGA频率无法和ASIC芯片相比较,因此在性能评估中采取了等比例折算的方法,进行20倍降频,FPGA上的主CPU采用50MHz的工作频率。

图4显示了在两种场景下的CPU负载和读写业务性能对比情况。

由此可见,如果我们把MySQL的查询放在DSP中处理的话,主机负载和盘控负载均能够下降10%以上,也能够保证主要数据通路上的QoS质量,读写性能有了10%左右的提升;同时,由于主CPU的负载减轻,FW可以更主动地启动垃圾回收和磨损均衡,有助于SSD盘片寿命和数据可靠性的提升。

故,采用了本方案的异构计算SSD控制器芯片方案,在NDP(近数据端处理)的应用中有着显著的优势和性能提升,同时又不会引入相比高端CPU更多的面积、功耗和成本开销。

图4 两种场景下的CPU负载和读写业务性能对比

4 结语

本文提出一种新型的固态硬盘控制器芯片架构,能够在数据库查询等NDP应用场景中降低主机负载,提升系统读写性能,保持QoS的稳定。本芯片架构在固态存储领域具备广泛的应用前景。