基于多时源的高稳时间同步装置的研制

,, , ,

(许继电气股份有限公司,河南 许昌 461000)

0 引言

时间同步装置为调度机构、变电站、发电厂内的被授时设备提供高精度时间信号。在使用中,时间同步装置普遍性地暴露了以下问题:如由于卫星系统受到天气、外部干扰等因素干扰;同步装置未能正确识别故障而错误跟随;由于多时源切换过程中各厂家时源切换策略不相同,导致切换的结果也不同,致使输出时间不一致,造成导致设备工作异常的现象;在守时阶段以及时源切换过程中同步装置的输出摆幅过大导致合并单元、同步向量装置等重采样误差过大等[1-2]。因此时间同步装置在外部时源发生变化时能有效切换,并保持自身的输出稳定性、守时稳定性等都是时间同步装置所要必须克服的关键问题。

同时随着我国北斗授时系统的建设速度加快,以及国内国际环境的快速变化,国家电网要求投运的时间同步装置均应采用“天基授时为主,地基授时为辅;天基授时以北斗为主,GPS为辅”[3],并对时间同步装置的各厂家产品进行标准统一与规范,在性能参数上提出了更高的要求。本文便是在此基础上,设计了一款性能稳定、精度高,严格符合国网检测规范的时间同步装置。

1 时钟的硬件设计

卫星接收模块从北斗和GPS接收卫星信号,它们的输出信号会受到多重因素的影响,如天气的原因、信号干扰、接收模块异常等,都存在有偶尔失星的不正常现象,此时接收机输出的秒脉冲不可靠[4]。即便是在正常情况下,卫星接收模块的每个PPS也存在30ns左右的随机误差。然而北斗和GPS长期时间稳定性非常好,卫星模块输出秒脉冲具有一定的随机误差,该随机误差服从正态分布,在样本时间足够长时,其累计误差趋于0。而恒温晶振短时稳定性好,长时稳定性差[5];因此在时间同步时,利用OCXO恒温晶振的频率产生的100 MHz基准频率,测量并记录在北斗或GPS卫星或IRIG-B码同步秒脉冲间隔,在基准信号失步时,以晶振频率为基准,以记录的秒脉冲间隔为参考,通过FPGA输出秒脉冲等时钟信号,可以兼顾长期和短期输出精度和并保证性能稳定。因此在硬件设计上采用CPU+FPGA+高精度恒温晶振的硬件规划。

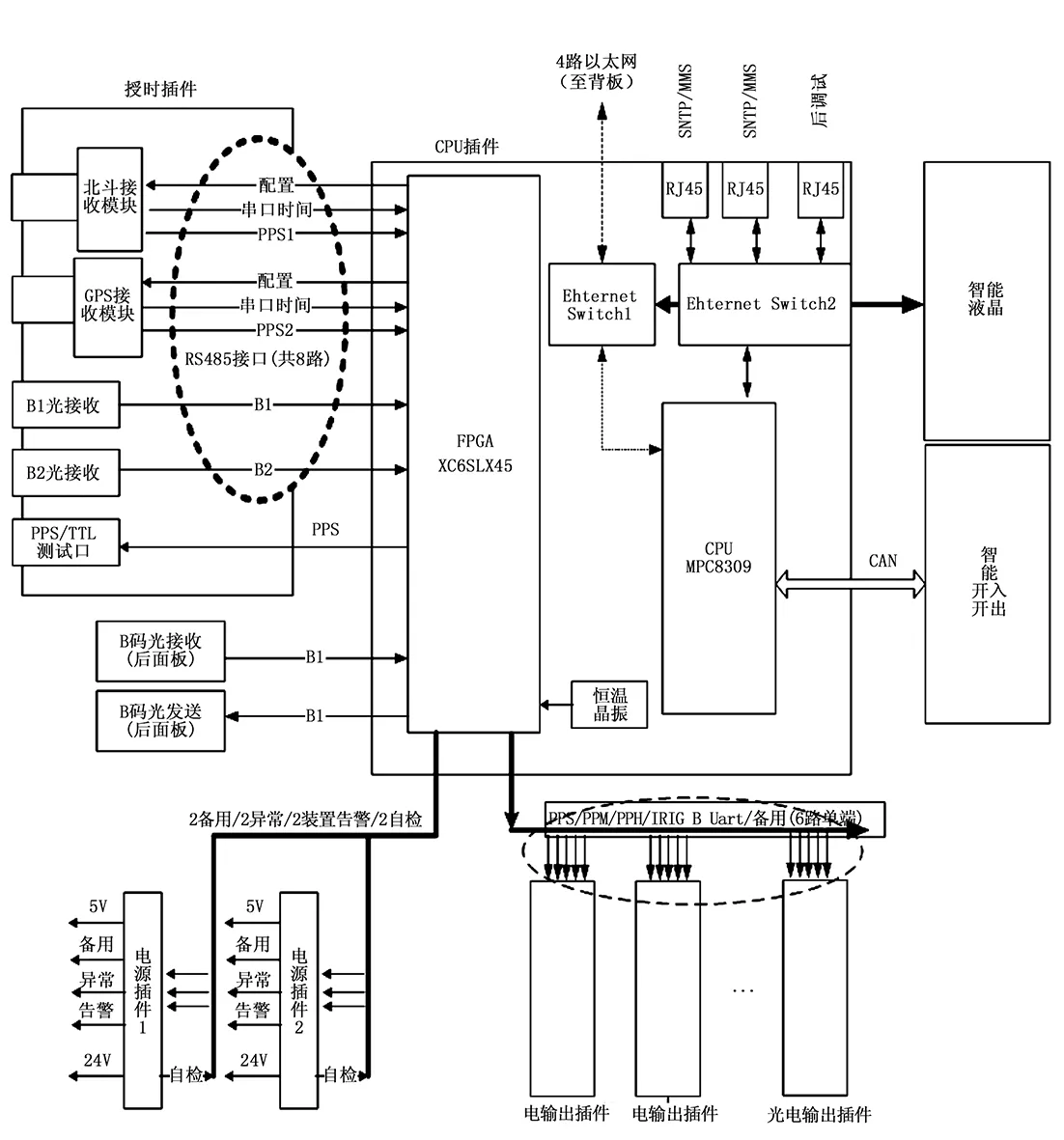

时间同步装置的总体硬件结构如图1所示。整个装置采标准4U机箱,插件式布局,输出可扩展。主要模块为冗余双电源模块,CPU模块,授时模块,输出模块、液晶模块共5个模块构成。

图1 时间同步装置的硬件架构

授时模块可以同时接受多个时钟源,包括北斗、GPS接收模块、地面时源和备钟时源。能同时接收两路卫星信号和两路IRIG-B码信号[6-7],为多时源切换提供了保证。北斗和GPS模块采用国内厂家标准OEM卫星接收模块,硬件软件兼容性强。模块输出采用串口时间报文加PPS脉冲组成,PPS准时沿误差<30 ns。可以通串口报文读取和配置模块信息。授时模块通过RS485接口与CPU进行通讯,保证了信息的抗干扰能力。

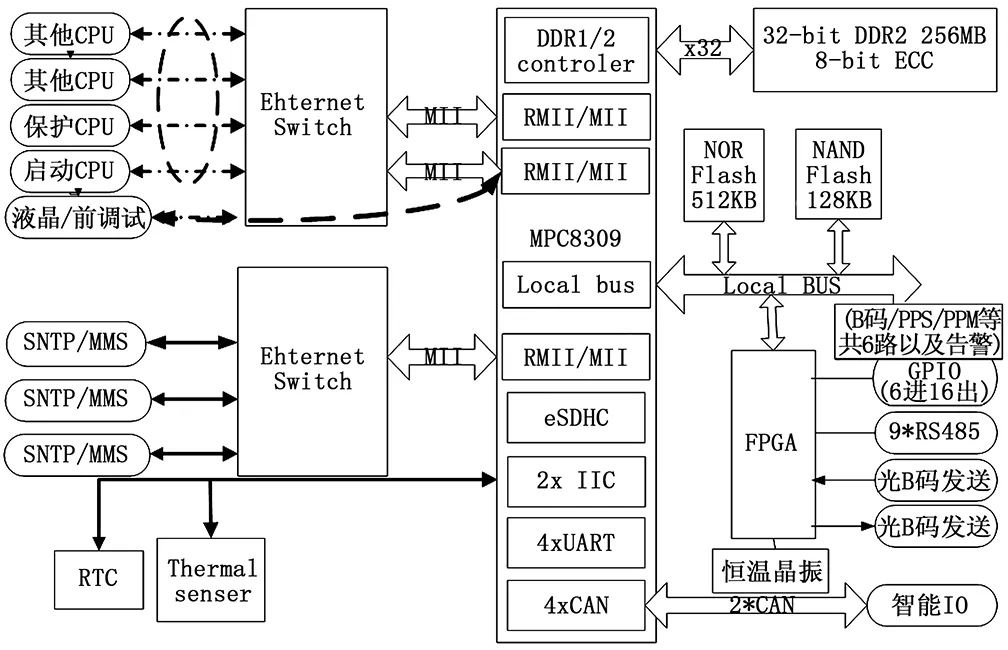

CPU模块作为核心插件,采用架构为FPGA+CPU+高精度恒温晶振的模式,其原理如图2所示。CPU采用飞思卡尔的PowerPC系列的MPC8309芯片,FPGA采用为XILNX的XC6SLX45可编程逻辑器件,接口丰富性能强大。配备鸿晔公司的高精度10 M恒温晶振JTM5035-A,日老化率小于0.2 ppb,年老化率小于50 ppb,预热期间(20分钟~2小时)误差<10 ppb。该恒温晶振经硬件电路倍频后连接FPGA,在FPGA内部采用100 MHz频率,单tick时标分辨率为10 ns,能有效保证时间精度和稳定性。

智能液晶模块负责显示时间信息,运行定值设置,SNTP定值设置等用户接口。宽电压冗余双电源支持,保证设备电源安全。输出插件包括IRIG-B码信号输出、串口时间报文输出、脉冲输出等各类时间输出信号。提供RS232、RS485、空节点、光输出等各种插件输出,输出信号和数量可配置。有效兼容各种使用场景。

图2 CPU插件硬件原理框图

2 时钟的软件设计

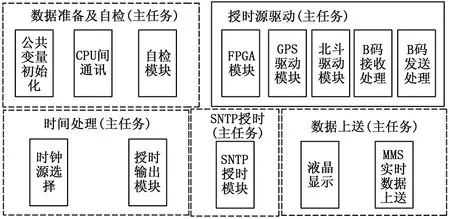

时间同步装置软件设计涉及CPU程序设计和FPGA程序设计,功能模块关系如图3所示。

CPU软件完成4个时源信息采集、自守时钟的走时、多时源判断选择、授时输出、SNTP对时服务器[5]、时间信息发送控制以及IEC61850MMS通讯信息[6]的上送等功能。

图3 软件模块关系图

FPGA负责外部接口的驱动,连接授时插件,输出插件等。FPGA和恒温晶振共同建立一个精确的32位tick计数器,利用此计数器作为本地走读的频率基础,并为各授时源PPS打高精时戳;本地时间PPS的输出由CPU发送输出预期计数值,由FPGA判断到达而产生时间脉冲。同时FPGA承担授时模块报文的接收、IRIG-B解码、PPS/PPM/PPH脉冲输出、IRIG-B发送和串口时间报文发送。

按照应用的功能,对应用层进行模块化设计。总体模块划分如图4所示。

图4 软件功能模块划分图

主要分为5个工作区:数据准备及自检、授时源驱动、时间处理、SNTP授时、数据上送。

授时源驱动负责对4个时钟源信息进行解析和存储。对于北斗和GPS模块,CPU读取FPGA程序解析的串口报文数据,报文遵循NMEA 0183“National Marine Electronics Association”(国际海洋电子协会)协议,每种报文为ASCII格式,逗号隔开数据流。报文包含定位时间、纬度、经度等信息,可解析出UTC时间和品质。同时获取FPGA所打的PPS时间戳。对于B码,则有FPGA直接解析报文和时间戳。

时间处理任务负责实现多时源选择功能,维护本地时间,同时负责维护FPGA内部建立的硬时钟,调整FPGA输出频率和相位,生成B码和串口报文数据格式。

SNTP授时负责SNTP对时服务器功能,能最多建立与250个授时客户端的连接。配合FPGA内部的硬时间,授时精度达到数据上送模块负责液晶界面的维护和IEC61850数据的上送。可以将自检信息如锁星颗数、失星状态、钟差等信息通过MMS报文输出给监控后台,满足电力系统监控的需求[7]。

各模块之间通过时间源数据进行耦合。相互之间功能独立,各模块之间由主任务循环调度。

3 关键技术

3.1 外部时源信号采集

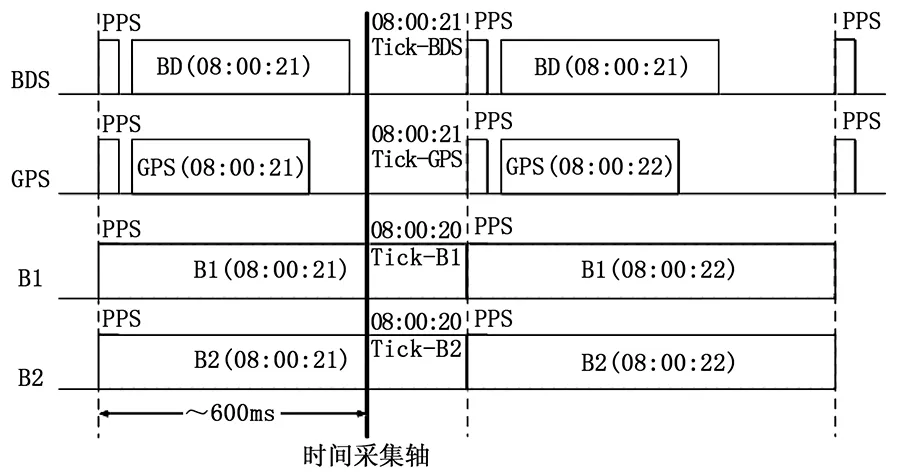

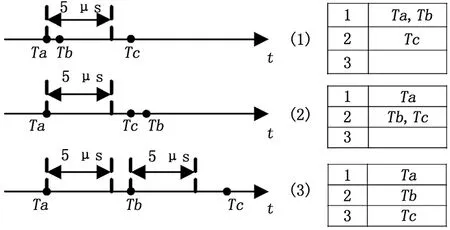

多时源信息的采集时序如图5所示。

图5 多时源时间信息的采集时序

由时间信息采集时序可知,在时间采集轴上,本次轮询读取的信息对于北斗和GPS时本秒的UTC时间和秒tick;对于B码读取的是缓存在FPGA缓存区的上一秒的时间。

时源信息的采集将对时间品质和秒脉冲有效性进行判断。若时钟源的时间品质信息有效,则计算秒脉冲间隔ΔTcur,该数值与FPGA的晶振的频率f进行横向比较,并与上次的间隔ΔTper进行纵向比较,若小于一定阈值5 μs,则认为时源有效。将有效的时间信息(年、月、日时、分、秒、Tick-PPS、ΔT)保存在CPU内存的时间信息数据结构中。

3.2 多源选择策略

在多时源选择中,共有5个时间信息参与选择,即北斗、GPS、地面有线(B1)、本地时间(即装置时间)和备钟时间(B2)[8]。其中北斗、GPS和地面有线时源称为外部时源;本文采用分组策略优先选择的多源选择策略选择正确时源。时间的选择分为2种情况:无本地时间或守时恢复时的初始化情况和时源跟随状态下的运行态情况。

3.2.1 初始化时源选择

当时间同步装置上电或守时恢复时,装置无时间信息或时间信息不准确。此时本地时间不参与多时源的选择,仅3个外部时源参与选择。

假设Ta、Tb、Tc是3个外部时源,它们的时间包括年、月、年、月、日、时、分、秒、tick-pps和ΔT,保存在时间信息数据结构。依次从3个时源选取1个,按照优先级顺序分别与其它时源求取钟差。将钟差小于5微秒的时源放在一组,不满足该条件的时源放于另一组。比较两个组中时源数目,如果前面一组时源数目多,则在该组中按优先级选取当前时源,否则选取不到当前时源。

图6 初始化时源选择分组示意图

图6(1)中选择1组中的Ta;(2)中选择2组中的Tb;(3)中无时源选择,在此情况下,如果系统还未初始化,则继续进行判别,等待初始化完成;如果系统已经初始化完成,则进入运行状态输出时间信息。

3.2.2 运行态时源选择

当时钟处于跟随状态以后,本地时钟源将参与运行时的分组策略。运行态分组时,本地时间处于最高优先级进行分组,分组以后,按照分组会形成4:0,3:1,2:2,1:1:1:1的情况。在4:0和3:1时从分组多中按照优先级选择外部时源,当为2:2时,有可能后形成(本地、GPS):(北斗、有线时源)的情况,根据北斗优先原则应跟随北斗时源。

图7 运行态时源选择分组示意图

如图7(1)选取Ta为跟随时源,图7(2)、图7(4)则固定选取北斗时源。图7(3)是1:1:1:1的情况,表明所有外部时源均不可用,则系统进入守时状态,并继续判断时源情况,直到退出1:1:1:1时在重新选择。

当选到最优时源后,产生本地时间,并使本地时间基准逼近随该时钟源的PPS上升沿时刻。输出则按照当前时源的PPS间隔信息预判本地时间的秒脉冲间隔,用tick数表示,向FPGA发送下一次秒脉冲输出的tick时刻。当FPGA的计数器到达此预判结果时,在此时刻发送秒脉冲、B码、串口报文等时间信息,从而达到授时的功能。FPGA不直接跟随时源的PPS秒脉冲,从向FPGA发送下一秒预期到FPGA产生秒脉冲,间隔100ms以上。通过此种方法,即便所选时源偶尔出现时源跳变,CPU也可以立刻判断出来,利用预判结果生成下一次秒脉冲和时间,从而保证同步时间精度和稳定性。

3.3 基于高精度恒温晶振的守时策略

当时钟失去所有有效时源时,时间同步装置将进入守时状态。时间同步装置要求装置启动2小时内要完成晶振驯服,达到1 μs/h的守时精度要求[9]。

守时时间的精度由有效秒脉冲间隔ΔT和高精度恒温晶振共同保证。CPU使用的余数均摊法生,根据最近的秒脉冲间隔ΔT生成512个秒脉冲输出队列,由FPGA循环输出,保证走时均匀准确。但是,晶体的频率受施加于它的应力的影响。温度的变化会使晶振内部应力变化[10]。实际运行通常会发生晶振预热不充分时失步的情况,晶振输出频率不稳定,而且采用的恒温晶振性能越好,体积越大,晶振的预热和驯服时间也就越长,保存的同步秒脉冲间隔ΔT不能反映实际晶振的频率变化,会使得的守精度误差增大。

本文提供一种基于恒温晶振的补偿方法,用以解决失步时在恒温晶振未充分预热而带来的守时误差较大的问题。

根据研究和实验数据得到,恒温晶振的热频特性变化特性基本上按照一定的规律变化[10],由此可通过预测晶振频率变化,进行补偿守时。具体原理分析如下:

恒温晶振提供工作频率f,FPGA利用此频率作为计数基准对同步时钟源同步信号的秒脉冲打上tick时标。如果假设N秒内的秒脉冲的tick时标为C,那么,根据CPU能够计算出恒温晶振的实际震荡频率,为:

f=C/N

(1)

当N=1时,秒脉冲间隔的tick数C即为频率。

CPU将有效秒脉冲的tick间隔值按照时间先后顺序依次存入RAM缓冲区,本实施例中,缓冲区大小设定为64。每当缓冲区满时,对缓冲区64个时间间隔进行和统计,得到β值,并存入缓冲区队列中。计算公式为:

(2)

其中,t0为恒温晶振在标称频率f0下的秒脉间隔值,即每秒的基准脉冲个数,比如:取值为99999950,ti为恒温晶振在实际频率下的每秒的脉冲个数。

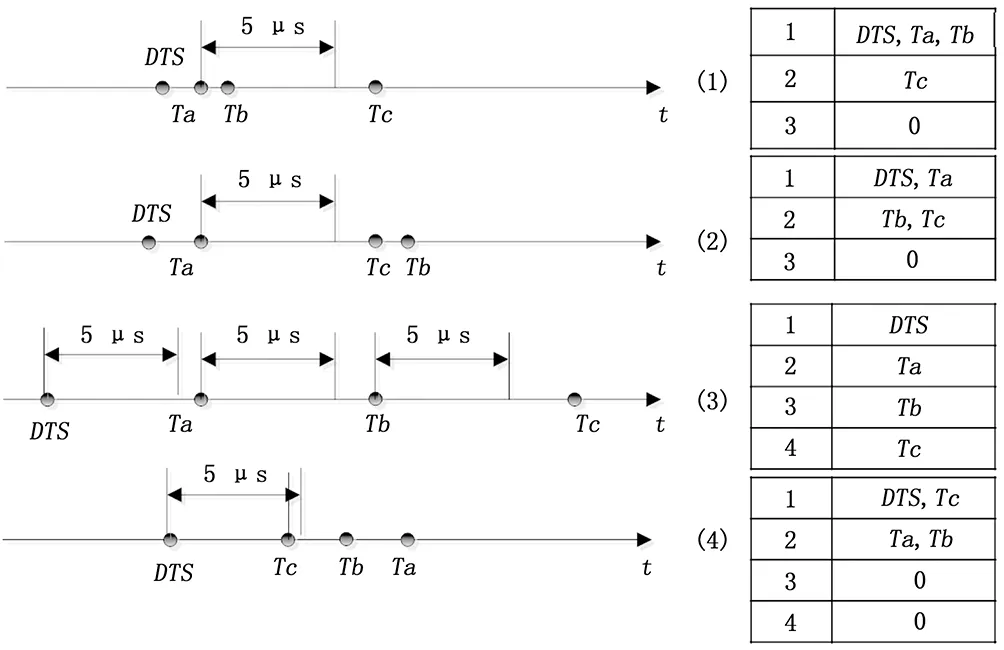

将β值依次存入缓冲区队列中后可观察到β值的变化趋势如图8所示。

图8 恒温晶振预热频率变趋势意图

因此,根据上述公式可知,f=(64β+t0)/64,故β值可以清晰的反应恒温晶振的频率变化。

通过分析恒温晶振的开机特性为:恒温晶振预热前期的频率值在一段时间内变化较大,这就是恒温晶振的开机特性,随着开机预热的时间加长,恒温晶振的频率输出将达到稳定。经过实验,对于不同的晶振,开机特性是不同的,即使是同一只晶振,重复测试结果也可能不同。但对于同一只晶振,开机时频率变化的趋势和开机特性在一定的范围内变化不大,对于实现守时补偿提供了机会。

由图8可以看出恒温晶振每64 s的tick计数随时间的变化关系。前100个周期内(100*64 s=6400 s)变化明显,表明此时晶振并未预热充分。随着时间的移动,晶振的频率变化趋于稳定,变化趋势趋于稳定。

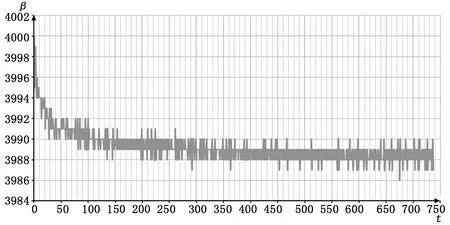

当失去外部同步时钟源时,为防止恒温晶振随机变化随机性的影响,需要对预热期间晶振频率的稳定性进行判断,仅当晶振频率变化单调才进行频率预测和调整。根据缓冲区队列中的β值从最近时间向前计算, 按照如图9所示分别求取α1、α2、α3……和φ1、φ2、φ3……。选取最近的4个φ值,分别是φ1、φ2、φ3、φ4,计算不等式(φ4-φ3)×(φ2-φ1)>0,和(φ3-φ2)×(φ2-φ1)>0>0是否成立,如果同时成立,则认为晶振频率在此时段是单调变化的。

在单调性的判断上,仅对晶振预热阶段的频率进行判断与调整,即缓冲区中至少保存有1.5小时的同步秒脉冲信息,预测守时后的频率变化的情况。若单调性成立,则按照进行后续的频率预测和补偿;如果单调性不成立,则不进行补偿。

图9 秒脉冲间隔窗口统计方法

为了消除卫星的正态分布误差,选取按照最后1024 s的秒间隔TICK值作为基准样本,即α1和α2,再进行晶振频率补偿后生成输出秒脉冲缓冲区队列数据。

补偿数据的计算方法:

f=(Δticki+αj)/N+f0

(3)

f是晶振的实际输出频率,f0是恒温晶振的标称频率。那么:

Δf=f-f0=(Δticki+αj)/N

(4)

因此,只要Δticki选择合理,便可以得到准确的实际输出频率。

通过实验如下补偿值计算方法,能够使输出的频率与恒温晶振的实际输出频率的误差最小,可以保证时间同步装置的守时精度,定义i=1、2、……

Δtick1=Δtick2=(φ1-φ4)/2

(5)

……

Δtick2i+1=Δtick2i+2=Δtick2i-1/2

(6)

Δtick对应的时间段与α值对应的时间段相等,均是512秒。Δtick1是最近512秒对应的补偿值,Δtick2是Δtick1前512秒对应的补偿值,其他的以此类推。另外,当Δtick=1时,停止补偿。

得到Δtick后,按照补偿后Δtick2i+1+α1和Δtick2i+2+α2的值生成两组512个tick计数器间隔,并按照计数器循环输出秒脉冲。

本实施例中,采用余数均摊方法生成秒脉冲输出序列利用余数均摊方法生成的秒脉冲数组相对于原始采集的512个tick值更加均匀。

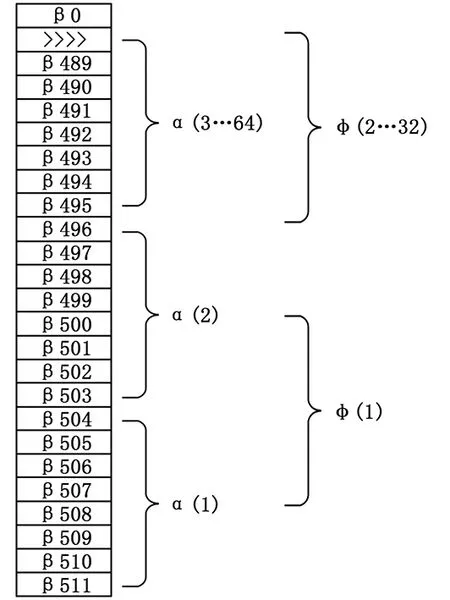

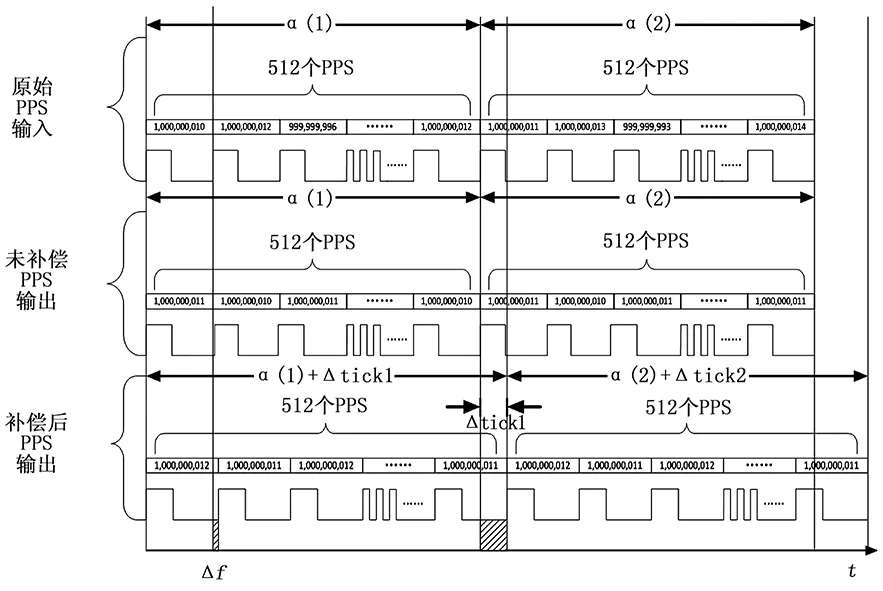

图10 补偿对比效果图

图10是未补偿和补偿后输出PPS的比较图。由图可见,未补偿PPS序列和补偿后的PPS在512个PPS中总和偏差Δtick(如图10阴影部分),该偏差Δtick被平均分配到单个PPS输出的小阴影部分。补偿值Δtick1纠正了由于晶振频率变化所引起的频率误差Δf,从而减少了输出512个PPS所引起的时间误差。

4 实验结果

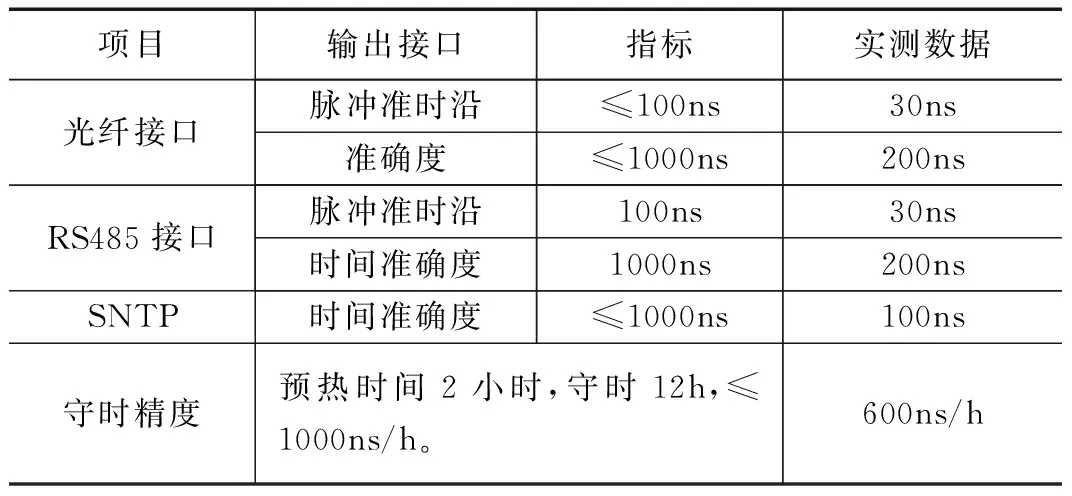

为证明利用本文设计方法所获得的时间同步装置的实际有效性,对装置的光纤接口、RS485接口、SNTP以及守时精度4个项目进行实际测试,测试结果如表1所示。

由表1可以看出,运用本文设计方法的时间同步装置实际测得光纤接口的脉冲准时沿为30 ns,准确度为200 ns,远小于国网检测指标的100 ns和1000 ns;RS485接口的脉冲准时沿和时间准确度实测结果同光纤接口的实测结果相同,同样小于国网的检测指标;SNTP项目在采用了本文设计方法的时间同步装置后实际测得时间准确度达到100 ns,比国网指标的1000 ns少了900 ns;国网指标要求时间同步装置的守时精度为1000 ns/h以下,采用本文设计方法的时间同步装置实测结果为600 ns/h,符合国网指标的要求。由此,利用本文设计方法的时间同步装置已顺利通过2017年的国网检测,各性能参数达到或优于预期。

表1 时间同步装置测试结果

5 结语

本文在设计之初便考虑到时间精度和稳定性问题,在硬件方面,考虑到时间准确性方面,对脉冲准时沿的实时性要求很高,单纯靠CPU难达到要求,所以利用FPGA的实时性和恒温晶振的稳定性,外加CPU的强大数据处理能力,构建了一个可靠的硬件平台。

在软件设计上采用基于优先级分组策略的多源选择算法、守时算法、晶振频率预测补偿算法等,充分利用卫星、CPU、恒温晶振和FPGA形成精确稳定的授时平台。实验证实,本文方法可以满足具体指标的要求,具有一定的推广价值和实用价值。