片间高速图像传输系统的设计与实现

任 强,姚远程,秦明伟

(1.西南科技大学信息工程学院,四川 绵阳 621010;2.特殊环境机器人技术四川省重点实验室,四川 绵阳 621010)

0 引言

随着视觉测量技术的发展,高速工业相机以其高帧率和高分辨率,在工业生产中的应用越来越广,因此产生了大量的图像数据。现场可编程门阵列(field programmable gate array,FPGA)作为一项越来越成熟的技术,以其并行性以及灵活性,被广泛应用于图像采集、传输以及处理[1-2]。在大型视觉测量和图像处理系统中,常常需要多个FPGA协同工作,所以FPGA之间的图像数据传输成为视觉测量和图像处理系统发展的难点和瓶颈[3-4]。Xilinx目前提供了4种不同速率的高速串行收发器[5-7]。

针对在片间传输高速图像数据和帧控制信号的问题,研发了一种高吞吐率、低错误率、高抗干扰能力、低I/O资源占用率的片间图像数据传输解决方案。该解决方案可广泛应用于视觉测量系统和图像处理系统。

1 GTH收发器

高速吉比特串行(GTH)收发器是吉比特收发器中的一种,是FPGA中高度可配置以及高度集成的可编程逻辑资源。GTH收发器具有很高的可扩展性,可支持PCI-e、10GBASE-R、Aurora等多种协议[8]。GTH收发器支持500 Mbit/s~11.3 Gbit/s的线速率,支持8B/10B、64B/66B、64B/67B等多种线路编码,支持时钟矫正以及通道绑定等多种特性。Virtex-7 GTH收发器的TX发送端和RX接收端功能独立,且均由物理媒介适配层(physical media attachment,PMA)和物理编码子层(physical coding sublayer,PCS)组成。PMA内部集成了高速串并转换、预加重、接收均衡、时钟发生器及时钟恢复等功能电路。PCS内部集成了8B/10B编解码、弹性缓冲区、通道绑定和时钟修正等专用电路模块[5]。

2 Aurora协议

Aurora协议是由Xilinx公司提出的、开放的、免费的、轻量级的可配置数据链路层协议,主要用于在多个高速串行通道之间进行点对点传输,具有高速数据传输和简单易用的特点[9]。

Aurora协议可为私有上层协议或标准上层协议提供透明接口的串行互联协议,允许任何数据分组通过Aurora协议封装,并在芯片间、电路板间,甚至机箱之间传输。采用Aurora协议传输数据时,用户数据在一个Aurora通道上传输,跨过通道通信的设备成为通道对。Aurora通道包含一个或多个Aurora链路,每个Aurora链路是一个全双工或单工的串行数据连接,称为“弄”。如果使用的是GTH收发器,这个“弄”可实现500 Mbit/s~11.3 Gbit/s的数据传输,最多可连接16个“弄”[5]。

Aurora通道具有如下特性。

①数据以帧的形式在通道中传输。

②帧和控制信息共享通道,控制信息包括流控信息、时钟补偿序列和空闲信息。

③高度可自定义的帧长度和帧格式。

④Aurora协议中的帧不必全部连续,可以被流控信息和空闲信息打断。

⑤支持8B/10B编码和64B/66B编码。

3 CXP图像传输协议

CXP图像传输协议在本文中是指128 bit数据位宽的图像传输协议,其中包括了时钟信号、128 bit的图像数据信号、传输有效指示信号以及8 bit的帧控制信号。CXP协议信号定义如表1所示。

表1 CXP协议信号定义

4 片间图像传输模块设计

片间图像传输模块名称为CXP_Transiver,模块内部集成了Xilinx提供的Aurora core。该模块的特性如下。

①实现透明全双工传输。

②支持最大吞吐率为32 Gbit/s,平均吞吐率为20 Gbit/s。

③实现链路的8B/10B编码。

④可配置的链路线速率,单链路速率最高可达6.25 Gbit/s。

⑤用户接口时钟最大可支持250 MHz。

⑥可移植性强,适用于多种收发器。

⑦可支持图像数据位宽为32~128 bit。

4.1 模块的架构设计

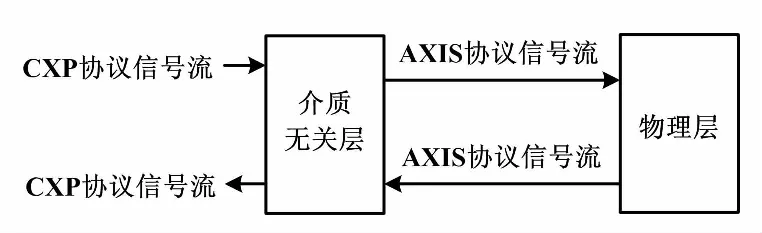

CXP_ transceiver模块结构如图1所示。

图1 CXP_ transceiver模块结构框图

模块分为两层,分别是介质无关层(media independent interface,MII)和物理层(physical layer,PHY)[5]。

介质无关层将CXP协议信号转换为AXIS协议信号。介质无关层不考虑任何底层数据的传输方式问题,底层可以采用任何物理介质进行数据传输。

物理层为AXIS协议提供透明数据通路。物理层不考虑任何上层的数据内容问题,仅采用高速串行接口为AXIS协议提供透明数据通路。

两层组合共同完成了CXP协议的透明数据通路。两层均采用模块化设计,使用标准接口。

4.2 物理层设计

物理层功能由Aurora协议完成。Aurora协议由Xilinx公司提供的Aurora 8B/10B core实现。Aurora 8B/10B core可以自动地实例化最多16个GTH收发器通道、提供8B/10B的链路编码、支持单工和全双工的工作方式、支持16 bit和32 bit的循环冗余校验并且可以在任意时刻暂停数据流传输。此外,Aurora 8B/10B core具有较低的资源消耗。

Aurora core主要参数配置如表2所示。

表2 Aurora core主要参数配置

Aurora 8B/10B core的主要功能模块如下。

①Lane Logic。每个GTP、GTX或者GTH收发器都被Lane Logic模块的实例化所驱动,每个收发器都会实例化一个Lane Logic模块。该模块处理控制字符的编码和解码以及错误校验。

②Global Logic。Global Logic模块完成了通道绑定和相位矫正。工作期间,该模块将产生Aurora所需的随机空闲字符,并监控所有Lane Logic模块的错误。

③RX User Interface。AXI4-Stream RX用户端口将数据从高速收发器通道搬移到用户接口,并实现流量控制。

④TX User Interface。AXI4-Stream TX用户接口将数据从用户接口搬移到高速收发器通道,并实现流量控制。此外,该模块还控制周期性的时钟补偿序列的传输。

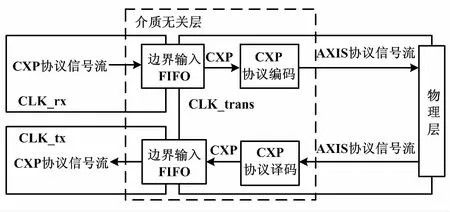

4.3 介质无关层设计

介质无关层结构如图2所示。

图2 介质无关层结构图

CXP协议包括了128 bit数据以及8 bit控制。为了便于物理层传输,介质无关层需要将CXP协议信号封装为128 bit的AXIS协议。在理想状态下,CXP协议能够满速率运行,即128 bit数据持续有效。在这个情况下,在同样频率的时钟下操作,无法将控制信号并入128 bit数据流。因此,介质无关层内部运行在比CLK_tx与CLK_rx更高频率的CLK_trans上。各时钟域间的信号传输以异步先进先出(first in first out,FIFO)进行隔离。

介质无关层内部的CXP协议编码模块(CXP_Encoding)及CXP协议译码模块(CXP_Decoding)分别完成将CXP协议编码为AXIS协议信号和将AXIS协议解码为CXP协议。当CXP协议中的控制信号为低电平时,输入的CXP协议数据直接转换为AXIS协议数据。当CXP协议中有控制信号为高电平时,1个时钟周期的CXP协议信号转换为2个时钟周期的AXIS协议数据。AXIS协议数据信号的第一个时钟周期为控制信令,包含了CXP当前的控制信号,与用于识别控制信号的标记CMD_TAG,第二个时钟周期的AXIS协议数据为CXP协议数据。

4.3.1 CXP边界FIFO

CXP 边界FIFO用于跨时钟域传输CXP协议信号,在Xilinx IP Native FIFO上进行了简单的重封装,以适应CXP协议。CXP-FIFO模块电路图如图3所示。

图3 CXP-FIFO模块电路图

CXP协议的图像数据信号和帧控制信号并行作为数据送入FIFO,读取时从FIFO中并行取出。CXP-FIFO的Ready与Valid信号与CXP协议中的信号一致,可以直接连接至符合CXP协议的模块。

4.3.2 CXP协议编码电路

CXP协议编码电路主要分为两个部分,即DataTransform与ControlUnit。

CXP Encoding模块电路如图4所示。

图4 CXP Encoding模块电路

DataTransform主要完成将输入数据转换为输出数据,在内部形成了以下三种数据。

①CXP协议中的图像数据。

②低64位与CXP协议中的输入数据的低64位相同,高64位为CMD_TAG-1。

③低8位为CXP的8 bit控制信号,第9位为是否转义的指示信号,第10~64位为0,高64位为CMD_TAG。

DataTransform以Trans_meaning信号与cxp_event信号为指示,选择其中一种数据。

Trans_meaning高电平有效,用于判断当前CXP输入数据的高64位是否与预设的CMD_TAG一致。若与CMD_TAG一致,为避免接收端误将该数据误译为控制信号,需要进行转义,将高64位减1,即CMD_TAG-1,即输出数据类型(2)。Cxp_evnent高电平有效,指示了当前CXP输入是否有控制信号为高电平。当有控制信号输入时,Encoding模块需要发出控制信号,即输出数据类型(3)。在其他情况下,将会输出数据类型(1)。

DataTransform中,Mapping的映射关系见上文提到的模块数据结构设计。Trans_meaning信号由Trans_Mean_Monitor模块产生。该模块是一个64 bit组合逻辑比较器。当输入的CXP协议信号中数据信号的高64位与CMD_TAG一致时,则输出高电平,否则输出低电平。

Control_Unit负责Encoding的时序控制,Control_Unit在CXP输入控制信号中有高电平时,阻断数据从CXP到AXIS的传输。当CXP输入控制信号都为低电平时,允许CXP与AXIS直接握手,直接将CXP数据传输至AXIS。

Event_Monitor是一个多输入或门,当sol、sop、eol和eop有信号为高时,输出高电平,否则输出低电平。Cmd_operation_done_n复位时为高电平,当有控制信号为高时,Event_Monitor与Cmd_operation_done_n都为高电平,则cxp_event为1。Cxp_event取反后将rx_data_ready置0,阻断了CXP协议信号的传输。当检测到本次控制帧传输完成后,Cmd_operation_done_n被置1,撤销cxp_event。CXP协议端继续向AXIS协议端传输数据。

4.3.3 CXP协议解码电路

CXP协议解码电路主要分为两个部分,即DataTransform与ControlUnit。

CXP Decording模块电路如图5所示。

图5 CXP Decoding模块电路图

CXP Decoding模块主要分为Data Transform和Control Unit两个部分。

DataTransform依据cxp_event信号进行工作。当cxp_event信号为高时,BUF读取AXIS data的低9位信号;当cxp_event为低时,BUF读取0。BUF是一组受cxp_event控制的触发器。

BUF的低8位输出至Tx_control,最高位是转义指示信号trans_meaning,控制MUX选择是传输原数据还是将被转义的原数据逆转义。

Control Unit用于检测AXIS协议端传输来的CMD控制信令。当有控制信令时,cxp_event为高,控制BUF读取控制信号,将Tx_data_valid拉低阻断CXP信号输出,将AXIS_data_ready信号拉高,允许读取该控制信令。当检测当前控制信令传输完成后,将cxp_event拉低,撤销此次控制信令处理。

Control Unit中的Event Monitor是一个64位组合逻辑比较器,当AXIS_data的高64位与CMD_TAG相等时,输出高电平。

5 系统测试与分析

5.1 片间图像数据传输系统架构

在单个FPGA上仿真的片间图像传输系统结构如图6所示。FPGA1和FPGA2为对称的架构,在FPGA1和FPGA2之间是模拟的物理链路。FPGA1和FPGA2都有数据源CXP source、数据采集模块CXP Endpoint以及数据对比模块CXP Verifier。

图6 片间图像传输系统结构图

CXP Source用于产生符合CXP协议的信号,模拟了利用CXP Transceiver进行传输的Tx系统。为了保证仿真的科学性,CXP Source输出的数据是由4个32 bit序列发生器生成的伪随机数。产生的图像的行场大小均为可配置参数。产生的valid信号有2种模式,由rand_valid信号控制。当rand_valid信号为0时,输出的valid信号恒为1;当rand_valid信号为1时,输出的valid信号为服从均匀分布的随机数。该模块还有一个trans_mean_valid控制信号。当该信号为1时,CXP Source会周期性地产生需要被转义的数据。该周期长度可参数化配置。

CXP Endpoint持续不断地读取CXP信号,模拟了利用CXP Transiver进行传输的Rx系统。CXP Endpoint简单地将CXP_ready信号拉高,不断读取用户接口端信号,并将其余信号使用“keep true”方式声明,保证信号不在综合时被优化掉;此外,其未对输入信号作任何处理。

CXP Verifier模块用于监听两个CXP信号线上的信号是否完全一致,以验证CXP Transiver的传输正确性。CXP Verifier会将监听到的信号分别存入FIFO中。当两侧FIFO都不为空时,将会取出数据进行比较。传输异常指示信号定义如表3所示。信号反映了CXP Verifier模块对数据传输情况的监视结果。

表3 传输异常指示信号定义

5.2 仿真结果及分析

本次仿真测试的软件平台为Xilinx公司推出的ViVaDo 2016.4,仿真工具为ViVaDo自带的仿真软件Isim[9-11]。

FPGA1仿真结果表明,total_num一共发送了6 825个128 bit即873 600 bit数据。err_occur、overflow_occur、underflow_occur一直为低电平并且err_num、overflow_ num、underflow_ num这3个计数器一直为0,说明没有边界FIFO溢出和传输错误的情况出现。

FPGA2上的仿真结果与FPGA1相同,因为FPGA1

与FPGA2是完全对称的结构,所以关于输入输出的图像数据可参考FPGA1的仿真结果。total_num一共发送了873 600 bit数据,err_occur、overflow_occur、underflow_occur一直为低电平并且err_num、overflow_ num、underflow_ num这三个计数器一直为0,说明没有边界FIFO溢出和传输错误的情况出现。

通过对两片FPGA传输情况的仿真结果可知,该高速图像传输模块能够正常工作,实现片间高速图像数据的正确传输。输入数据同步时钟可达250 MHz,数据位宽可达128 bit,外加8 bit帧控制信号。

6 结束语

本文所设计的基于FPGA的片间高速图像传输系统,完成了片间的高速图像数据传输。设计了图像数据和帧控制信号的编解码、跨时钟域处理等电路,并对Aurora 8B/10B core进行调用和封装。系统实现了符合CXP协议的图像数据传输,同步时钟为250 MHz,图像数据位宽为128 bit,帧控制信号为8 bit。系统提供了一种新的片间传输图像数据的解决方案。因为底层传输由GTH收发器实现,故该设计具有高抗干扰性,占用较少的I/O资源,提高了成本效益和图像传输的吞吐率,具有很高的实用价值。