具有小步进和低相噪的频率合成器的设计

蒋佳男 马忠松

摘 要: 为了设计具有小步进和低相噪的频率合成器,分析了直接式、锁相式和直接数字式频率合成器的优缺点,以及结合锁相环与直接数字式频率合成器的多种设计方案。在此基础上,使用DDS激励PLL的频率合成技术,设计了满足多种指标的频率合成器。该合成器的步进是1 Hz,当频率是10 kHz时,合成器的相位噪声低于-90 dBc/Hz,同时其输出带宽较大。

关键词: 频率合成; 锁相环; 低相噪; 小步进; 频率合成器; 杂散

中图分类号: TN73?34; TN74 文献标识码: A 文章编号: 1004?373X(2018)16?0009?04

Abstract: A frequency synthesizer with small step and low phase noise is designed by analyzing the advantages and disadvantages of direct, phase?locked and direct digital synthesizers, and combining multiple design schemes of phase?locked loop and direct digital synthesizers. On this basis, the frequency synthesis technology using DDS to stimulate PLL is adopted to design the frequency synthesizer that can satisfy various indicators. The step of the synthesizer is 1 Hz, and when the frequency is 10 kHz, the phase noise of the synthesizer is lower than -90 dBc/Hz, and the output bandwidth of the synthesizer is relatively large.

Keywords: frequency synthesis; phase?locked loop; low phase noise; small step; synthesizer; stray

0 引 言

在现代电子系统中,频率合成器是通信、雷达和电子对抗等设备的重要组成部分,其输出信号的稳定与准确程度直接影响通信、电子对抗等系统的整体性能[1?3]。所以,如何设计具有高稳定性和高准确度的频率合成器始终是学术界研究的热点内容。一般而言,频率合成器是一种使用标准信号和多种技术手段生成大量离散频率信号的电子设备,常用于微波扫频中频率参考信号的生成[4?6]。

根据频率合成技术的实现方式,频率合成器可分为直接式、锁相式和直接数字式频率合成器[7?10]。其中,直接式频率合成器也被称为分频?混频?倍频式频率合成器。此设备是使用晶体震荡的信号产生目标频率信号,该技术必须保持所有晶体的频率稳定性和准确度,故生產成本较高。锁相式(Phase Locked Loop,PLL)频率合成器是通过比较晶体信号与振荡电路信号的相位,再调整振荡电路信号的相位,以减少两种信号的相位差,从而尽量使振荡电路信号的输出频率与晶体信号保持一致。锁相式频率合成技术出现于20世纪50年代,其优点是性能稳定,电路结构简单,缺点是环路的响应时间较慢。直接数字式(Direct Digital Synthesizer,DDS)频率合成器是直接使用抽样和数字化等,数字计算技术产生合成频率。该技术的优点是输出信号相位是连续的,噪声比较低,且设备的体积小,信号分辨率与转换速度较高;缺点是输出信号的杂散多,输出频率较窄。

基于这三种频率合成器的研究背景,为了设计具有小步进、低相噪、低杂散和宽带输出的频率合成器,本文综合使用锁相式(PLL)和直接数字式(DDS)频率合成器,规避这两种实现技术的缺点,最终设计与实现了兼具两种优点的频率合成器。

1 DDS+PLL频率合成器

通过对DDS频率合成器进行研究分析可知,其优点在于信号分辨率高,频率转换时间少;缺点在于信号的频谱存在诸多杂散分量,从而导致信号的频段难以满足高频输出的要求。同样,PLL频率合成器的优点在于输出频率较高且频谱纯净;缺点在于频率转换时间过长,即电路的响应仅可以达到微秒级。由频率合成器的优缺点分析可知,DDS和PPL频率合成器的优缺点是互补的,结合这两种频率合成器的设计可以得到一种混合使用的频率合成器。该种频率合成器兼具这两种设备的优点,而不存在两种频率合成器的缺点。

1.1 DDS激励PLL的频率合成技术

DDS激励PLL的频率合成技术是使用DDS和PLL混合方式的频率合成器,常被用于宽带雷达信号的生成过程。其电路结构见图1。

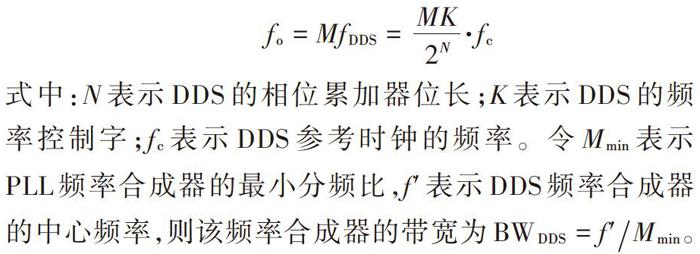

由于带通滤波器(BPF)和鉴相器之间有一个硬限幅电路,故该方案克服了DDS频率合成器的杂散较小的缺点,其最终输出结果是:

式中:[N]表示DDS的相位累加器位长;[K]表示DDS的频率控制字;[fc]表示DDS参考时钟的频率。令[Mmin]表示PLL频率合成器的最小分频比,[f′]表示DDS频率合成器的中心频率,则该频率合成器的带宽为[BWDDS=f′Mmin]。

1.2 环外混频的DDS+PLL频率合成技术

在环外混频的DDS+PLL频率合成技术中,DDS和PLL频率合成器是两个独立的电路结构。这两个电路结构的信号由混频器处理之后输出,其电路结构如图2所示。

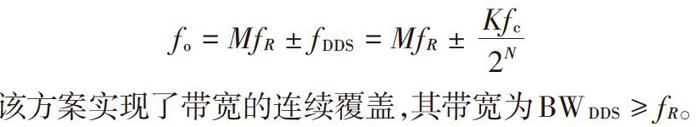

该方案的频率输出结果是:

该方案实现了带宽的连续覆盖,其带宽为[BWDDS≥fR]。

1.3 环内混频的DDS+PLL频率合成技术

该方案将混频器加入了锁相环的电路中,进一步优化了方案的频率合成效率。其电路结构如图3所示。

2 小步进低相噪低杂散频率合成方案

在Ku波段的频率合成方案设计过程中,其设计难点在于同时实现多项指标,这些指标包括输出频率的范围为12.55~13.85 GHz;输出功率的大小是12 dBm;频率步进的大小为1 Hz;杂散小于-60 dBc;当信号频率是10 Hz时,相位噪声小于-70 dBc/Hz;当频率是100 Hz时,相位噪声小于-78 dBc/Hz;当频率是1 kHz时,相位噪声小于-84 dBc/Hz;当频率是10 kHz时,相位噪声小于-92 dBc/Hz;当频率是100 kHz时,相位噪声小于-100 dBc/Hz;输入参考频率的大小是10 MHz。为了设计达到多个参数的频率合成器,本文使用了DDS激励PLL的频率合成技术。同时与PDRO进行混频,得到了Ku波段的频率输出,完成了具有小步进和低相噪的频率合成器的设计。

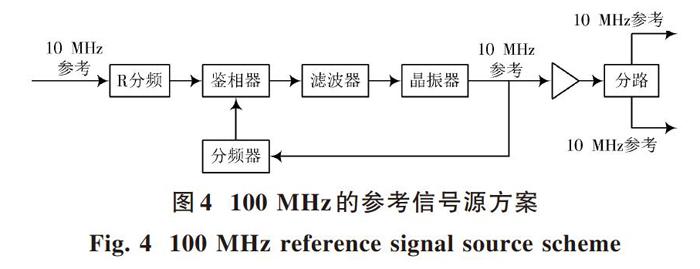

2.1 参考信号源的设计方案

因系统的输入参考频率是10 MHz,且为了减小相位噪声,本振锁相环的参考源采用高鉴相频率。本系统使用的鉴相频率是100 MHz,故系统必须使用倍频器将输入的10 MHz放大到100 MHz,但此时相位噪声的指标会恶化20 dB。为了降低这一指标,使用锁相技术,由此既降低了相位噪声,同时也提高了100 MHz晶体源的性能。

其实现框架如图4所示。

2.2 本振的设计方案

为了实现小步进的指标,该系统的本振一般会使用DDS或小数分频锁相环实现。因小数分频锁相环可以控制的最小步进单位是kHz,难以满足本文的设计要求。所以,本系统的本振使用DDS技术实现1 Hz的频率步进。此外,本文使用了锁相式频率合成技术,完成了1.5 GHz的宽带输出,其具体方法是利用宽带压控振荡器输出1.5 GHz的频率。该方法的优点是电路实现相对简单,可以将电路设备小型化;其缺点是该振荡器的驱动只能使用有缘环路,而在该过程中会产生一些噪声。由于本系统的模块化和规范化的要求,文中使用了此方法进行宽带输出。

综合上面分析的内容可知,系统的本振需要使用DDS+PLL的电路结构来实现。由上文的分析可知,3种实现方案均可满足系统的步进和输出频点的设计要求。但由于环内与环外混频的DDS+PLL频率合成技术均无法输出满足系统要求的带宽,故文中选用DDS激励PLL的频率合成技术作为本振的实现方案。需要指出的是,第1.1节介绍的频率合成技术的输出信号在倍频的作用下,频率达到Ku波段。在此过程中,信号的相位噪声将大量增加,故本振的电路还需要加入变频处理电路。在本文中,由于Ku波段的PDRO具有相位噪声低的优点。所以,本振变频选用了PDRO作为电路中的高频段单频点本振。在本振的设计方案中,DDS时钟由独立的PLL电路提供,PPL的输出信号在四分频的作用下输入DDS。同时经过频率为100 MHz分频PLL的作用,提供了25 MHz的参考时钟。该设计方案可以减少DDS的杂散指标,其具体实现框架如图5所示。

3 性能分析

在完成频率合成器的设计之后,文中还需要对该合成器的指标进行具体分析,确定该合成器是否达到设计要求。

3.1 步进分析

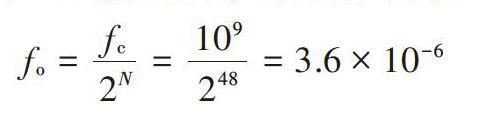

在本系统的设计中,频率合成器的步进是1 Hz。在实际的系统中,DDS实现了这一功能。若参考时钟的大小为1 GHz,则DDS输出频率的分辨率为:

这一结果意味着,即使PLL在进行40倍频之后,该频率分辨率仍可满足系统的步进要求。

3.2 相位噪声分析

因本系统使用了DDS激励PLL的频率合成技术,故文中需要反推混频器前输入信号的相位噪声。同时考虑倍频所带来的相位噪声的恶化情况,再反推DDS输出相位噪声的情况。经过考虑参考时钟、四分频和鉴相器的多重作用之后,最终可得到系统的相位噪声分配。鉴于文章的篇幅,其具体计算过程不再列出,计算结果见表1。

表中的最后一列就是该系统所达到的相位噪声的计算结果,其完全满足系统的设计要求。

4 结 语

随着卫星通信研究的不断深入,地面基站中Ku波段上变频设备的设计受到广泛的关注。本文基于Ku波段的变频设备系统设计要求,對小步进和低相噪的频率合成器进行深入的研究,并设计得到了满足各种指标要求的Ku波段的频率合成器。经过分析,该频率合成器符合系统的设计要求,且具有较高的理论价值与实际意义。

参考文献

[1] 周叶华,叶宝盛,程明,等.一种高频谱纯度的C频段宽带频率合成器设计[J].电讯技术,2018,58(2):219?224.

ZHOU Yehua, YE Baosheng, CHENG Ming, et al. Design of a high spectral purity C?band frequency synthesizer [J]. Telecommunication engineering, 2018, 58(2): 219?224.

[2] 邓迅,石玉,张钰英.基于DDS的C波段宽带小步进低相噪频率源的设计与实现[J].磁性材料及器件,2018,49(1):43?46.

DENG Xun, SHI Yu, ZHANG Yuying. Design of C?band wide band small step and low phase noise frequency source based on DDS [J]. Journal of magnetic materials and devices, 2018, 49(1): 43?46.

[3] 张兰,刘玉宝,吴国乔,等.基于HMC703的宽带低相噪低杂散频率合成器设计[J].现代电子技术,2014,37(1):93?95.

ZHANG Lan, LIU Yubao, WU Guoqiao, et al. Design of HMC703?based broadband frequency synthesizer with low phase noise and low spurious [J]. Modern electronics technique, 2014, 37(1): 93?95.

[4] 周彪,胡丹,李丽,等.S频段小型化低相噪倍频器设计[J].通讯世界,2017(15):13?14.

ZHOU Biao, HU Dan, LI Li, et al. Design of S?band miniature low phase noise frequency multiplier [J]. Telecom world, 2017(15): 13?14.

[5] 李海华.小步进、低相噪频率合成器的设计与实现[D].武汉:华中科技大学,2016.

LI Haihua. Design and implementation of small step and low phase noise frequency synthesizer [D]. Wuhan: Huazhong University of Science and Technology, 2016.

[6] 钱渊源.基于AD9914的C波段频率合成器的研究[D].南京:南京理工大学,2016.

QIAN Yuanyuan. Research on C band frequency synthesizer based on AD9914 [D]. Nanjing: Nanjing University of Science and Technology, 2016.

[7] 朱英超.基于微波介电陶瓷的X波段取样锁相介质振荡器[D].成都:电子科技大学,2016.

ZHU Yingchao. X band sampling phase locked dielectric oscillator based on microwave dielectric ceramics [D]. Chengdu: University of Electronic Science and Technology of China, 2016.

[8] 郄锦辉,舒燕,王亚洲.低相噪低杂散C波段频率合成器的设计[J].计算机与网络,2011,37(10):48?50.

QIE Jinhui, SHU Yan, WANG Yazhou. Design on C?band frequency synthesizer with low phase noise and spur reduction [J]. Computer & network, 2011, 37(10): 48?50.

[9] 王川宇,潘碑,丁玉宁.X波段低相噪细步进频率合成器的研制[J].固体电子学研究与进展,2014,34(1):56?59.

WANG Chuanyu, PAN Bei, DING Yuning. Development of X?band low phase noise and narrow resolution frequency synthesizer [J]. Research & progress of SSE, 2014, 34(1): 56?59.

[10] 虞洋华.宽带低杂散S波段下变频组件研究[D].南京:南京理工大学,2016.

YU Yanghua. Research on conversion module under broadband low spurious S band [D]. Nanjing: Nanjing University of Science and Technology, 2016.