Xilinx Virtex5 FPGA配置Flash的通用访问方法研究

中国空空导弹研究院 樊宏伦

引言

FPGA(现场可编程门阵列)由于其资源丰富、设计周期短和风险小、使用灵活等优点,已广泛应用于信号处理和控制领域。FPGA大多采用SRAM工艺,掉电后内部配置数据丢失,再次上电后需要重新对其进行配置,因此在FPGA外部多采用非易失性存储器(称为FPGA的配置PROM或配置Flash)来存储配置数据以方便每次加电后对其进行自动配置。

在系统设计中,经常会出现应用程序需要存储部分非易失性数据的情况,受空间和成本限制,我们不太可能在电路设计中增加额外的外部存储器。由于选用的配置Flash的存储容量往往大于FPGA配置文件的大小,我们可利用配置Flash的剩余空间来存储数据以达到节省电路板空间和成本的目的。

本文以Xilinx Virtex5 XC5VLX110 FPGA及其配置Flash XCF128X为例,介绍了FPGA配置完成后对Flash的读电子签名、总线读写、块擦除等操作,并通过Chipscope工具进行了在线验证,为后续应用提供了设计依据。

1.硬件设计

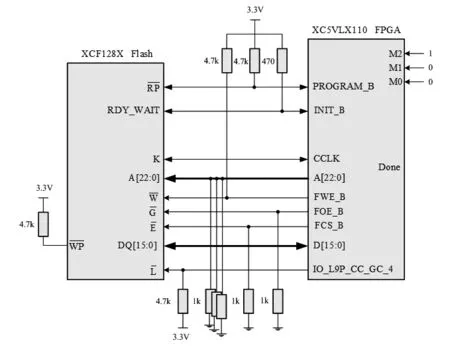

XCF128X是一款专门为Vitrex5系列FPGA配置设计的Flash,其采用低功耗CMOS NOR-Flash工艺,容量为128Mb。XC5VLX110 FPGA采用XCF128X作为配置Flash的电路如图1所示。本文以主SelectMap模式为例介绍FPGA配置完成后对Flash的访问操作,其它配置模式与此类似,不再赘述。在主SelectMap配置模式下地址总线23位、数据总线16位,配置时钟由FPGA的CCLK管脚提供,CCLK时钟频率可在ISE开发环境的配置选项中的“配置速率”(-g Con figRate)中进行设置。

图1 FPGA主SelectMap配置电路

XC5VLX110 FPGA的上电配置过程如下:

上电,FPGA清除内部配置存储器,将INIT_B管脚驱动为低电平(对应Flash的RP管脚为低进行复位);在复位时Flash将其RDY_WAIT管脚驱动为低电平(对应FPGA PROGRAM_B管脚为低);

FPGA和Flash分别释放各自的INIT_B管脚和RDY_WAIT管脚,外部上拉电阻将INIT_B和RDY_WAIT(PROGRAM_B)分别拉为高电平;

在INIT_B上升沿采样M2:M0管脚,确定其配置模式为主SelectMap配置模式;

Flash初始读地址由地址总线A[22:0]上的下拉电阻确定为0x000000,Flash将初始读地址锁存到内部地址计数器,输出数据总线DQ[15:0]上的16位配置数据;

配置数据在CCLK时钟下被同步送到FPGA中,然后Flash增加其内部地址计数器,并输出数据总线DQ[15:0]上下一个16位置配置数据到FPGA,依次类推;

配置成功后,FPGA将Done信号驱动为高电平。

2.Flash访问方法介绍

FPGA配置完成后,其部分配置管脚可以被释放为通用I/O,如表1所示。设计人员可以根据Flash操作时序,在FPGA中编写VHDL代码,同时进行管脚约束后对Flash进行相应访问。

表1 配置完成后释放为通用I/O的管脚

由于CCLK管脚并没有被释放为通用I/O,如果在FPGA配置完成后需要对Flash进行同步读操作,可以通过例化STARTUP_VIRTEX5原语实现对CCLK的控制。本文对Flash进行异步读操作,不需要对此原语进行例化。

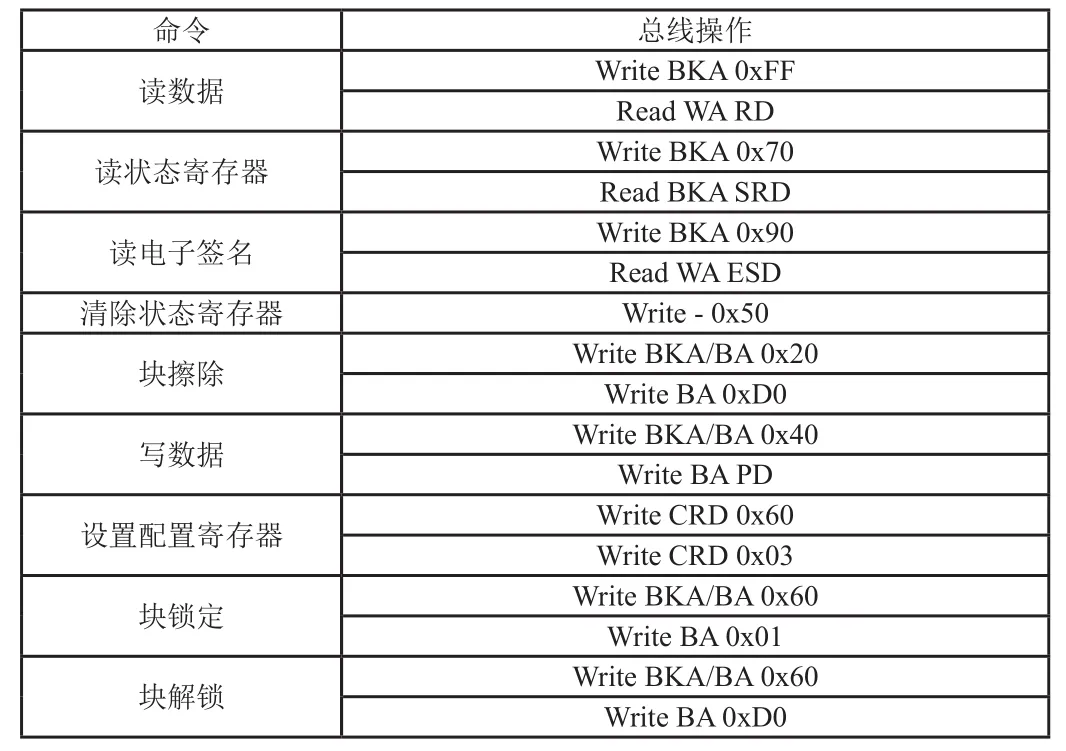

Flash操作采用命令访问方式,在进行访问之前要先写相应命令,具体操作如表2所示。

表2 Flash操作命令

3.Flash访问在线验证

本节编写对Flash进行读电子签名、异步读写和擦除等操作的VHDL代码,并通过Chipscope工具进行了在线调试,验证了FPGA配置完成后对Flash操作的可行性和正确性。

XC5VLX110 FPGA的配置文件大小为29124608bit(约为28Mb),因此XCF128X存在约100Mb的剩余空间可以利用。为了不覆盖配置文件,本文对Flash Bank3的Block0(字地址区间为0x600000~0x60FFFF)进行相应操作。

Flash写时序和异步读时序分别如图2和图3所示。

图2 Flash写时序

图3 Flash异步读时序

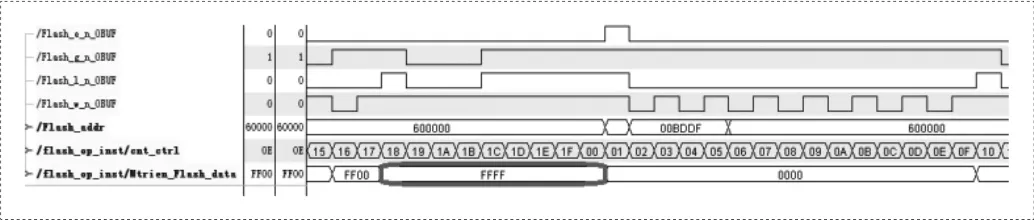

Flash读取电子签名的在线调试图如图4所示。其中读取的制造商ID为0049,器件ID为506B,与器件手册一致。

图4 Flash读取电子签名的在线调试图

Flash上电后寄存器默认配置为同步读模式,需要将配置寄存器的CR15位设置为1进入异步读模式。Flash上电后处于锁定状态,进行写操作前需要先对写地址空间解锁;若Flash写地址空间非空,解锁后还需要对其进行擦除操作。Flash读写操作的在线调试图如图5所示,在地址0x60000写入数据0xAA55,然后读该地址,读出来的数据为0xAA55。

图5 Flash读写操作的在线调试图

Flash块擦除的在线调试图如图6所示,Flash 地址0x60000擦除后内部数据为0x FFFF。

图6 Flash擦除的在线调试图

4.结论

本文以Xilinx Virtex5 XC5VLX110 FPGA及其配置Flash XCF128X为例,介绍了FPGA配置完成后对Flash的读电子签名、总线读、总线写、块擦除等操作,并通过Chipscope工具进行了在线验证,在空间和成本受限的情况下为后续需要存储外部数据的应用提供了设计依据。