利用DMA模块的图像采集处理系统的优化设计

,,

(1.湘潭大学 微电子科学与工程系,湘潭 411105;2.湖南长沙进芯电子科技有限公司)

引 言

随着物联网的迅速发展,人们对设备使用效率的要求越来越高,嵌入式系统的高速性能也越来越备受关注,这对广泛应用于车站、酒店、银行等场合的嵌入式身份证读卡器系统也提出了更高的要求。

嵌入式身份证读卡器系统是基于数字信号处理器(DSP)和现场可编程门阵列(FPGA)架构而开发的实用系统。该系统不仅结构灵活,且有较强的通用性,适合模块化设计从而提高算法效率,而且开发周期较短,平台易于维护和扩展,适用于实时信号处理[1]。

身份证读卡系统虽然已经被广泛应用,但是因为用户需求的多样化以及受数据传输响应速度的限制,现有的系统数据传输速率并不能满足高速CMOS图像传感器的采样频率以及用户对使用等待时间的要求。针对这一问题,利用集成了DMA模块的DSP进行数据搬移、存储和处理,提高了整个系统的响应速度。

1 原系统简介

身份证读卡器是一款用于对身份证信息扫描和采集的仪器,需要获取的身份证数据主要包括射频识别RFID[2](Radio Frequency Identification)数据和图像扫描数据。RFID信息数据大约有100多KB,通过串行通信获取,而图像扫描数据则通过A/D采样的模拟信号,信号数据有4 MB左右。对于如此大量的数据处理,速度是关键,处理的慢则耗时越久,这是使用者难以接受的。所以根据实际使用情况及用户要求,我们将扫描过程耗时控制在1 s以内,经计算要达到这个时间要求,则图像扫描频率需达到3 MHz以上。

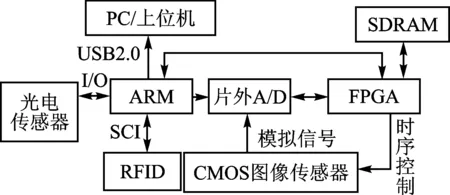

原系统由CMOS图像传感器、光电传感器、片外A/D、ARM、FPGA、SDRAM和USB2.0接口等硬件组成。系统硬件结构框图如图1所示。

图1 系统硬件结构框图

片外A/D采集CMOS传感器图像后由FPGA存储到SDRAM,再由ARM进行处理,最后通过USB2.0上传至上位机[3]。

2 改进系统设计

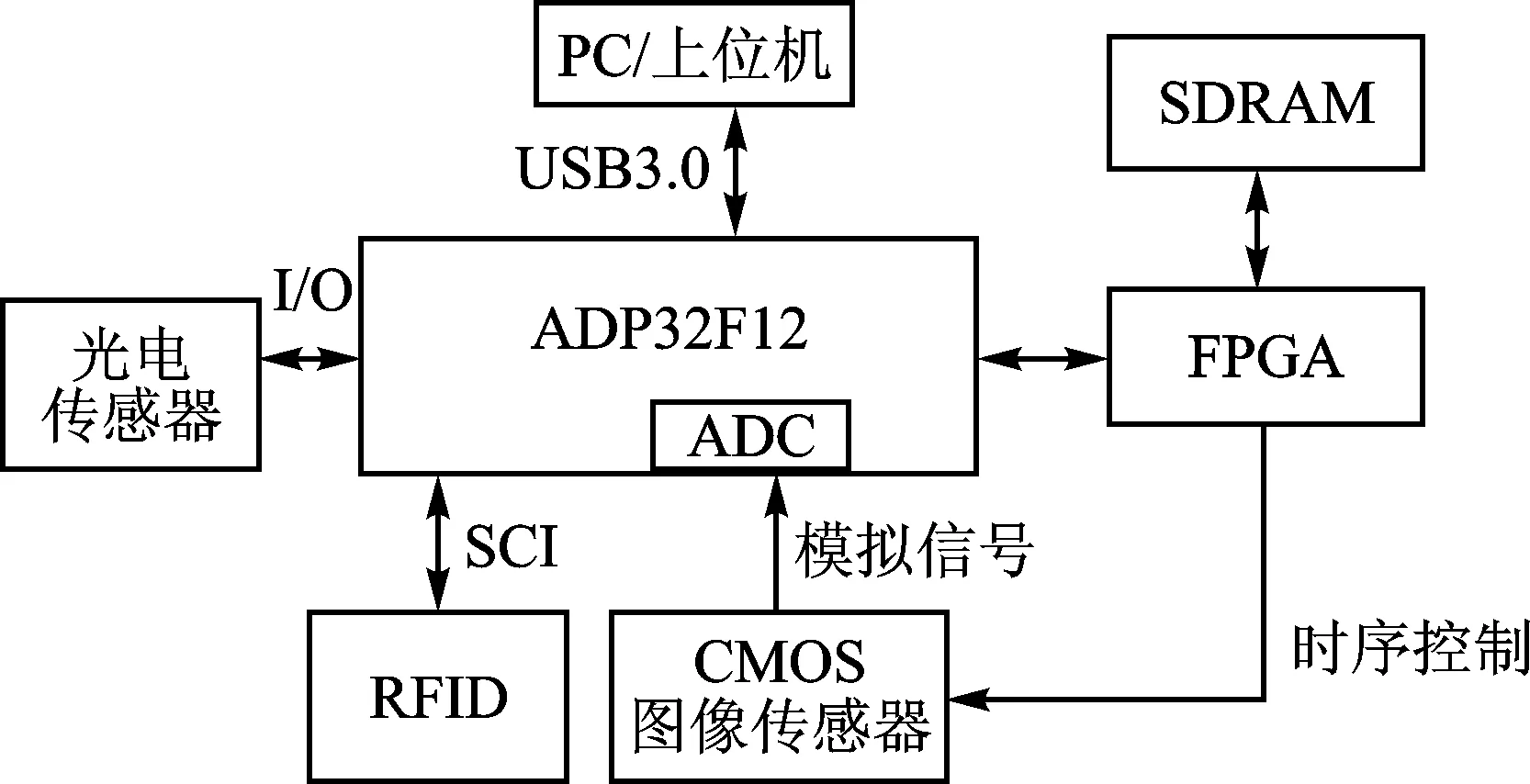

基于对提高整个系统的运行速度及降低硬件结构尺寸来提升性价比的方面考虑,我们提出了一种新的升级方案——用一块DSP芯片替代ARM+片外A/D两块芯片,新方案系统硬件结构框图如图2所示。

图2 新方案系统硬件结构框图

方案中的DSP首先使用的是ADP32F12,该芯片内部集成了一个流水线结构且分辨率为12位的ADC模块[4]。该ADC模块有16个通道,可配置成两个独立的8通道模块,可以为外设事件管理器EV服务,两个8通道模块具有一对一系列转换自动化序列化的能力,通过模拟多路器可以任意选择可用的8个通道中的一个通道,一旦转换结束,已选择的通道值就保存在各个通道的结果寄存器ADCRESULT中。自动序列允许系统对同一通道转换多次,允许用户执行采样算法[5],完全等效TITMS320F2812芯片的功能。

由于A/D采样率最高可达12.5 MHz,如果采用该系统,直接以一个8 MHz的频率去启动A/D采样,由于上下两个面各有一个扫描头,各需要一个A/D通道对其采样,所以实际的A/D采样频率为4 MHz。

同样,两个A/D通道采集完后进入A/D中断,该中断的频率同样是4 MHz,然后在中断服务程序中将A/D采样数据搬移至片外RAM中,整个扫描过程结束。但在实际测试时发现扫描数据会大量丢失,理论上扫描数据有:

648(每行点数)×3(RGB三色)×1024(行数)×2(正反两面)=3 981 312个

而通过实验扫描得到的数据点数只有理论计算的一半。经验证,发现A/D采样在非连续模式下其采样率远达不到12.5 MHz,而只有1.5 MHz左右,并且中断的响应频率最快只有2 MHz左右,完全满足不了系统的应用需求。

经分析发现,A/D如果在连续采样模式下,采样率能够满足应用要求,只是采样后的数据CPU无法将其快速搬移。但如果仍沿用该系统架构,即使采用A/D连续采样,数据也无法达到应用要求的速度进行快速搬移,因为2 MHz的A/D中断的响应频率还是无法满足要求。无法满足数据搬移的速度是该方案的瓶颈所在。

于是,在上述方案的基础上将ADP32F12替换为ADP32F28335,该芯片相对ADP32F12,除了具有ADP32F12所有的功能及相对更先进的新功能外,还集成了DMA模块,DMA模块用硬件实现了从源地址到目的地址的搬移,只需要CPU在数据传送开始和结束做一些处理,即可直接进行高速数据传送,从而为其它系统功能释放带宽,提高CPU利用率[6]。

ADP32F28335共有6个DMA通道,每个通道有各自独立的触发源来启动数据传输,并通过各自独立的PIE中断触发CPU 来控制DMA数据传输的开始和结束。DMA模块内部由DMA控制器DMAC(DMAC是DSP的核心数据传输引擎[7])来掌管其内部地址总线如数据读/写总线、控制总线,与总线相连的是地址和数据源/目的接口。

数据传输时采用了四级流水线机制,内部状态机是嵌套的内循环和外循环两级结构,内循环表示每个通道在一次外部中断触发到来时,每次突发传送的数据量;外部循环表示内循环的次数。

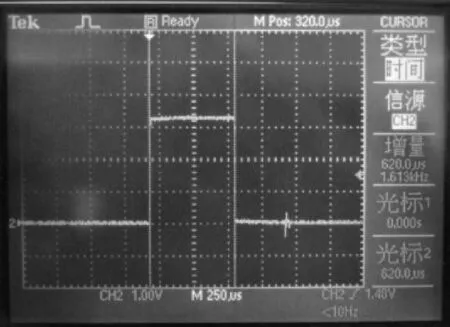

首先,对DMA从A/D将数据搬移至片外SDRAM这个过程的响应速度进行了验证。由于DMA的源/目标地址的可配置性,直接将源地址设置为A/D结果寄存器、目标地址设置为片外SDRAM。系统设置为:A/D时钟为25 MHz,采样率为12.5 MHz,采样模式设为双序列顺序采样、2通道(A0、A1)连续采样,每个通道采样648个点,共1296个点,则总共耗时为:

试验中,用I/O翻转测试耗时结果如图3 所示。

图3 I/O翻转测试耗时结果

由图3可知,总共耗时为104 μs,与理论计算值基本吻合,结果表明合理利用ADP32F28335的DMA搬移连续A/D采样结果数据的速率是能够满足要求的。

在核心功能满足要求的基础上,搭建了整个系统的硬件平台,整体系统结构如图4所示。

图4 整体系统结构框图

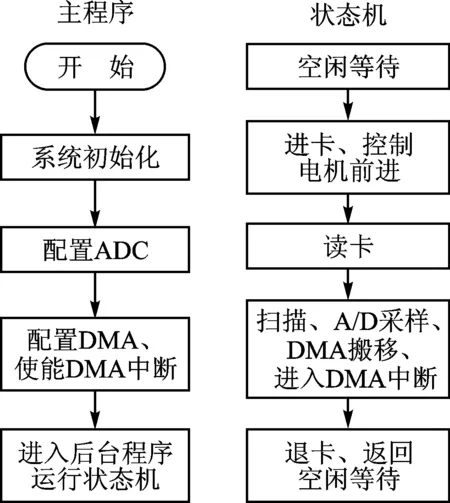

A/D采样结果通过DMA传输至片外SDRAM进行存储,等整张图片扫描完毕后,DSP再从SDRAM中读取扫描数据进行相应的处理,处理完后再存回SDRAM中,等所有处理过程结束后,再由FPGA将SDRAM中处理好的数据采用USB进行主控制器与上位机的数据通信[8],经USB3.0发送至上位机进行显示。整个系统的程序流程如图5所示。

图5 整个系统的程序流程

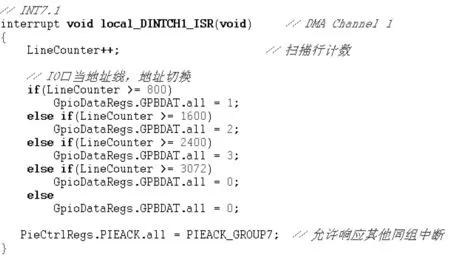

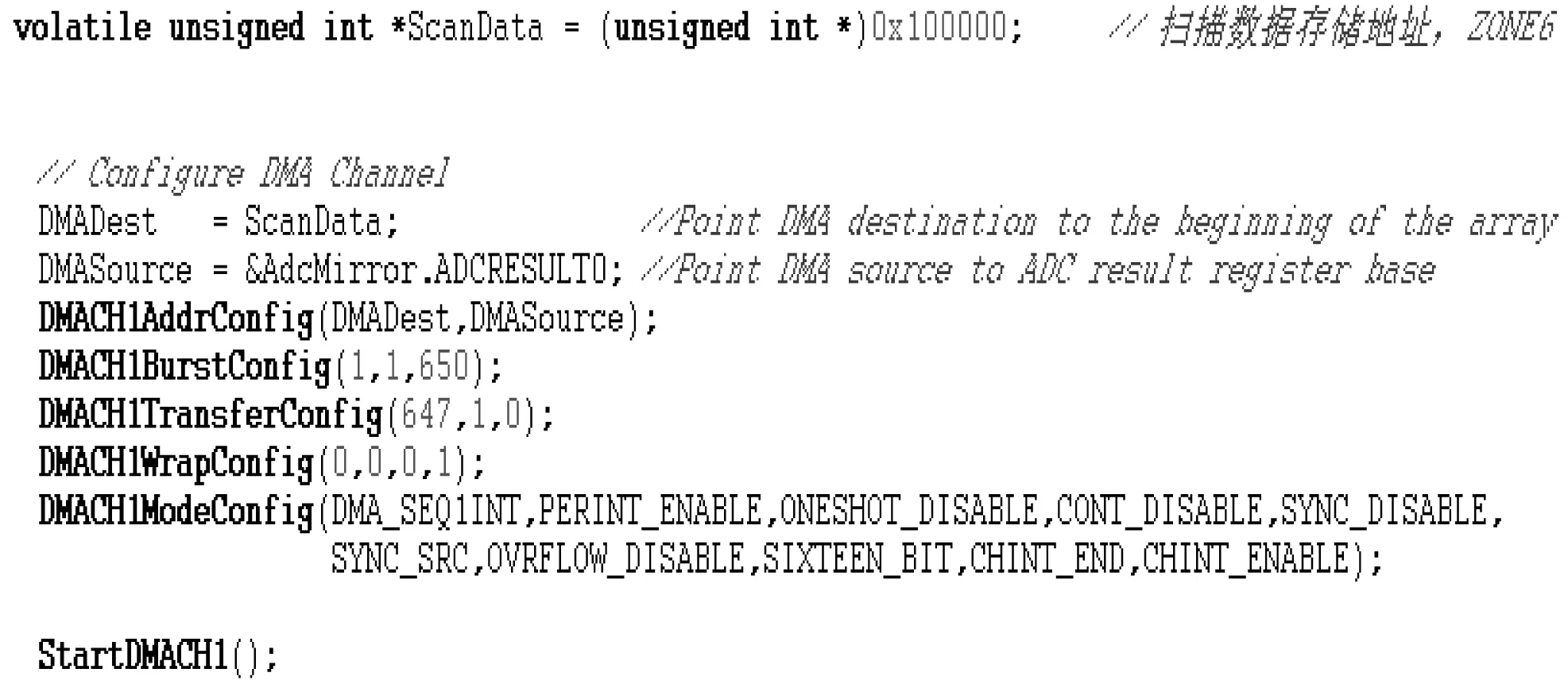

由于ADP32F28335的外部扩展的寻址范围只有1 MB,而我们的SDRAM有16M×16bit的存储空间,为了满足在超出的寻址范围寻址,使用GPIO8口的GPIOB0~GPIOB3作为地址线,经FPGA的接口处理使得DSP能够对SDRAM的16 MB的空间进行访问。而其中的地址切换在DMA中断中进行,即每达到1 MB的地址范围后,切换I/O口状态以达到将I/O口作为地址线使用的目的,DMA中断程序如图6所示,其中DMA配置相关程序代码如图7所示。

图6 DMA中断程序图

图7 DMA配置相关程序代码

3 处理结果

通过对原系统的优化设计,在提升了扫描速度和降低硬件结构尺寸来提升性价比后,将身份证插入读卡器,在上位机端得到的测试结果如图8所示。扫描过程耗时0.4 s,比原系统提升了90%的速率,大大提升了用户的体验效果。测试结果验证了该系统优化设计的正确性,本系统所具有的高效性和实用性的特点将会被广泛地应用。

图8 测试结果

结 语