基于恒温晶振和CPLD的紧凑型高稳时钟模块的设计实现

徐国盛

(中国电子科技集团公司第五十四研究所,石家庄 050000)

1 核心性能器件——恒温晶体振荡器

恒 温 晶 体 振 荡 器(Oven Controlled Crystal Oscillator,OCXO),简称恒温晶振,做为一个专门的频率发生器件,是指使用恒温槽技术使其中的核心部件石英晶体谐振器及所配振荡电路保持温度恒定,从而减少外界环境的干扰,极大的提高了输出的频率稳定度。由于其指标高性能出色,成为通信及测量领域中高端仪器与设备的核心元器件。

虽然其功能单纯,就是产生一个单一的固定频率,但却是整个模块性能的核心器件,直接决定最终性能的优劣。所以我们选用了一款自主设计生产的双层恒温低噪晶体振荡器,其各方面性能指标远远优于普通的恒温晶体振荡器。外围则配以一系列电路,如CPLD,MCU,DDS,PLL等,进行各种功能扩展,做成一个封装极为紧凑的时钟基准产生模块。具有多个时钟输出,频率可选可调,可以与外部源同步、并在保持阶段具有预测性的自主调整功能。

2 主要数字逻辑器件——CPLD

可编程逻辑器件有FPGA和CPLD两大类。FPGA功能强大,资源丰富,往往含有PLL,DDS等各种内核,可以为整个数字功能部分提供一站式的解决。但是在本产品设计中我们没有使用FPGA,而是由项目的实际目标要求并结合以往开发经验选用了CPLD。将可以由FPGA统一完成的功能(如数字逻辑、控制、接口等),分解为由CPLD和MCU和其它独立器件实现。这主要有如下考量。

FPGA和CPLD都是可编程逻辑器件,有许多共同点,在不少场合下也可以相互替代,但由于二者内部结构上的差异,又有各自的特点。一般来说FPGA的集成度比CPLD高,具有更复杂的布线结构和逻辑实现。但在同等设计水平和工艺水平下,往往CPLD的速度比FPGA快,并且具有较大的时间可预测性。这是由于CPLD内部采用固定长度的金属线进行各逻辑块的互连,其连续式布线结构决定了它的时序延迟是均匀的和可预测的,而FPGA的分段式布线互连结构决定了其延迟和时序的不完全预测性。

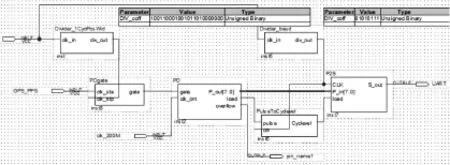

而本产品的定位就是注重性能,追求时序的精准和时基的准确,所以我们使用CPLD和其它高性能的独立IC来实现功能。由于CPLD可以只用来实现与时序和性能严格相关的核心功能部分,而非实时运算、控制与接口部分都交由MUC来完成,所以所需资源较少,可以更从容的选择封装更小更紧凑的器件。CPLD采用了Altera公司MAX V系列的一款EQFP-64 Pin封装元件,只有9mm*9mm见方,是一款封装极为紧凑的小型CPLD。

3 控制与接口部分——MCU

MCU负责非实时的运算处理,数据采集,控制,及外部的通信接口实现。选用了SiliconLabs的8051内核的EFM8系列单片机。对比了几种适合工控和仪表常用的单片机,如microchip的PIC系列,TI的MSP430系列等,SiliconLabs的8051-EFM8系列单片机在同等的小封装尺寸下,外设资源更丰富和强大,且端口配置更为灵活,非常适合本项目应用。

图1 CPLD程序顶层模块图

图2 MCU项目工程文件树形图

4 最终结果

经过精心的构架与调试,本产品最终达到良好的效果,很好的满足了客户的上机使用。

[1] 赵声衡.晶体振荡器[M].北京:科学出版社,2008.

[2] EDA先锋工作室.Altera FPGA/CPLD设计[M].北京:人民邮电出版社,2011.

[3] 马忠梅.单片机的C语言应用程序设计[M].北京:北京航空航天大学出版社,2007.