Ku波段低相噪频率综合器设计

金 力,杨 玲

(中国兵器装备集团成都火控技术中心 四川 成都 611731)

1 引言

频率综合器又称之为频率源,主要功能是产生电子系统所需要的各种形式的频率信号,在通讯、雷达、电子对抗、遥控遥测和仪器仪表等众多领域应用广泛,是电子设备射频前端的核心部件之一,其性能的优劣直接影响系统整机的性能和指标。随着电子科学技术的快速发展,现代雷达系统对频率综合器的要求也越来越高,低相位噪声、低杂散抑制、高稳定度已成为频率综合器的发展趋势。

多普勒雷达是通过测量有用回波信号所产生的多普勒频移来确定运动目标的速度。回波信号不仅包括有用的运动目标回波,还包括从大地或固定目标反射回来的干扰信号。这些回波信号经过接收机下变频后,能否区分的关键取决于其边带噪声,特别是对于低小慢目标,相位噪声决定了系统的灵敏度和选择性能,成为雷达设备中要求最为严苛的指标之一[1]。

本文重点介绍了一种能够有效抑制相位噪声和杂散信号的频率综合器设计方法,并且通过原理样件研制,获得了杂散和相位噪声的测试结果,能够对工程样件以及正式产品的研制提供借鉴和参考。

2 方案设计

2.1 相位噪声模型设计

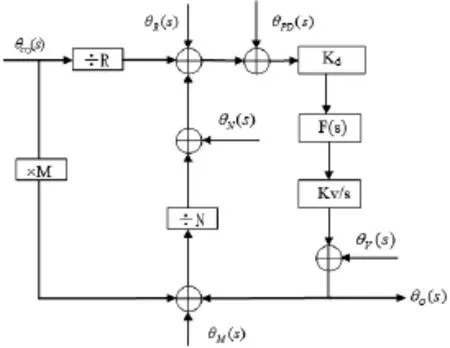

传统的频率综合器设计是直接采用反馈支路分频锁相方式,但这样的方式会使得环路分频比变大,同时也会抬高环路内部噪声电平,并且增加频率转换时间。这种设计方法已不能满足现代雷达对变频带宽和频率间隔的要求,因此急需对噪声模型进行重新设计。目前,业内提出了一种混频锁相设计方式,可以有效减小锁相环路分频比,有助于改善雷达系统的动态响应和相位噪声指标,其基本工作原理是将基准信号与反馈信号在鉴相器中进行相位比较,输出电压通过环路滤波器来抑制噪声的高频分量来控制VCO,系统通过改变反馈支路混频后的分频比,实现频率捷变。当环路被锁定时,输出频率f0=(M+N/R)fr,频率间隔为Δf=fr/R。其原理框图如图1所示[2]。

图1 环内混频锁相环框图

锁相环附加相位噪声的原理框图如图2所示,其中,θcry(s)、θR(s)、θpd(s)、θN(s)和θv(s)分别为晶振、R分频器、鉴相器、N分频器和压控振荡器的附加相位噪声的拉普拉斯变换。锁相环锁定时近似为线性系统,根据负反馈理论,可得锁相环输出的相位噪声为[2]:

图2 锁相环路附加相位噪声原理图

L(f)是单边带相位噪声功率密度与载频功率之比,H(f)是锁相环闭环传递函数,He(f)是锁相环误差传递函数。对于Ku波段频率综合器设计而言,M值较大,而N值较小,因此通过优化偏置频率和分频比,便可以得到性能最佳的相位噪声[3]。

2.2 频率综合器设计

为进一步改善输出信号在近区的相位噪声指标,在第一本振设计上,可以考虑采用环内混频锁相方式,其主要方法是将晶体振荡器二分频后的基准信号与VCO和频标组件下变频后的分频信号进行鉴相处理,最后经滤波器滤波后去锁定VCO的输出频率;第二本振拟采用反馈分频锁相环设计方式,同时,为满足波形的设计要求,激励源拟采用DDWS+上变频的方式产生[4]。Ku波段频率综合器的设计框图如图3所示。

图3 频率综合器电路设计框图

3 关键技术分析与论证

3.1 相位噪声分析

根据原理与工程经验,锁相环在近区附近的相位噪声主要由Ku频标、参考源以及锁相环器件的剩余相位噪声共同决定,远区的相位噪声主要由VCO所决定。本Ku波段频率综合器拟采用的晶振相位噪声为-160dBc/Hz@1KHz,分频器的剩余相位噪声为-142dBc/Hz@1KHz,分频器剩余相位噪声起主导作用,故参考输入的相位噪声为-142dBc/Hz@1KHz左右。锁相环反馈端经过20分频后,相位噪声将恶化26dB,同时在工程设计中还可能引入3dB左右的指标恶化,因此输出相位噪声应为-113dBc/Hz@1kHz左右。最后,输出信号与相位噪声优于-110dBc/Hz@1kHz的Ku频标相混频,输出相位噪声应为-110dBc/Hz@1kHz左右[5]。

3.2 杂散抑制分析

锁相环可看作窄带滤波器,能有效滤除环路带宽外的杂散。本振杂散主要来自鉴相频率泄漏,环路滤波器采用有源比例积分滤波器,锁相环对鉴相频率有70dBc左右的抑制。

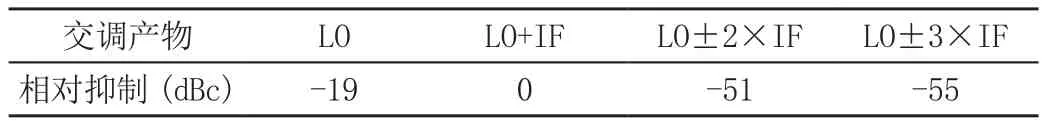

激励杂散主要来自DDWS和本振的交调产物。DDWS可通过测试杂散的分布和强度,进行合理的频率规划避开杂散较高的区域并用滤波器滤除杂散。交调产物可选取合适的混频器加以优化,混频器主要杂散如表1所示。表1表明在输出LO+IF与附近的LO及LO+2×IF在频谱上有一定的距离,可用滤波器予以滤除。

表1 交调产物及相对抑制

除了在电路上采取措施外,结构盒体采用分腔设计增强隔离,适当增加螺钉数量以减小缝隙及信号泄漏。

4 研制结果

频率综合器的相位噪声和杂散如图4和图5所示,均采用Agilent公司N9030A频谱分析仪得到测试结果。图4显示的微波本振相位噪声优于-111dBc/Hz@1kHz,图5显示的测试结果为在100MHz带宽内,杂散电平小于-70dBc,符合技术指标要求。

图4 频率综合器相位噪声测试结果图

图5 频率综合器杂散指标测试结果图

5 结语

本文通过对频率综合器低相噪、低杂散的理论与工程研究,成功研制了原理样件,并且通过测试和对比,各项指标满足设计要求,能够为高性能频率综合器工程样件以及正式产品的研制奠定基础。随着微波元器件性能的持续发展,高性能频率综合器将得到越来越广泛的应用。

[1]Ulrich L.Rohde,Microwave and Wireless Synthesizers Theory and Design,John Wiley & Sons,1997.

[2]白居宪.低噪声频率合成,西安交通大学出版社,1995.

[3]丁鹭飞.雷达原理(第五版),西安电子科技大学出版社,2014.

[4]斯科尼克主编.雷达手册(第三版),南京电子技术研究所译,电子工业出版社,2010.

[5]VadimManassewitsch.频率合成原理与设计(第三版),何松柏,宋亚梅,鲍景富,等译,电子工业出版社,2008。