基于FPGA的片上网络通信架构设计*

谢宁波,张乐乾,高健超

(1.桂林电子科技大学信息与通信学院,广西 桂林 541004;2.桂林市桂电中学教务处,广西 桂林 541004)

自1958年第一颗集成电路芯片面世以来,集成电路产业从最简单的小规模集成电路(SSI)起步,先后历经了中规模(MSI)、大规模(LSI)、超大规模(VLSI)和巨大规模(ULSI),发展到如今的特大规模集成电路(GSI)以及高性能片上系统SoC,单个芯片上集成的晶体管数数以亿计。随着集成电路设计复杂度的提高以及器件特征尺寸的减小,高集成度、低功耗、高性能的片上系统(System on Chip,简称SoC)已成为应用最为广泛的芯片解决方案。但是,由于目前绝大部分片上系统都采用总线互联的方式实现资源IP间的数据通信,随着功能IP数目增加,基于总线互连的片上系统在资源复用性、适应性和扩展性等方面无法满足设计需求,成为了制约片上系统性能的瓶颈。

为了突破传统SoC固有的局限性,来自欧洲瑞典皇家理工学院的科研团队于2000年提出了一种全新的适用于大规模SoC的集成电路体系结构——片上网络(Network on Chip,NoC),它把计算机网络中的通信技术移植到片上系统的互连通信中来,从体系结构上解决了多核SoC在扩展性、复用性和通信效率等方面遇到的问题。本文从片上网络的拓扑结构和通信协议设计出发,基于FPGA平台构建并完成了一款5×5二维环面 NoC通信架构的片上网络的设计。

1 NoC系统架构模型

学术界给NoC的定义是:NoC是基于网络通讯的多核系统,用路由和报文交换技术完成通讯任务。NoC一般是由通信网络将多个资源节点相连通构成,针对不同的资源节点,用一定的互联拓扑结构搭建成为通讯通道,使资源节点间进行数据传输时选择合适的通道,从源节点正确地传输到目的节点。在搭建NoC架构的过程中,需要对片上网络进行优化设计,主要包括2个方面的内容,即拓扑结构和通信协议。拓扑结构指的是NoC中通信节点和资源节点的静态分布方式与节点之间的连接方式,拓扑结构的选择对网络的延时、吞吐率、面积、功耗有着重要的影响。常见的拓扑结构可以分为网格结构(Mesh)、环面结构(Torus)、树形结构(Tree)、环形结构(Ring)等。在上述几种拓扑结构中,二维环面结构具有结构对称,易于设计,扩展性优秀,路由算法简单、高效等优点,所以,本设计以二维环面结构为NoC通信架构的拓扑结构模型。

通信协议,指的是系统中的通信双方完成通信或服务所必须遵循的规则和约定,由通信时序、数据交换技术和路由算法三部分构成。为了满足设计要求,本设计基于广泛使用的OSI协议作为通信协议标准,采用全局时钟策略下的同步握手协议、数据分包(package)的交换技术和维序XY路由算法构建NoC通信架构。

2 NoC系统架构设计

2.1 系统总体结构设计

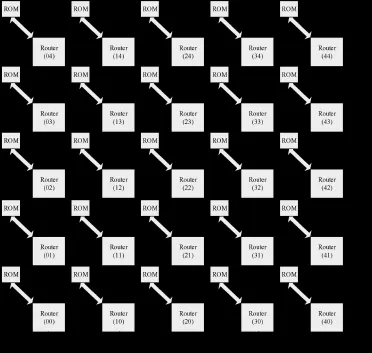

一个完整的NoC通信架构由资源节点、通信节点、资源网络接口和连接整个网络的通道构成。由于资源节点可以是设计好的IP,也可以是已有的SoC,在本设计中不涉及资源节点的设计,主要着眼于完整的通信网络的连接设计以及底层的通信节点和资源网络接口的设计实现。综合考虑设计指标和资源成本,基于上述讨论的通信架构模型,本设计构建如图1所示的5×5二维环面网络结构。

图1所示的NoC架构包含25个路由节点和25个RNI接口,其中,路由器地址从(0,0)至(4,4)。网络的扩展可通过添加更多的资源节点与路由节点实现。

图1 NoC通信网络总体结构

2.2 路由器(Router)设计

在NoC中,路由器(Router)的功能包括了数据的存储转发、报文交换和路由选择等,所以,其性能在很大程度上决定了NoC架构的性能。完整的路由器由输入缓存(InputBuffer)、路由抉择(RouterOpt)、路由仲裁(Arbiter)和输出缓存(OnputBuffer)4个分立模块构成。路由器接收到从上一级路由节点传来的数据包以后,先把数据缓存在输入缓存中,提取有效路由信息进行地址判断,然后向正确的输出通道发出转发请求,如果输出通道空闲,该方向的仲裁模块返回允许应答,同时,开放输出通道,最后经由输出缓存把数据包传输到下一级路由节点的输入通道。完整的数据存储转发过程如图2所示。

图2 NoC路由器结构及数据传输过程示意图

2.3 路由仲裁(Arbiter)设计

片上网络与传统总线相比具有通信带宽高、数据吞吐量大的优势,所以,片上网络在处理多对设备并行通信时,往往会出现多组通信同时竞争同一个路由节点的某个输出通道的问题,因此,需要设计1个合理的仲裁(Arbiter)模块来处理多组请求,并分时返回准许(grant)信号。

本设计采用NoC中广泛应用的轮循调度仲裁机制,轮循调度的基本思想是调度器循环地为队列中的实体提供服务,具有公平、灵活的优点,其功能基于图3所示的状态机实现。

图3 路由仲裁状态机

3 基于FPGA平台的验证与实现

仿真和验证的功能是检查设计的正确性,仿真验证是设计流程中极为重要的环节,同时,也是系统不断修正、改进和优化的过程。我们为NoC通信架构设计了一套比较完善的验证方法,验证了各部件的逻辑以及整个通信架构的功能。

3.1 验证方案

一般来说,基于FPGA的设计与验证流程包括功能验证和时序验证2个方面,功能验证是指使用Modelsim、VCS和NC Verilog等EDA软件模拟电路的工作行为;时序验证则是利用FPGA、CPLD等可编程逻辑器件实现设计的功能,同时,辅以外设搭建一个系统环境,通过对该系统施加测试向量验证设计的时序是否满足设计需求。

3.2 功能验证

为了设计一套有效的功能验证方案,我们通过构建不同数据吞吐量下的通信网络数据交换测试,实现功能验证的完备性。通过无阻塞的点对点节点通信验证,验证路由算法的逻辑、链路的连通性和NoC通信架构传输的正确性,通过设计多节点并行通信验证,验证架构中缓冲队列的读写时序以及轮循调度的路由仲裁机制是否符合设计规范。

3.3 时序验证

本设计的时序验证基于Altera公司的FPGA开发板验证平台进行。与功能验证类似,时序验证以数据存储ROM作为资源IP为NoC通信架构加载测试向量,在原基础上增添1个UART传输过程,通过UART传输把目的节点中的数据以串口数据读到PC端,通过比对实际电路板的输出结果与在仿真平台下得到的预期结果是否一致来判断设计的时序是否正确。

3.4 基于FPGA的物理实现

本设计最终基于Altera公司的Stratix II EP2S90 FPGA开发版完成物理实现。通过FPGA平台进行电路综合,该系统的物理实现共使用了18 046个组合运算器、15 134个逻辑寄存器和21 600个存储单元,整个系统共占用FPGA平台逻辑资源的32%和极少量的存储资源,且综合得到系统的最高时钟频率可达118.79 MHz。资源开销以及设计时序均符合预期设定的设计需求。

4 总结

本设计基于FPGA平台设计实现了一款5×5的二维环面结构的片上网络,具有可复用、并行通信、扩展性好、低开销等优点,可应用于对资源复用性、适应性和扩展性有较高需求的多核片上系统的设计,具有广泛的应用前景和较高的价值。

[1]高明伦,杜高明.NoC:下一代集成电路主流设计技术[J].微电子学,2006,36(4):461-466.

[2]顾华玺,刘增基,王琨,等.Torus网络中分布式自适应路由算法[J].西安电子科技大学学报,2006,33(3):352-358.

[3]Benini L,De Micheli G.Networks on chips:a new SoC paradigm[J].Computer,2002,35(1):70-78.