等精度信号参数测量仪设计

徐 伟,吴 静, 杨 阳, 袁振国, 王 迪

(南京信息工程大学 江苏省气象探测与信息处理重点实验室, 江苏 南京 210044)

陈寿法等[1]提出了一种等精度频率计,实现了量程可自动切换的频率测量,但测量频率范围较小,最高频率只能达到30 MHz,且没有研究当被测信号幅度很小时的测量性能。武卫华等[2]中提出了一种高精度的频率计,但实验预定测频范围仅为1 Hz~10 MHz,且实际实验受信号源输出限制,只是对10 Hz~5 MHz的正弦、方波信号分别进行了频率与周期的跟踪测量。林建英等[3]提出一种等精度数字频率计的SOPC实现方法,该方法可测量频率、周期和占空比,但只讨论了被测信号范围为1 Hz~12.5 MHz的误差。

综上,目前基于等精度测量方法所设计的频率计缺乏有效的宽带信号调理电路而造成被测信号为单一的方波脉冲[4-5]、对被测信号幅度要求高[6-8]、无两路信号的时间间隔测量功能等问题[9-11]。

针对这些问题,本文综合测量多种要素的等精度信号参数测量仪,采用AGC电路实现宽频带范围内小信号和大信号的自动调节,采用复杂可编程逻辑器件(CPLD)完成时序电路。主控制器选用MSP430系列单片机,实现整个测试信号的控制、计数值处理和TFT屏显示。结合了单片机控制灵活性和CPLD处理脉冲信号高精度的优点,可靠性高、测频范围宽、精度高、结构紧凑。

1 CPLD 实现等精度测频

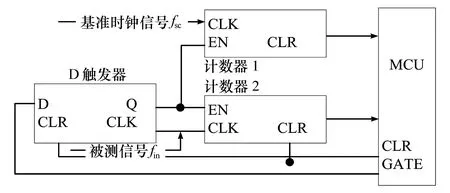

为实现宽频率范围输入信号的高精度测量,采用等精度测量原理。CPLD实现测频电路结构见图1,由触发器、计数器、单片机和CPLD通信实体等组成。

计数器1和计数器2分别对基准时钟信号(基准信号)fsc和被测信号fin计数。计数结果发送到主控制器计算处理。闸门EN控制计数开始和结束。

图1 CPLD测频原理图

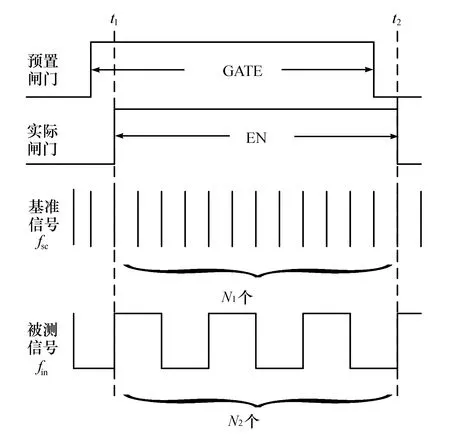

测量时序见图2。单片机产生预置闸门GATE信号(高电平有效),高电平时间固定,如1 s。闸门信号GATE有效时,两计数器并不立即开始计数。GATE送CPLD的D触发器输入端,由于D触发器的边沿触发特性,只有时钟信号CLK即被测信号fin的上升沿到来时,输出端Q才等于GATE,使能两计数器。D触发器相当于同步门的作用,CPLD通过检测被测信号fin上升沿,实现门控信号EN与fin上升沿同步。保证两计数器在被测信号的上升沿到来时才有效,计数开始与结束时间与被测信号严格同步。

图2 等精度测量的时序

当1 s的预置闸门GATE变为低电平时,使能信号EN不是立刻变为低电平,而是要等到D触发器的时钟CLK(被测信号fin)新的上升沿到来时才失效,两计数器并不立刻停止计数。根据两计数器的计数值和基准时钟的频率计算被测信号的频率。

理想情况下,在实际的闸门时间EN内,两计数器对基准时钟信号fsc和被测信号fin的计数值分别为N1和N2。基准时钟信号的频率为fsc。则被测信号的频率fin为

(1)

对被测信号的计数都是在其信号的上升沿触发的,下降沿停止,整个闸门时间EN为其周期的整数倍。实际的计数值N2不存在误差。而对基准时钟信号的计数最多可能相差一个数的误差,即|N1|1。则实际测得的被测信号的频率为

(2)

相对误差为

(3)

将式(1)和(2)代入(3)式得

(4)

相对误差与被测信号的频率没有关系,只与闸门时间EN和基准信号的频率有关。整个频率范围内等精度测量。闸门时间EN越长,基准频率越高,被测信号的相对误差就越小。EN时间约为1 s,CPLD的晶振时钟为50 MHz,则相对误差达2×10-8。

2 系统硬件设计

2.1 总体方案

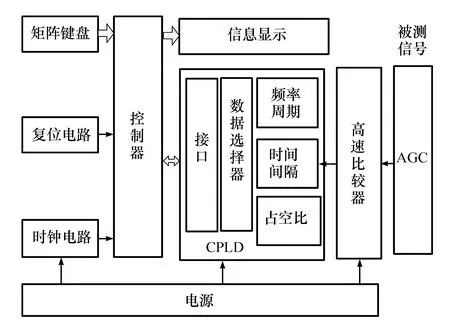

信号参数量测仪的任务是能够快速准确识别输入信号的频率周期、时间间隔和占空比。单片机完成按键的识别、TFT液晶屏的驱动显示、最终频率周期、时间间隔和占空比的计算处理等任务[12-13]。选用具有丰富的外部中断资源和较多IO口的430单片机作为主控制器。时序电路通过CPLD实现,并使用VHDL语言编程[14-15]。软件编写数据总线和控制总线来实现单片机和CPLD之间的通信。图3为系统总体框图。

图3 系统总体框图

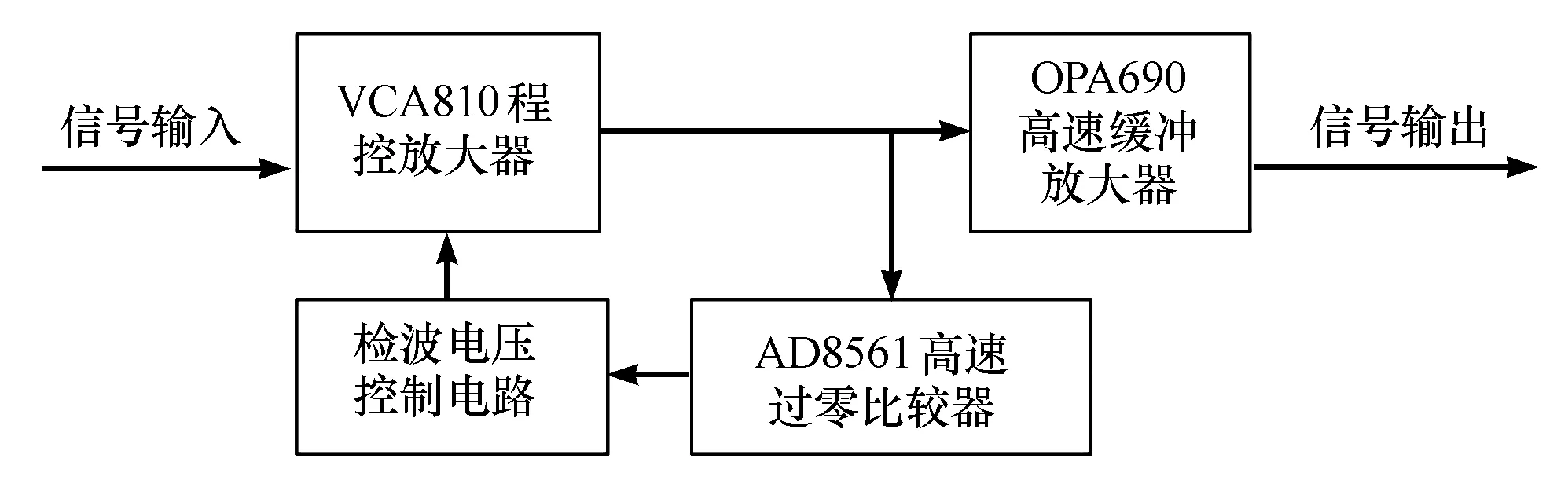

2.2 前级宽带AGC电路

要求被测信号频带宽且幅度变化大,若前级信号调理电路设置为固定的放大倍数,则放大后的信号幅度变化范围大,不利于后级的电路对波形的变换和处理。为适应不同幅度的输入信号,采用宽带AGC(自动增益控制)电路对被测信号的放大倍数自动调节,使放大后的信号幅度稳定,便于后级电路处理。

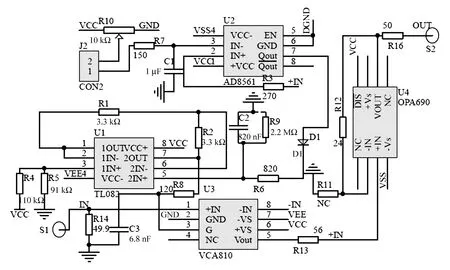

图4为前级宽带调理电路框图,主要由可控增益放大器、检波电路、高速比较电路和高速缓冲器组成,图5为AGC电路原理图。

图4 宽带信号调理电路框图

图5 AGC电路原理图

VCA810为宽带可控增益放大器,3脚G输入的直流电压控制放大倍数。高速比较器AD8561构成过零比较,与后级的充放电电路构成负反馈,控制VCA810的放大倍数。

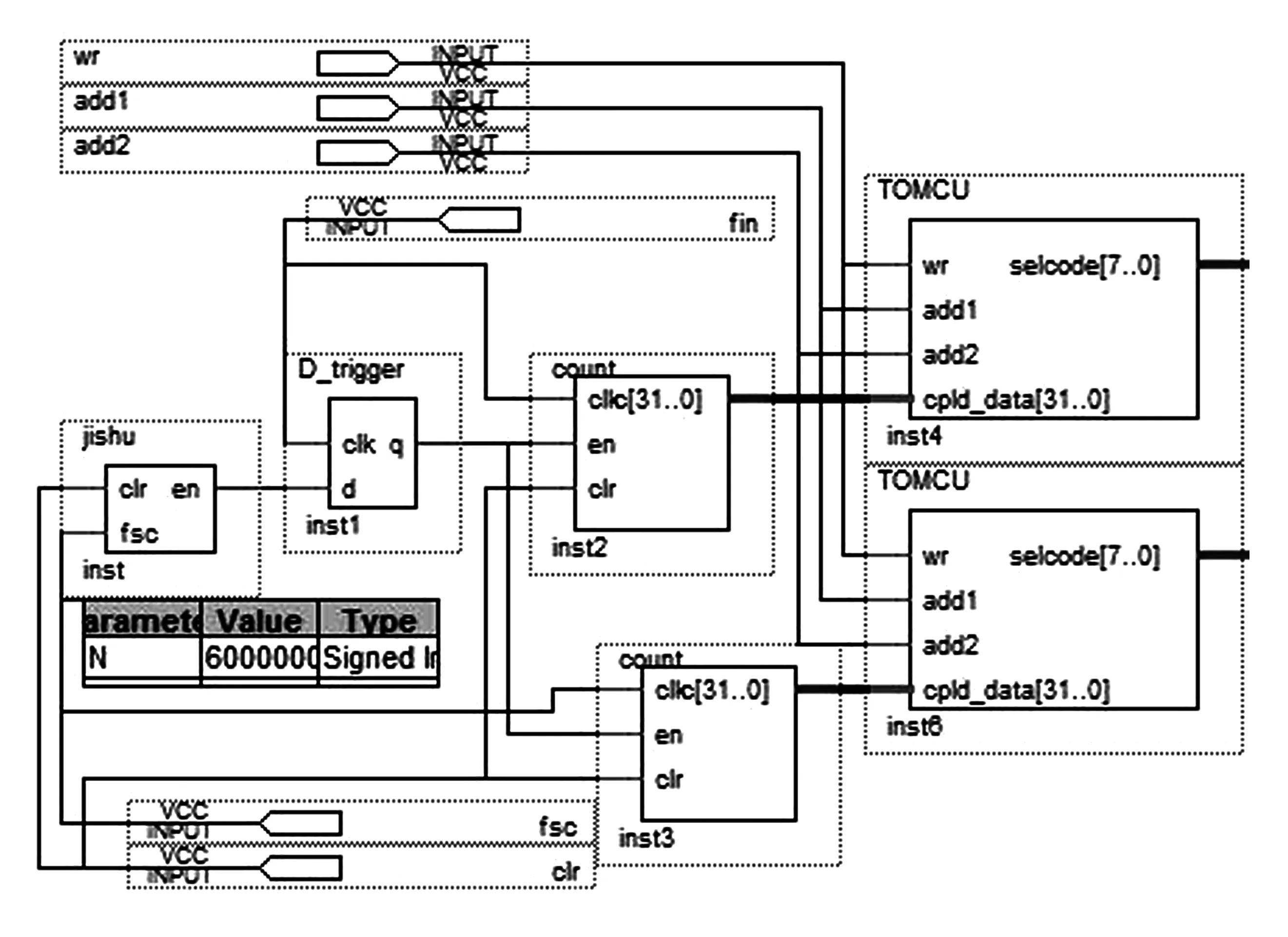

2.3 控制器最小系统及端口分配

图6 控制器最小系统及端口分配

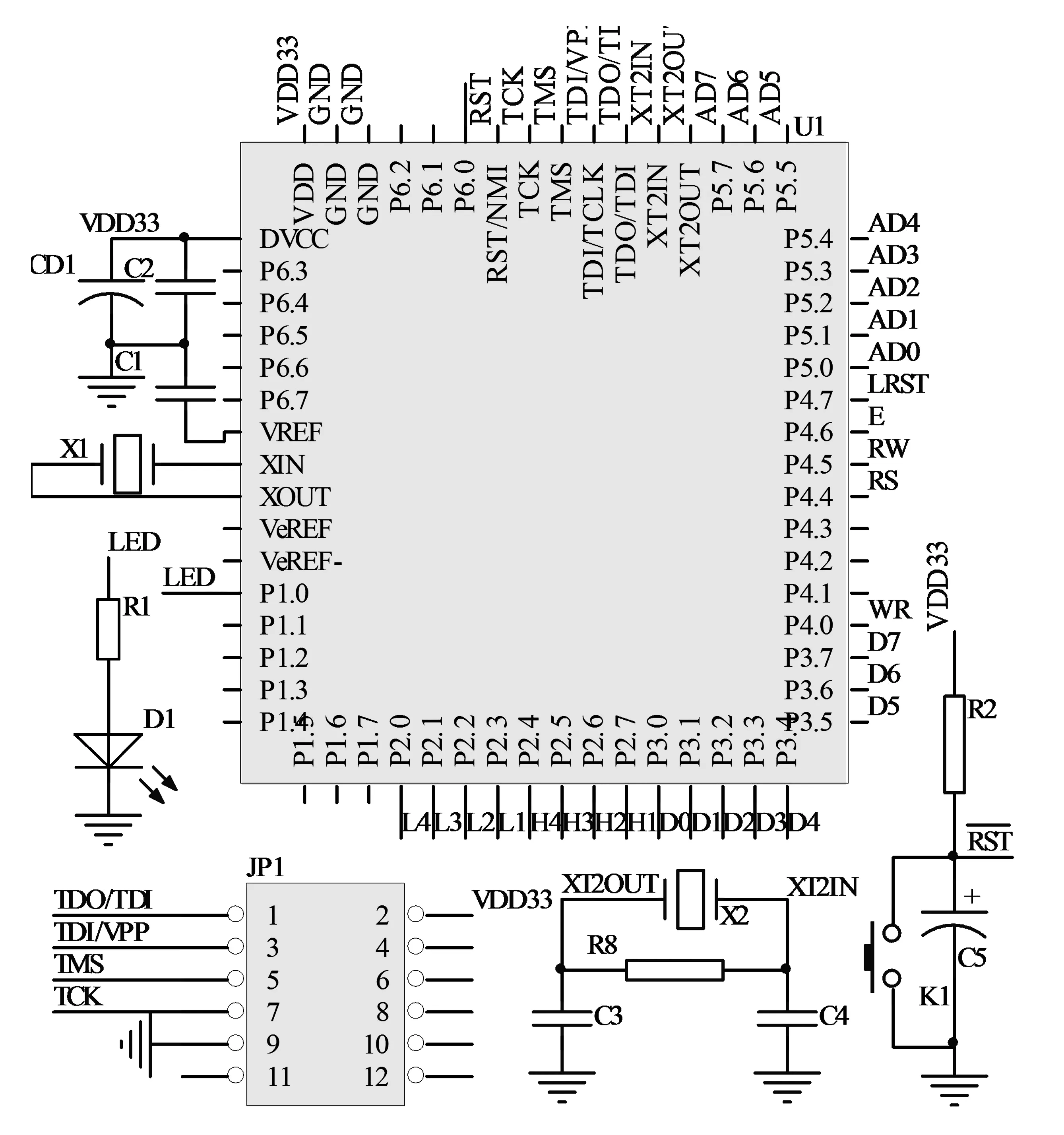

选用MSP430F169单片机为主控,见图6。图6中晶振X1和X2分别产生低速、高速时钟。按键K1、电容C5、电阻R2构成复位电路,JP1为下载口。端口分配如表1。

表1 单片机端口资源分配

2.4 CPLD测量电路

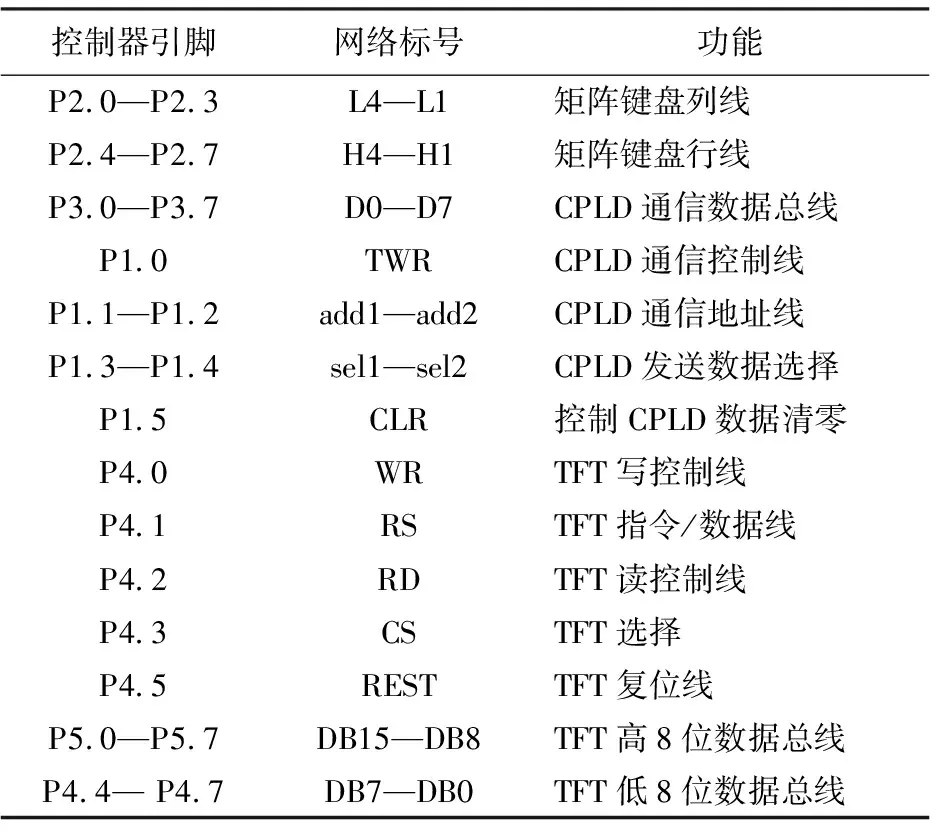

2.4.1 频率周期测量

CPLD测量频率和周期电路见图7,包括计数器inst2和inst3、D触发器inst1、分频器inst、与单片机通信接口inst4和inst6。输入包括基准时钟fsc、被测信号fin、写控制wr、字节选择add1和add2、清零clr。输出为测量数据selcode。计数器inst2和inst3分别对被测信号Fin和50 MHz的基准时钟计数。开始时间受闸门EN控制。分频器inst对50 MHz信号分频得到周期1s的预置闸门,有效时并不立即开启计数。预置闸门通过D触发器产生与被测信号严格同步的实际闸门EN。

图7 等精度测量频率和周期电路

由输入信号上升沿开启闸门,计数器1和2分别用来给标准频率和被测数字信号计数。闸门控制结束时计数器1计数为N1,计数器2为N2,标准频率为fsc,被测频率为fin,则有:

fin/N2=fsc/N1

(5)

fin=fsc×N2/N1

(6)

2.4.2 时间间隔测量

图8为CPLD实现时间间隔测量原理图。由实体计数器inst7和通信接口实体inst9组成。输入端口包括两路脉冲信号A3和A4、清零控制clr2、基准时钟fsc1、字节选择wr5、add3、add4。计数值通过selcode以字节方式发送到单片机。

计数器的过程中,检测A、B信号的边沿。A信号的上升沿触发时钟计数,B信号的上升沿停止计数,计数值通过接口实体发送到单片机进行处理,计数值N乘以时钟周期T,就是A和B信号的时间间隔。

(7)

2.4.3 占空比测量

图9为CPLD实现占空比测量电路。

图9 占空比测量原理图

通过测频电路测量脉冲信号的频率f,再将被测信号输入到图9中实体inst7,检测被测信号的边沿,在高电平期间对基准时钟fsc计数,若高电平期间的计数个数为N,通过上面的测频电路测得的信号频率为fsc,则占空比D为

(8)

3 系统软件设计

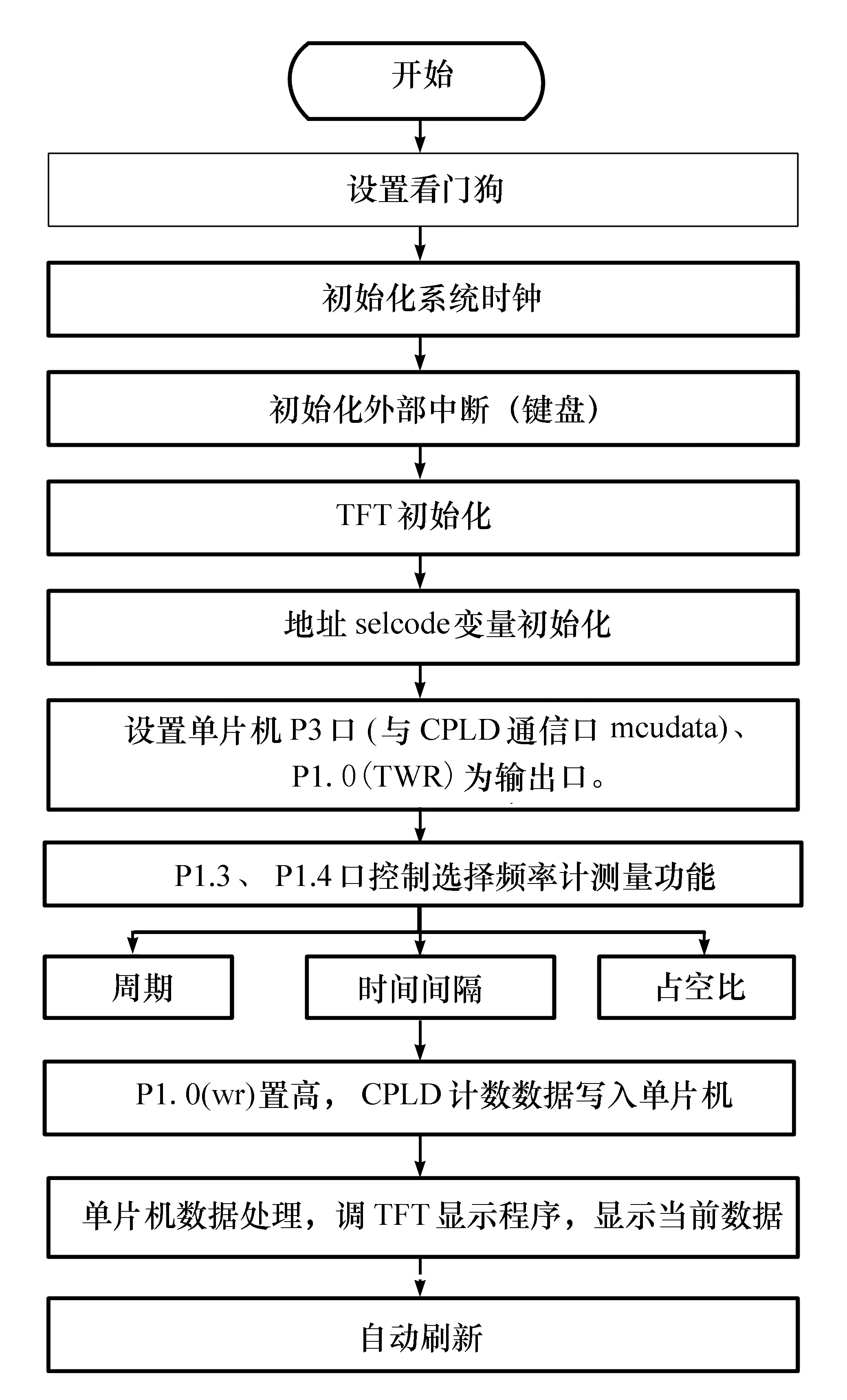

测量电路由CPLD实现,按键识别和计算处理、TFT屏、通信等任务由单片机完成。软件流程见图10。

图10 系统流程图

4 系统测试

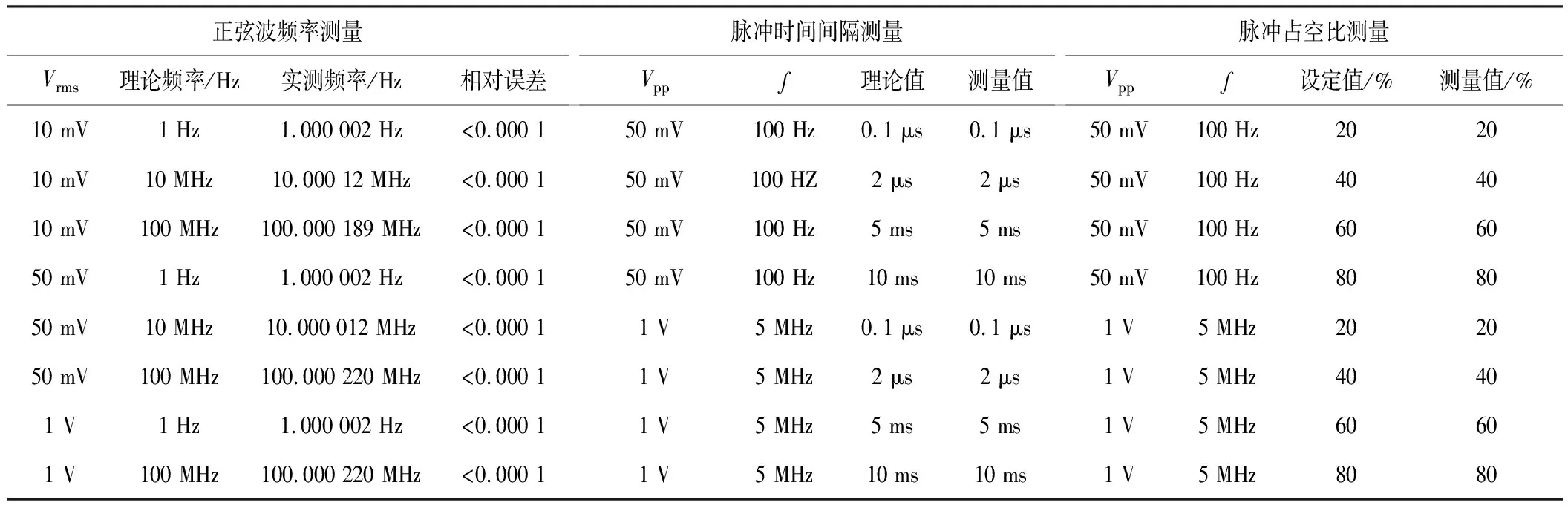

在IAR和Quartus中分别编写并下载单片机和CPLD程序。信号发生器提供输入信号,通过键盘选择频率计功能,测试数据见表2(表中Vrms为电压有效值,VPP为电压峰峰值)。

表2 测量数据

系统实现了对频率范围1 Hz~100 MHz、有效值电压10 mV~1 V的正弦信号的频率测量,相对误差的绝对值不大于10-4;频率范围100 Hz~5 MHz、有效值电压50 mV~1 V的方波信号的时间间隔测量,测量相对误差的绝对值不大于10-2;频率范围1 Hz~5 MHz、有效值电压50 mV~1 V的脉冲信号的占空比测量,测量相对误差的绝对值不大于10-2。数据刷新时间不大于2 s。

5 结论

在CPLD硬件平台上,使用VHDL语言编写D触发器、计数器、单片机和CPLD接口等实体电路,辅以单片机实现信号参数号的等精度测量。在单片机和CPLD通信时,上升沿写特征值,下降沿写地址,确保了数据传输的有效性和可靠性。通过不同的特征值,实现多个程序功能的选择,增加了系统的可扩展性。此外,改善相应的电路中元器件值和晶振大小可以扩展频宽和有效值电压范围。系统实现了高精度的宽幅度、宽频率测量。

[1] 陈寿法,王中鹏. 基于等精度测量原理频率计的设计与实现[J]. 杭州应用工程技术学院学报,2014(6):409-414.

[2] 武卫华,郑诗程.基于SoPC的嵌入式数字频率计设计与实现[J].电子测量与仪器学报,2010,24(2):172-178.

[3] 林建英,高苗苗,杨素英.基于SOPC的等精度数字频率计设计[J]. 国外电子测量技术,2010,29(12):51-55.

[4] 张博,曹学岩,房亮. 基于VHDL的简易数字频率计的设计[J]. 传感器世界,2013,19(5):29-34.

[5] 贺同,陈星,洪龙龙. 基于FPGA的全相位FFT高精度频率测量[J]. 电子测量技术,2013,36(8):80-83.

[6] 李炎, 赵伟,黄巧巧,等.多通道高精度动态频率测量系统的研究与实现[J]. 电子测量技术,2012,35(12):75-80.

[7] 晏细兰,谢景明,熊茂华.基于FPGA和VHDL的高精度数字频率计研究与设计[J]. 计算机光盘软件与应用,2014(15):91-94.

[8] 沈亚钧.基于单片机的数字频率计设计[J]. 山西电子技术,2012(5):14-16.

[9] 徐伟,汤莹,杨绪森, 等.基于CPLD的高精度程控移相器[J]. 电子测量技术,2014,37(1/2):5-9.

[10] 裴林廷,黄世玲.一种基于FPGA小信号宽频带数字频率计的设计[J]. 科技创新与应用,2016(7):61.

[11] 范启亮.一种简易数字频率计的设计与实现[J]. 科技风,2014(20):48-49.

[12] 肖春芳,韩绪鹏.基于单片机控制的数字频率计设计[J]. 国外电子元器件,2012,20(1):140-143.

[13] 张杰,杨艳丽,马莉莉, 等.基于单片机C语言的数字频率计设计[J].内蒙古农业大学学报(自然科学版),2007,28(2):191-192.

[14] 方敏,侯其立,李苗, 等.基于TMS320F2812的数字频率计[J]. 实验室研究与探索,2009,28(5):37-40.

[15] 张青林.基于单片机和CPLD的数字频率计设计[J].合肥学院学报(自然科学版),2010,20(1):43-46.