基于AD9164的小型化设备研究与实现

王 珏

(中国电子科技集团公司 第二十研究所,陕西 西安 710068)

0 引 言

在传统无线电系统中,收发信道混频时使用的本振信号采用模拟器件搭建或者使用现有的快跳本振模块,无论采用哪种设计方案,电路在重量、体积、功耗上都无法满足小型化、轻量化的设计要求。现有设备射频信号的产生方案是先将基带信号变频到中频,通过混频电路进行变频,搭配相应的滤波电路产生射频信号,因此控制时序比较复杂[1]。随着芯片技术的发展,完全可以使用捷变频芯片代替传统的设计方案,不仅可以减小设备体积、重量,且可有效降低功耗。

本文提出一种基于AD9164芯片的小型化设备设计及实现方案,并给出实现方法,在保证性能指标与原有设备相比不下降的前提下,可使设备的重量、体积及功耗明显下降,且整个系统的控制时序得到简化。

1 AD9164芯片简介

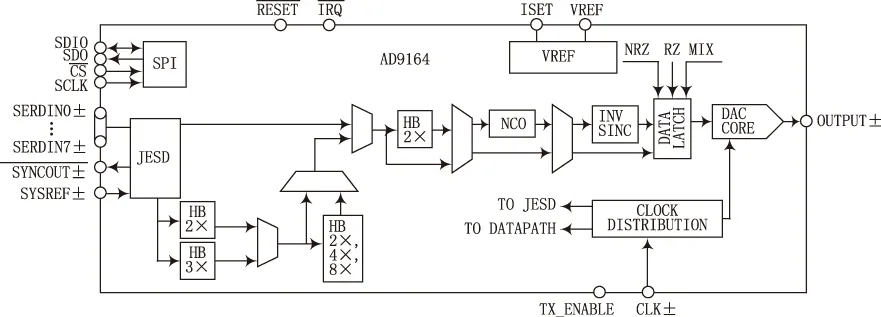

AD9164是高性能16位数模转换器(DAC)和直接数字频率合成器(DDS),支持最高达6 GSPS更新速率,支持最高24倍内插[2]。DAC的内核基于一个四通道开关结构,并配合2倍的插值滤波器,使DAC的有效更新速率在某些模式下高达12 GSPS[3];而DDS由一组32个32 bit数控振荡器(NCO)组成,每一个均包含相位累加器,在基带模式下可输出的频率范围为DC~2.5 GHz,在NRZ模式下可输出的频率范围为DC~6 GHz,在Mix模式下可输出的频率范围为1.5~7.5 GHz。结构框图如图1所示。

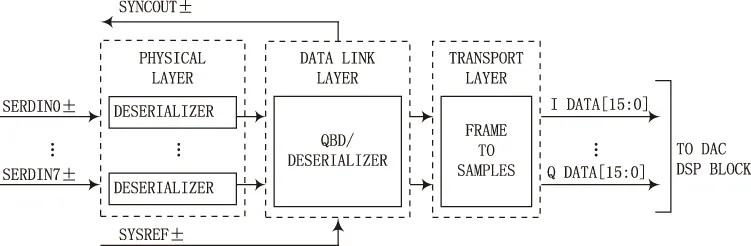

AD9164采用8通道JESD204B接口接收数据[4],其结构如图2所示。

AD9164可采用两种方式产生单频信号,即NCO only模式和NCO基带直流模式。NCO only模式只需提供所需频率对应的频率控制字就可产生相应的单频信号,产生方法比较简单,在该模式下芯片相当于一个DDS;NCO基带直流模式则需同时提供频率控制字和基带数据才可产生相应的单频信号(其实质是在芯片内部对数据流进行上变频处理),该模式可直接将基带信号变频到射频输出。两种模式的频率控制字都为48 bit,计算方式为:

FTW[47:0]=(f/fdac)×248

式中: f为所需产生的频率,单位为MHz; fdac为DAC采样频率,单位为MHz。

图1 AD9164结构框图

图2 AD9164 JESD204B接口

根据AD9164官方手册,切换到NCO only模式需要改动INTERP_MODE寄存器(地址0x110),而改变该寄存器需将JESD204B高速链路进行复位。因此,从NCO only模式切换到NCO基带直流模式时,会重新经历JESD204B高速链路建立链接的过程,该过程需花费近2.5 ms时间。在NCO基带直流模式下,更换频率码及IQ数据,无需复位JESD204B高速链路,整个稳定时间在纳秒级。

2 系统设计方案与实现

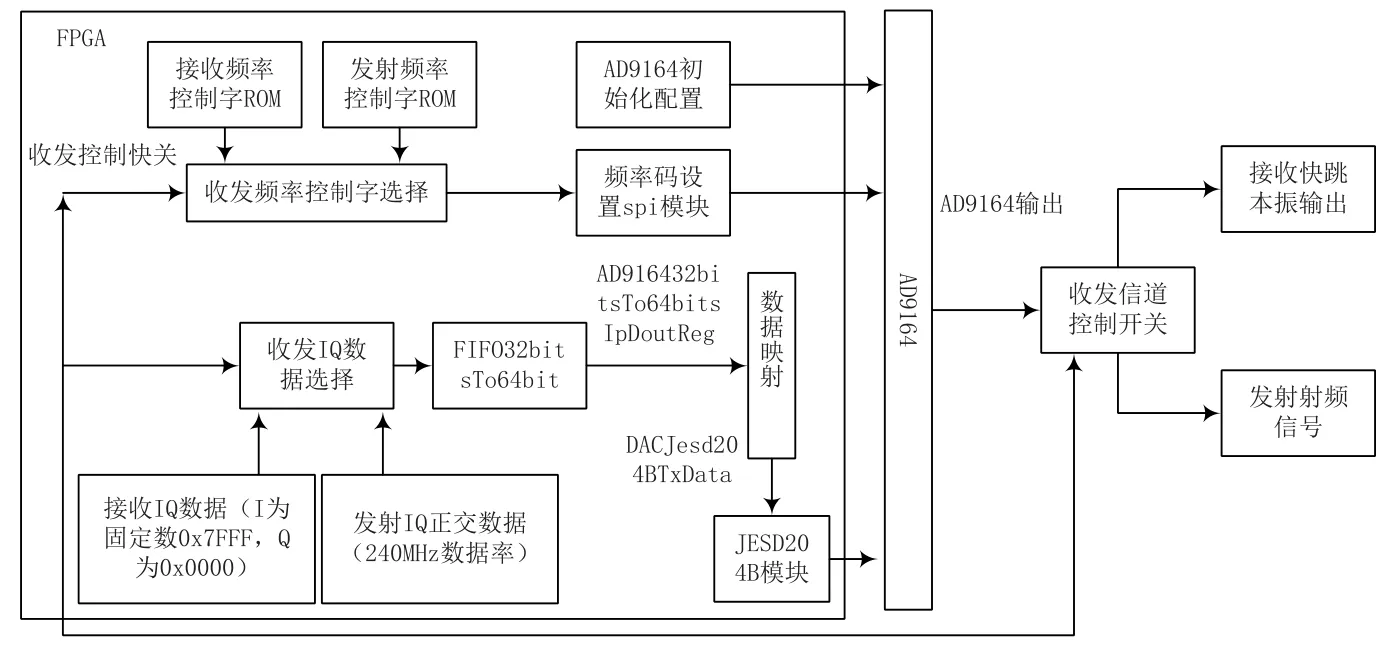

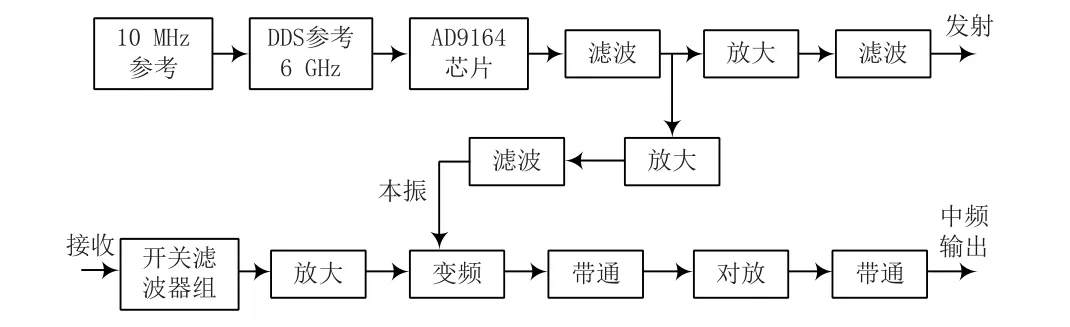

整个系统由FPGA,AD9164及收发信道三部分组成[5],设计框图如图3所示。

2.1 FPGA算法设计

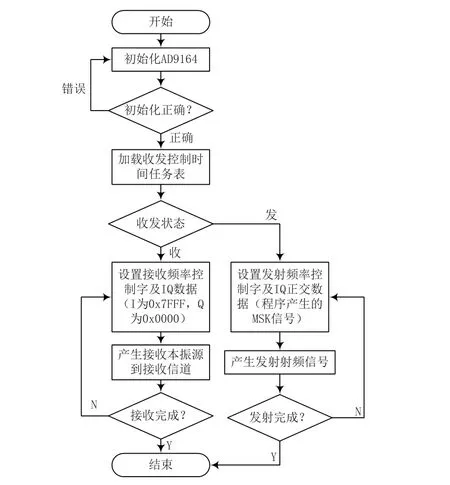

该部分主要完成AD9164初始化配置、收发状态切换控制、收发频率控制字产生及配置、收发IQ数据产生及数据到JESD204B链路的映射。FPGA控制流程如图4所示。

在本系统中,接收过程只需AD9164产生单频信号,因此采用NCO only模式比较方便。发射过程需要使用AD9164内部上变频器产生所需频率范围的MSK信号,因此需要同时设置频率控制字和发射数据,只能采用NCO基带直流模式。系统收发链路的建立时间要求为微秒级,而AD9164两种模式的切换时间为毫秒级,远远超过系统收发切换所需时间,因此,在本方案中收发过程都采用NCO基带直流模式。当处于接收过程时,FPGA提供频率控制字和I路数据(固定值0x7FFF,Q路为0x0000);当处于发射过程时,FPGA提供频率控制字和IQ正交数据。

通过AD9164初始化模块配置AD9164为2 lanes,24倍内插模式,内核采样速率为5.76 GHz,初始频率控制字为0x2AAA_AAAA_AAAB。

图3 系统设计框图

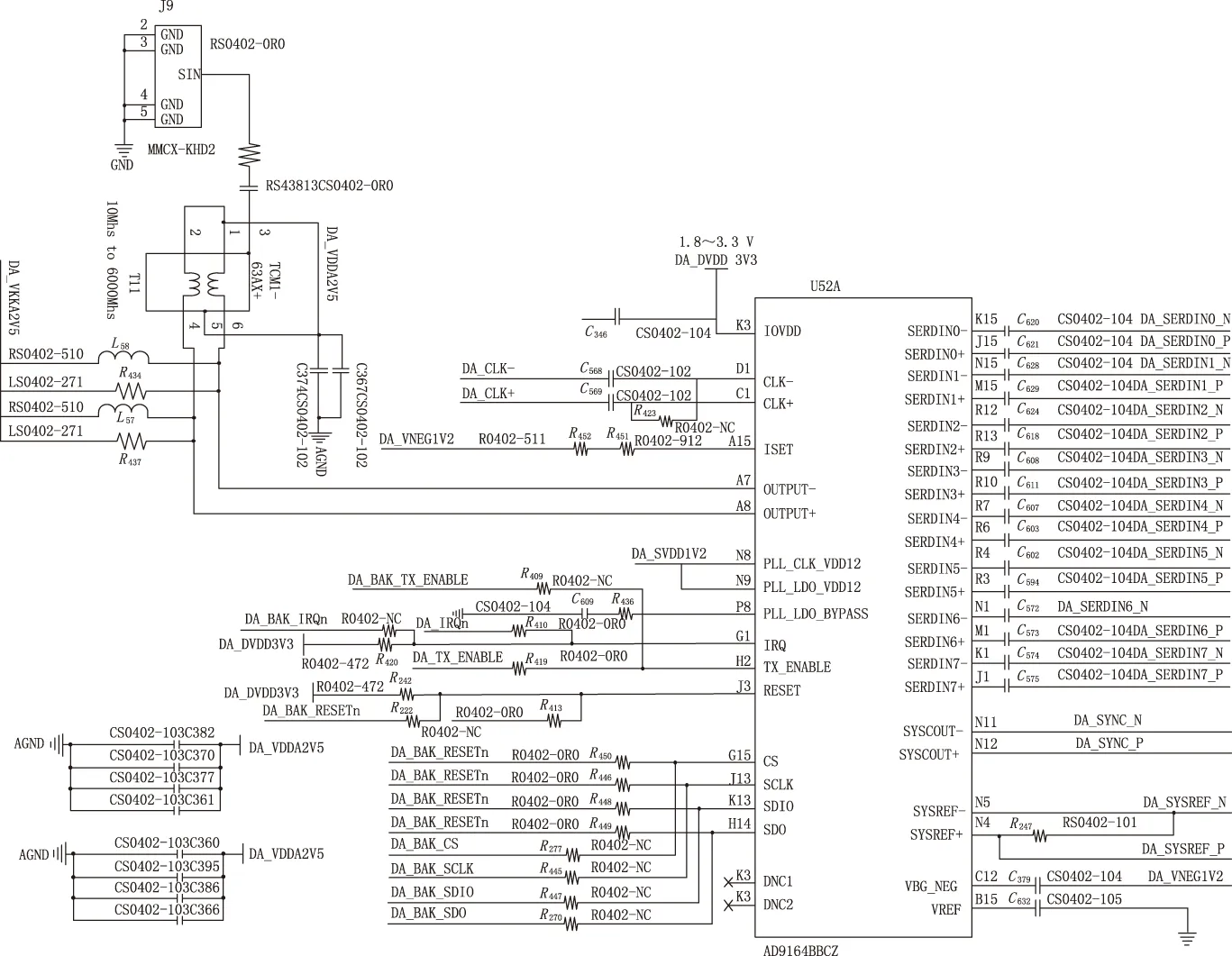

2.2 AD9164数字电路设计

AD9164电路如图5所示见59页。

2.3 收发信道模拟电路及本振源电路设计

收发信道模拟电路及本振源电路图如图6所示。

图4 FPGA控制流程图

图6 收发信道模拟电路及本振源电路设计示意图

3 测试验证

对采用该设计方案所生产设备的发射功率、发射频谱及接收动态范围进行测试,发射频谱测试结果如图7所示。

图7 发射频谱图

接收动态范围按照原指标进行仍能满足要求。相对于原设备指标,新设备的发射频谱及接收动态范围性能并未下降,但是在重量、体积、功耗方面大幅度减少。

4 结 语

本文提出了基于AD9164芯片的数字化本振设计及射频直发设计方案,给出了具体实现方法,并在设备上完成了该方案的验证。在保持性能指标不降低的情况下,有效减轻了设备的重量、体积及功耗,结合动态功耗管理技术可进一步降低设备功耗,为以后设备的小型化、轻量化设计提供了新的设计思路和实现方法,应用前景广阔。

图5 AD9164电路图

[1] 佚名.北斗一体化导航模块终端的设计实现[J].电子世界,2011(5):60-61.

[2] 佚名.ADI AD9164高性能16位DAC和DDS解决方案[J].世界电子元器件,2016(8):1-2.

[3] MKT H S .高速转换器的关键性能,将从三个方面改变世界[OL].https://ezchina.analog.com/thread/16507.

[4] JESD204串行接口和JEDEC标准数据转换器[OL].http://www.analog.com/cn/applications/landing-pages/001/jesd204-serialinterface-jedec-standard-data-converters.html.

[5] 杨秀增.基于FPGA的DDS信号源设计[J].电子设计工程,2009,17(11):7-8.

[6] 邓岳平,肖铁军基于FPGA的并行DDS信号发生器的设计与实现[J].计算机工程与设计,2011,32(7):2319-2323.

[7] 张峰,王站江.基于JESD204协议的AD采样数据高速串行传输[J].电讯技术,2014,54(2):174-177.

[8] 冉焱,席鹏飞.基于JESD204协议的高速串行采集系统[J].电子科技,2015,28(5):17-19.