基于DDR3 SDRAM的大容量异步FIFO缓存系统的设计与实现

孙冬雪 ,王竹刚

(1.中国科学院国家空间科学中心,北京100190;2.中国科学院大学计算机与控制学院,北京100190)

数据缓存在大数据实时采集系统中起着至关重要的作用。它具有多种实现方式:异步FIFO以先入先出的读写规则,不需要对读写地址进行操作、读写时钟独立等优点广泛应用于跨时钟域的数据采集传输系统中[1]。但是由于常见FPGA的片上FIFO容量大部分为MB等级,很难满足对大数据缓存的要求,同时FIFO地址由内部地址指针控制,不能由地址线决定读取地址,可移植性差。DDR3 SDRAM(Double DataRateSynchronousDynamicRandom Access Memory)的内存容量已经达到GB等级,完全可以对大量数据同时缓存,因此受到工程人员的青睐,但是由于DDR3不能直接像FIFO一样通过识别外界设置的读写使能来完成对数据的缓存,而是需要自己设计一个操作复杂的读写操作控制模块,这样加大了设计人员的开发时间和成本[2]。本设计基于以上所述,把FIFO和DDR3 SDRAM的优点结合起来,设计了一种大容量异步FIFO数据缓存系统。它可以直接通过识别外界的操作使能完成对大量数据的缓存,操作简单、速率快,可以用于大量数据实时采集系统中。

1 DDR3-SDRAM介绍

双倍速率同步动态随机存储器(DDR3 SDRAM)可以同时在时钟的上升沿和下降沿传输数据[3],其传输速率在不改变时钟频率的情况下是SDRAM的两倍。本设计基于KC705评估板,DDR3采用Micron公司的MT8JTF12864HZ-DDR3内存条,它内部配置有8个BANK,能够以8n预取结构获得高速操作,同时它采用先进的同步电路,读、写数据、命令和CPU同步又相互独立完成,8个BANK对应3根BANK地址选择线,行地址线复用14根、列地址线复用10根,通过8组数据线(DQ0-DQ7)来完成对外的通信,因此每个内存芯片的容量为8*2^3*2^14*2^10=128 MB,该内存条由8片同样的内存芯片构成,则内存条的容量为1 GB。将内存条的突发长度设置为8,每颗芯片含8根数据线(DQ0-DQ7),8片芯片放在一起,则每次读写操作的数据位宽为512位,大大提高了DDR3的读写效率[4]。

2 数据缓存系统设计

2.1 总体设计

本设计由DDR3 SDRAM控制模块、外部的DDR3 SDRAM、两片FIFO、FIFO控制模块和时钟复位模块构成。其总体框图如图1所示。

本设计采用分包传输,一包传输32*512 b=16 kb=2 KB数据。外界提供异步FIFO的写使能将数据输入到WR_FIFO中等待,当WR_FIFO的剩余数据量达到2KB且DDR3准备好时,将WR_FIFO的读使拉高,数据便被传输到DDR3中,当写入DDR3的数据达到2KB时,转向读DDR3状态,即RD_FIFO的写使能为1,将数据传输到RD_FIFO中。当收到用户的读请求后将数据从RD_FIFO读出,循环进行,就可以用DDR3模拟FIFO完成对数据的缓存。对于用户来讲,本设计是一个标准的大容量FIFO,用户可以直接根据自己的需求像FIFO一样对外部接口进行操作,不用关心其内部组成原理。

图1 系统总体框图

2.2 DDR3 SDRAM控制模块的设计

设计使用MIG核user design里的RTL来建立工程,首先在MIG核的GUI图形界面选择MT8JTF1 2864 Hz芯片、将DDR3的工作时钟设置为800 MHz、输入时钟设置为200 MHz、再对应开发版手册填好管脚约束等参数[5],即可生成DDR3 SDRAM控制器。控制器封装了用户逻辑到存储器逻辑的转换,我们只需要根据MIG核用户接口协议编写用户逻辑,根据自己的需求产生读写命令、地址、数据信息[6],DDR3 SDRAM控制模块的工作流程如图2所示。

图2 控制模块工作流程

DDR3 SDRAM控制模块用来产生读写DDR3 SDRAM的命令和数据存储的地址。整个设计依据DDR3提供的APP协议进行编写,在正常操作之前,DDR3 SDRAM必须要以预定义的方式上电和初始化。从外界输入200M的差分输入时钟,MIG产生DDR3的工作时钟800M,和整个系统的工作时钟200MHz[7]。将KC705的SW4作为复位信号经过DDR3产生的rst作为整个系统的复位信号,所有模块均采用高电平复位[8]。设计将控制器的200 M系统时钟经过MIG IP核中的锁相环倍频到800 M作为控制器的主时钟频率,由于DDR3能够在时钟的上下沿都传输数据,因此,其传输速度达到1600 M/S[9],数据宽度为64 bit。

2.3 片上FIFO设计

设计中采用两个小容量片上FIFO来解决整个数据传输过程由于读写时钟不同所带来的亚稳态问题[10]。片上FIFO采用Xilinx FPGA的异步FIFO标准IP来实现。WR_FIFO的读数据位宽设置为512 bit,RD_FIFO的写数据位宽设置为512 bit。它们的数据深度均设置为512。WR_FIFO的复位信号和用户控制逻辑模块相同,即高电平复位,低电平工作,它的写时钟和外部采集数据的时钟相同,读时钟和DDR3的用户时钟相同;它的读使能由用户控制逻辑模块控制(当DDR3准备好,即初始化成功、app_rdy和app_wdf_rdy均为1、且WR_FIFO内部剩余数据量达到2KB),其内部剩余数据量由rd_data_count提供。RD_FIFO的工作原理和WR_FIFO的工作原理类似,写时钟和DDR3的用户时钟相同,读时钟对应外部时钟,同理它的写使能也由用户控制逻辑模块控制,当状态机跳转到读时,将RD_FIFO的写使能拉高。

3 系统测试与分析

为了证明所设计的DDR3控制模块和FIFO缓存系统能正常工作,将设计生成的比特流文件下载到开发板进行测试。本次测试基于Vivado 2016.2,为了便于分析,采用Xilinx提供的片上调试工具Chipscope[11]来监测读写命令、数据等信号,和MIG时序以及写入数据作比较。

3.1 DDR3 SDRAM控制模块测试与分析

DDR3 SDRAM控制模块测试的基本原理:将由32个地址低16位组成的512bit数据作为写入数据输入到DDR3 SDRAM控制模块,采用写计数器计存进去的数据个数,当计到32个(2 kB)时等待20个时钟转向读DDR3状态,同理再用读计数器计读出来的数据个数,到32个以后等待20个时钟再转向写DDR3状态,循环读写,实现对DDR3 SDRAM控制模块的测试。

1)用Chipscope监测到的写DDR3波形如图3所示。

图3 控制模块写时序

上图中:phy_init_done(app_ini)的值一直为 1,说明初始化成功;app_rdy和app_wdf_rdy是内存条的输出信号,app_rdy表示硬件已经准备好,可以接收控制模块输出的命令操作,只有当它拉高的时候,地址app_addr才是有效的;app_wdf_rdy是ddr内部写FIFO满对应的信号,当它为0时,说明写FIFO已满,写入数据无效,只有为1时,app_wdf_data才是有效的,因为本次设计每包仅处理32组,写FIFO不会满,所以此信号一直为1;app_en、app_cmd、app_addr在时序上和app_rdy相对应,app_cmd是读写控制命令信号,用来控制数据写入还是数据读出,当为3’b000时说明当前在进行写操作,当为3’b001时说明当前进行的是读操作,在本模块中读写命令中间的等待时间 ,将 app_cmd赋值为 3’b111;app_addr(ddr_addr)由app_rdy控制用来控制写操作地址,当app_rdy拉低时,地址无效,所以它对应的地址应该如图3所示延时一个周期,DDR3的地址按照结构从高位到低位分别是Rank+Bank+Row+Column,由于本设计采用的DDR3的突发长度BL=8,写地址值以8为单位连续增加,将app_addr的初地址赋值为0,则app_addr低4位将如图3一直在0和8交替循环;app_en是操作地址的使能信号,上图它一直拉高说明app_addr有效[12-14];本次测试将由32个地址低16位组成的512 bit数据非阻塞赋值给app_wdf_data作为写入数据,则某一地址的数据由32个比自己地址低16位小1的512 bit数据组成,和图3对比可知写入的数据正确;app_wdf_wren是写入数据的接口使能信号,只有在它拉高的情况下app_wdf_data才是有效的;app_wdf_end保持和app_wdf_wren相同即可;每个控制周期对应一组突发数据(512bit),则每写入一次数据就要给出一个app_wdf_wren[12,15]。将图3和MIG的写时序图对比,可知此控制模块写设计满足DDR3写时序要求即写模块设计正确。

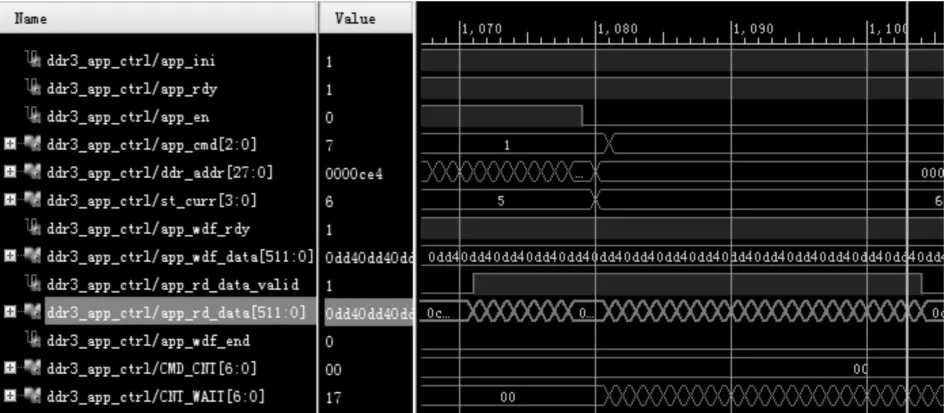

2)用Chipscope监测到的读DDR3波形如图4所示。

图4 控制模块读时序

上图中:phy_init_done的值一直为1,说明初始化完成;app_cmd=3’b001,表示当前进行读操作;app_addr(ddr_addr)用来操作读地址,只有在app_rdy和app_en都拉高的情况下地址才是有效的。从图4可知:在给出读地址和读命令,隔一段时间才收到DDR3发出来的读数据,因为在DDR内核里,地址、命令和读数据是两套不同的系统,DDR需要反应时间,所以读数据会相对读命令有所延迟。app_rd_data则是读数据接口,app_rd_data_valid拉高表示app_rd_data有效[16]。从上图可知读出来的这一包数据的最后一个数和这一包写进去的最后一个数完全一致,再和读地址对比发现某一地址读出来的数据由32个比地址低16位小1的512 bit数据组成,和写数据完全对应,证明该控制模块能够正确的对DDR3 SDRAM进行读写操作。将图4和MIG的读时序图对比,可知此控制模块设计满足DDR3写时序要求,验证了此模块的正确性。

3.2 异步FIFO缓存模块测试与分析

该缓存设计对用户来说是一个标准的大容量FIFO,用户只需要提供存储的数据、使能信号、时钟、位宽,不用关心其内部操作。为了测试该系统的性能,采用如图5所示框架进行验证。

图5 测试系统框图

上图基本的工作原理:在FPGA内部通过逻辑产生存储数据流,将他们通过待测试的异步FIFO系统缓存后,将输出数据流用Chipscope监测,通过改变FIFO的时钟和相应输入输出数据宽度,便可实现此系统在不同时钟域下的高速数据传输,通过比较Chipscope显示的数据和逻辑产生的数据是否一致,便可以判断系统设计是否正确。

分别用逻辑产生不同位宽的模拟输入数据,对应不同的测试时钟。通过待测试的缓存系统,多次实验证明:Chipscope显示的数据和逻辑产生的数据一致,此系统设计正确。

4 结论

本设计由硬件描述语言verilog编写完成,它结合了DDR3和FIFO的优点,操作简单、容量大、移植方便,又可以完成数据的跨时钟域传输,实用性高、可继承性好。通过VivadoChipscope对异步FIFO系统调试,验证了本设计的正确性。经过测试,本设计实现了最高480M的数据传输率,64~512位的总线宽度,容量最大为1 GB,可以用来缓存高速实时采集系统所采集的数据。

参考文献:

[1]马其琪,鲍爱达.基于DDR3 SDRAM的高速大容量数据缓存设计[J].计算机测量与控制,2015(9):3112-3113,3118.

[2]丁宁,马游春,秦丽.基于FPGA的DDR3-SDRAM控制器用户接口设计[J].科学技术与工程,2014(17):225-229.

[3]张剑.一种基于FPGA的Virtual FIFO控制器的设计与实现[C]//中国计算机学会.第十八届计算机工程与工艺年会暨第四届微处理器技术论坛论文集,中国计算机学会,2014:7.

[4]杨金宙,徐东明,王艳.基于FPGA的高速数据采集系统设计与实现[J].中国集成电路,2017(Z1):20-23,34.

[5]张刚,贾建超,赵龙.基于FPGA的DDR3 SDRAM控制器设计及实现[J].电子科技,2014(1):70-73.

[6]宗凯.基于FPGA的DDR3控制器设计[J].电子测量技术,2017(1):118-122.

[7]王红兵,强景,周珍龙.Xilinx MIG IP核的研究及大容量数据缓冲区的实现[J].电子产品世界,2016(8):43-46.

[8]KC705 Evaluation Board for the Kintex-7 FPGA ug810(v1.0)[EB/OL].[2014-03-21].http://www.xilinx.com/warranty.htm.

[9]潘一飞,余海.基于FPGA的DDR3用户接口设计[J].电子制作,2013(15):9-10,16.

[10]李玉发,孙靖国,李涛.一种高速大容量异步FIFO的实现方法[J].航空计算技术,2015(5):114-116,120.

[11]ChipScope Pro Logic Analyzer tool[EB/OL].[2014-02-17].http://www.xilinx.com/tools/cspro.htm.

[12]7 Series FPGAs Memory Interface Solutions[EB/OL].[2014-02-11].http://www.xilinx.com.

[13]余壮志.基于FPGA的多通道高频信号采集和存储研究[D].湘潭:湘潭大学,2015.

[14]刘杰,赛景波.基于DDR2SDRAM乒乓双缓冲的高速数据收发系统设计[J].电子器件,2015(3):650-654.

[15]李鹏.高速大容量存储器的控制器设计与验证[D].西安:西安电子科技大学,2015.

[16]李元兵,姚远程,秦明伟.DDR3-SDRAM控制器设计及FPGA实现[J].自动化仪表,2016(8):5-7,12.