基于MicroBlaze软核的等精度频率计设计

韩瑞,张莹莹,杨文,陈华宝

(淮阴师范学院 物理与电子电气工程学院,江苏淮安,223001)

0 引言

频率计是一种专门对被测信号频率进行测量的电子测量仪器,能够快速准确地捕捉到被测信号频率的变化。在电子技术中,频率与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率计在科学研究、精密测量和工业控制等方面都有着较广泛的应用。针对传统的频率计存在结构复杂、稳定性差、精度不高且成本较高等缺陷,本文基于MicroBlaze软核设计的等精度频率计,可实现对被测信号频率、周期、脉冲宽度和占空比的测量及显示。

1 等精度频率测量原理

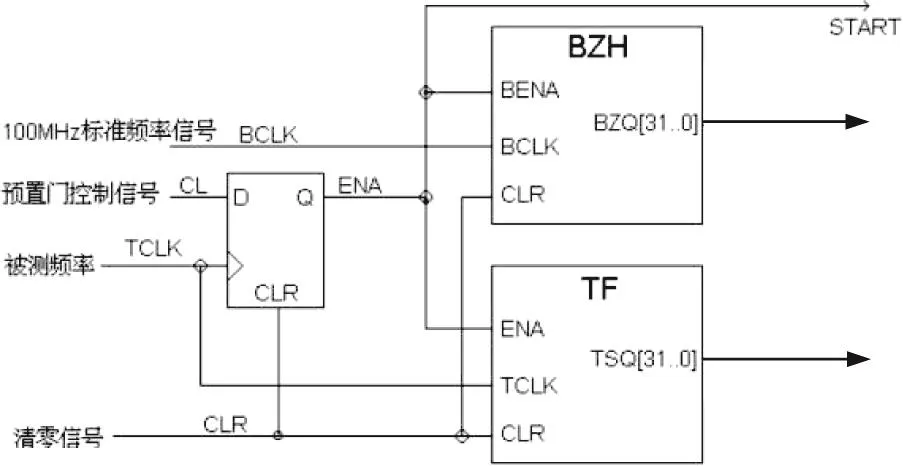

等精度频率计测频原理如图1所示。当控制器发出预置闸门控制信号CL,并且被测信号上升沿到来时D触发器有输出,使能两个计数器BZH、TF,分别对标准信号和被测信号进行计数;当控制器关闭预置闸门控制信号CL,并且被测信号上升沿到来时D触发器输出为零,两个计数器同时停止计数。其时序如图2所示,由于采用D触发器实现预置闸门的同步作用,TF计数器所记录的NX值已不存在误差的影响,而时钟信号与闸门的开和关无确定的相位关系,BZH计数器所记录的NS的值仍存在±1误差的影响,但由于时钟频率很高,对误差影响很小,所以在全频段的测量精度是均衡的,从而实现等精度频率测量。显然在实际的闸门时间内有:

由于t为Nx周期的整数倍,因而Nx的正负误差为0,即DNx=0,又 DNs=±1,Dfs=0,则 :

图1 等精度测频原理图

图2 等精度测频时序图

由上式可看出测量频率的相对误差与被测信号的频率的大小无关,仅与闸门时间和标准信号频率有关。闸门时间越长,标准频率越高测频的相对误差就越小。标准频率可由稳定性好,精度高的高频率晶振产生,在保证测量精度不变的前提下,提高标准信号频率,可使闸门时间缩短,即提高测试速度。

2 系统设计方案

系统主要由放大整形电路、片上等精度测频模块以及显示模块等部分组成,其整体框架如图3所示。被测信号经过放大整形电路处理后,输出原频信号和64分频信号到选择门,当被测信号频率大于30MHz,自动切换到64分频输入。测频模块通过其MicroBlaze嵌入式软核和Verilog HDL设计的外围功能模块完成测量控制与数据处理,最后采用LCD12864,将所测信号的频率、周期进行实时显示。

图3 系统结构方框图

3 系统硬件设计

3.1 前置调理电路设计

由于被测高频小信号不能由数字系统直接进行处理,故要对被测信号进行前置放大调理,其电路组成如图4所示。首先通过场效管2N5485隔离放大,再通过高频运放MC10116进行整形放大,整形后的信号分为两路输出。

图4 前置调理电路组成框图

3.2 片上等精度测频模块设计

测频模块主要由选择门、预置阀门、与门、被测信号和标准信号计数器以及Microblaze软核等组成,其结构如图3所示。选择门由Microblaze软核控制将被测信号送给与门,当其输出端有信号时,使能两个计数器分别对标准信号和被测信号进行计数,从而得到Microblaze软核测算频率所需的数据。

3.3 显示模块设计

等精度频率测量模块测得的频率数据通过MicroBlaze软核进行处理显示,显示模块采用LCD12864液晶显示。

4 系统软件设计

4.1 测频程序设计

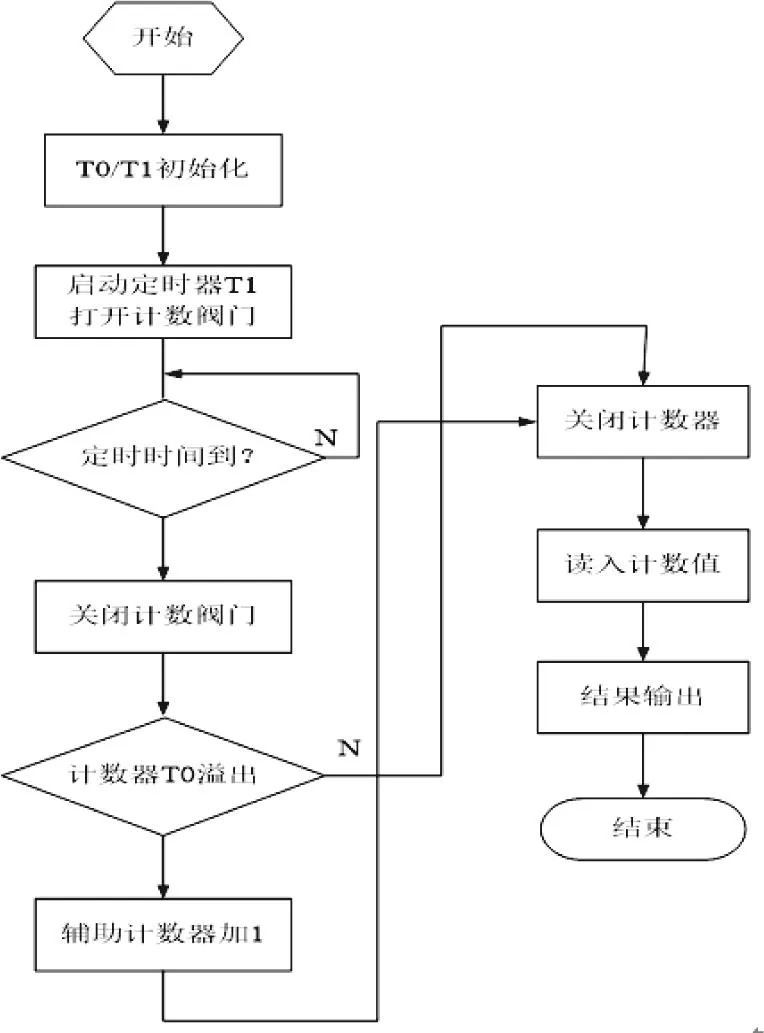

图5为测频程序设计流程图。在VIVADO软件开发环境下,利用Verilog语言,依据等精度频率测量的原理,由MicroBlaze软核发出计数指令,计数器在规定的时间内完成计数,并把计数值进行返还,MicroBlaze软核读入计数值并对其进行处理。

图5 测频程序流程图

图6 主控程序流程图

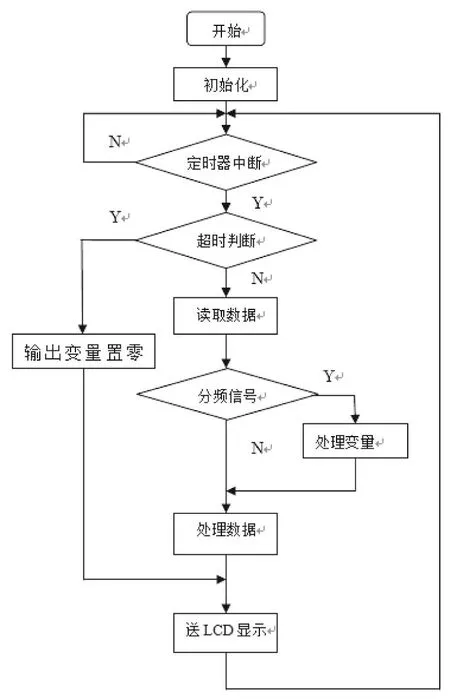

4.2 主控程序设计

图6 为主控程序设计流程图。系统将VIVADO中硬件描述语言综合编译生成的bit文件导入到集成开发环境SDK(Software Development Kit)中,进行C语言编程实现频率计的逻辑功能。闸门时间由定时器控制,其默认时间为1s。当定时器产生中断,控制器关断闸门预置信号CL,计数器停止计数,如果闸门监测信号EEND为零,读取计数器计数值,对数据处理送LCD12864显示,然后开启预置信号CL、使能异步复位信号CLR对计数器清零进入下一次循环。

5 结束语

随着电子技术的不断发展,现场可编程门阵列被广泛用于硬件系统中的逻辑控制与通信中,芯片生产家推出越来越多可靠并且功能强大的IP核,尤其是软件处理核,凸显了FPGA作为主控芯片的优势,从而使得FPGA在越来越多的电子产品中被使用。本文在FPGA芯片上基于MicroBlaze软核设计的等精度频率计不仅大大减小了频率计硬件电路的尺寸,而且提高了整体电路的稳定性、可靠性。

参考文献

[1]林建英,高苗苗,杨素英.基于SOPC的等精度数字频率计设计[J].国外电子测量技术,2012,29(12):55-13.

[2]莫琳.基于FPGA的等精度频率计的设计与实现[J].现代电子技术,2004,177(10):081-084.

[3]刘永健.软核嵌入处理器MicroBlaze[J].计算机与网络,2012,15:64-36.