高速ADC中具有失调对消的采样保持电路设计

刘勇聪,王建业,连 振

(空军工程大学防空反导学院,西安 710051)

0 引言

超宽带雷达和通信系统的迅速发展对模数转换器(ADC)采样速率的要求越来越高。而采样保持电路(THC)可大幅度提高ADC的动态性能,在设计超高速ADC时,THC是必不可少的部分,其直接决定ADC的采样速率、带宽、线性度等性能。随着采样速率的增加,ADC内部的失调,尤其是比较器失调越发明显,严重影响ADC整体性能,因此,消除ADC高速采样时的失调量十分必要。在已有的失调消除技术中,文献[1-2]介绍了电阻平均失调对消技术,文献[3]采用电容平均消除失调技术,而文献[4]则运用综合电阻、电容平均技术来消除失调,文献[5]采用数字修调技术消除失调量。本文从THC和比较器结构出发,通过采样电容存储失调量,来抵消比较器失调电压,实现失调对消。相比于已有的失调对消技术,其在电路复杂度上具有明显优势,减小了物理实现的难度。并且在综合性能上,也优于其他失调对消技术。

1 传统高速ADC中的THC

传统 THC 有闭环[6]和开环结构[7],由于闭环结构的反馈电路将限制ADC的采样速度,高速ADC中的THC一般使用如图1所示的开环结构:

由S采样开关,CH保持电容,输入缓冲A1与输出缓冲A2共同构成THC。由采样保持电路阵列组成的预放大电路作为锁存比较器的前端,可改善ADC对输入信号的敏感度,减少比较时间,提高速度。传统Flash ADC前端结构如图2所示:

传统ADC结构中,无论是采用电阻,电容平均技术消除失调,还是采用数字修调技术,都需要加入复杂的额外电路,物理实现起来较为困难,功耗也会随之增加。而本文设计的消除失调的THC在几乎不增加电路复杂度的前提下,实现了失调对消,并且加入的开关电容电路也几乎不增加功耗。

2 具有失调对消的THC

2.1 失调对消原理

在设计传统THC时,需要考虑线性度。而具有失调对消的THC在实现高速采样和保持的同时,由于采用全差分结构,本身就具有高线性度。其基本结构如图3所示:

不同于传统的THC,具有失调对消的THC的保持电容和采样开关的位置改变,两级预放大器不仅可提高比较器锁存速度,而且可通过时钟控制采样开关 S1、S2,实现电路工作相位 φ1,φ2的交替变换从而消除电路的失调量。相位φ1时,对输入信号与失调分量进行采样放大,而在相位φ2时,只对失调分量进行反向采样放大,一个时钟周期中,相位φ1和φ2的输出累加便可消去电路的失调分量,实现失调对消。

2.2 失调对消过程

通过电路工作相位交替变换,实现电路失调对消的具体过程如下:

电路工作在相位φ1时,开关S1闭合,S2断开,THC等效电路如图4所示。THC前级对输入信号进行采样放大,后级对失调信号Vioff进行采样放大,输入信号Vin存储在电容CA1和CA2中,失调信号Vioff存储在电容CB1和CB2中。在相位φ1时,输出Vout为:

当开关S1断开,S2闭合,电路工作在相位φ2时,此时THC等效电路如下页图5所示。

由于输入端被短接,此时无信号分量,只对失调分量Vioff进行采样,由于Vcm被短接,所采样的失调量Vioff被反向放大,后级对φ1时的采样信号Vin和失调分量Vioff进行同相传输,而对失调分量Vioff进行反向采样。相位φ2时,输出Vout等效为:

当相位φ1,φ2交替变换时,对信号Vin和失调分量Vioff都可进行放大,而在相位φ2时,只对失调分量Vioff进行采样,由于输入端和Vcm被短接,失调分量被反向放大,结合式(1)和式(2)可知,累加之后的Vout变成了:

由式(3)可知,失调量理论上可被完全消除。

3 失调对消THC的电路实现方法

前级双差分输入放大器的电路组成如图6所示:

其中,交叉耦合MOS电容的引入可以对消密勒电容,减小输入阻抗。开关S1,S2可通过时钟控制,从而实现相位φ1,φ2的交替变换。

后级差分输入放大器组成如图7所示:

其中,S2的加入可以减少S1闭合时,耦合到输出端的电荷。为提高电路工作速度,开关S1选择共源共栅开关电路[8],开关S2的与之对应相位相反。电路实现如图8所示。

通过改变MOS管M1的栅压Vg来控制开关S1。通过引入Cascode结构,可提高M1导通时的电流,加快了后级采样电容的充电速度。同时,对时钟信号电压摆幅的要求也降低了。

4 仿真结果分析

采用UMC 0.18um CMOS工艺,对应用失调对消THC的Flash ADC进行输入为500 mVp-p,频率为200 MHz~1 000 MHz的信号在2 GHz时钟频率进行仿真。由于Flash ADC一个时钟周期可以完成一次采样,所以该ADC采样速率为2 GS/s。图9表示不同频率输入信号下无杂散动态范围(SFDR),信号-噪声和失真比(SINAD)的仿真结果。

仿真结果表明,在2 GS/s的采样速率下,所得出的SFDR基本稳定在45.0 dB以上,而SINAD在输入为700 MHz频率出现最低值,也能达到33.1 dB。

图10表示有效位数(ENOB)在不同输入频率下的仿真结果。

可以看出,不同输入频率下的ENOB基本稳定在5.4 bits左右。

通过以上仿真结果可以看出,Flash ADC的动态性能随输入信号的变化而基本保持稳定,由此可知失调分量Voff得到了有效的抑制。

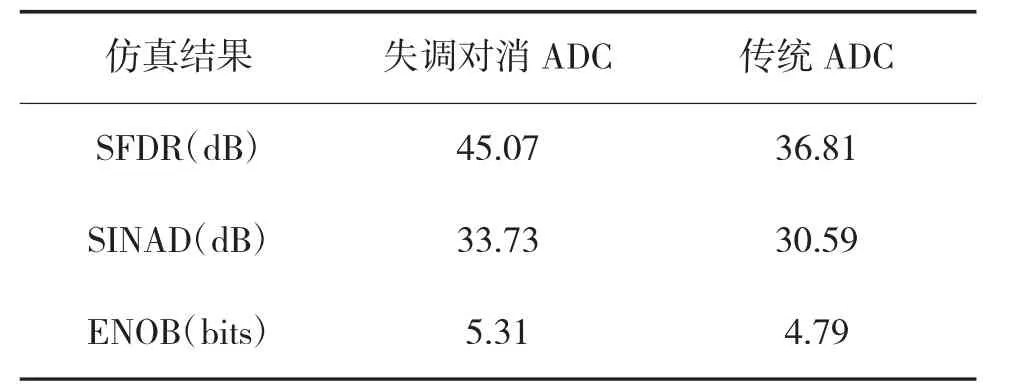

为验证具有失调对消THC对Flash ADC动态性能的提升,选取800 MHz输入信号时仿真结果与传统Flash ADC进行对比,仿真结果如表1所示:

表1 与传统THC仿真结果比较

相比较于传统ADC,应用失调对消THC的Flash ADC的SFDR,SINAD分别提高了 8.26 dB,3.14 dB,ENOB也提高了0.52 bits。证实了具有失调对消THC对高速ADC动态性能的提高。

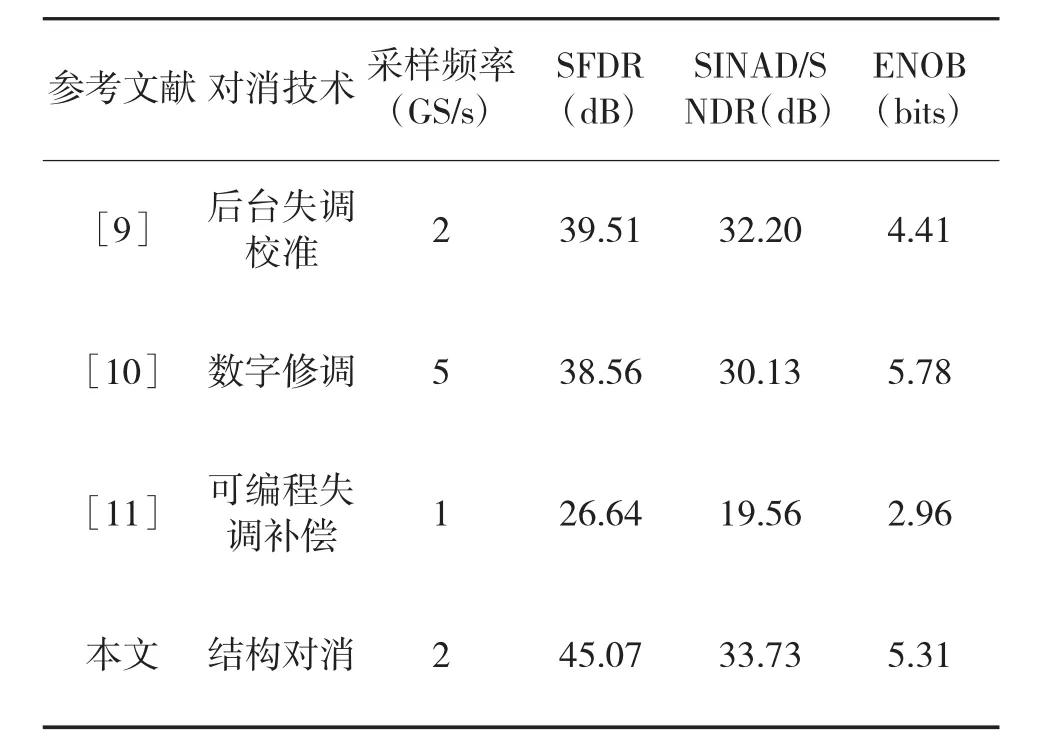

与已有的失调对消技术进行比较,THC结构对消的方法也具有一定的优势。其仿真动态性能参数如表2所示:

表2 与不同失调对消技术仿真结果比较

5 结论

本文介绍了一种具有失调对消的THC结构,该THC不仅可提高ADC的动态性能,而且在实现和功耗上更具有优势。随着ADC采样速率不断地提高,具有失调对消的THC对进一步提高ADC的采样速率、动态性能有着非常重要的意义。对于失调失配较为严重的多通道ADC,具有失调对消的THC也具有一定的参考意义。

参考文献:

[1]GUAY N G,HANSEN C W,ROBINSON C D,et al.Improving module temperature measurements using averaging resistive temperature devices[C]//Photovoltaic Specialists Conference(PVSC),2016:3132-3134.

[2]LI X J,YANG Y T,ZHU Z M.A 1.8V 100MS/s 10-bit pipelined folding A/D converter with 9.49 ENOB at nyquist frequency[C]//2011 IEEE 9th International Conference ASIC(ASICON),2012:476-479.

[3]LEE P C,LIN J Y,HSIEH C C.A 0.4 V 1.94 fJ/conversion-step 10 bit750 kS/s SAR ADC with Input-Range-Adaptive Switching [J].IEEE Transactions on Circuits and Systems I:Regular Papers,2016,63(12):2149-2157.

[4]FAN S Q,TANG H,ZHAO H.Enhanced offset averaging technique for flash ADC design [J].Tsinghua Science and Technology,2011,16(3):285-289.

[5]YAOJJ,LIUJ,LEEH.Bulkvoltagetrimmingoffsetcalibration for high-speed flash ADCs [J].IEEE Transactions on Circuit sandSystems-II.ExpressBriefs,2010,57(2):110-114.

[6]BOUVIER Y,OUSLIMANI A,KONCZYKOWSKA A.A 40 GSamples/s InP-DHBT track-and-hold amplifier with high dynamic range and large bandwidth[C]//IEEE,IET International Symposium on Communication Systems,Networks and Digital Signal Processing(CSNDSP),2012:1-4.

[7]LIU Y C,CHANG H Y,HUANG S Y,et al.Design and analysis ofCMOS high-speed high dynamic-rangetrack-and-hold amplifiers[J].IEEE Transactions on Microwave Theory and Techniques,2015:63(9):2841-2853.

[8]HEATHER O,ANAND G.A 20 GS/s 1.2 V 0.13 μm CMOS switched cascode track-and-hold amplifier [J].IEEE Transactions on Circuits and Systems-II:Express Briefs,2010,57(7):512-516.

[9]BA-RO-SAIM S,CHANG K L,WAN K,et al.A 6 bit 2 GS/s flash-assisted time-interleaved(FATI)SAR ADC with background offset calibration [C]//IEEE Asian Solid-State Circuits Conference(ASSCC),2013:281-284.

[10]VASSOU C H,MOUNTRICHAS L,SISKOS S.A NMOS bulk voltage trimming offset calibration technique for a 6-bit 5GS/s flash ADC [C]//2012 IEEE International Instrumentation and Measurement Technology Conference(I2MTC),2012,pp:13-16.

[11]MARINA Z,SEYED A Z,MARVIN O.Digitally programmable offset compensation of comparators in flash ADCs for hybrid ADC architectures[C]//2015 IEEE 58th International Midwest Symposium on Circuits and Systems(MWSCAS),2015:2-5.