一种实用突发CSK/SS通信系统的设计与实现

邓雪群

(中国电子科技集团公司第十研究所,四川 成都 610036)

0 引言

测控与信息传输系统是高速无人飞行器信息电子系统的核心之一,它在传统飞行器统一测控系统的跟踪、测轨、遥控、遥测及载荷数据传输“四合一”功能基础上[1],综合了任务规划与指挥控制功能。其中的遥控、任务指挥控制功能主要由视距测控通信链路与超视距测控通信链路互为补充完成。

与传统飞行器测控相比,高速无人飞行器视距测控通信需解决如下问题[2-3]:① 复杂电磁环境下的强抗干扰、优越低截获性能传输需求;② 高动态环境下导致较大的多普勒频移问题;③ 战场边缘应用及平台的随机摆动与反射,会造成信号电平严重衰落,以及低仰角多径效应问题。采用扩频通信技术是解决上述问题的一种技术途径,但扩频通信传输速率、扩频增益、信号带宽的相互制约,突发方式下的传输效率与快速同步的矛盾,以及工程实现时算法精度与硬件资源的矛盾都是技术难题。因此,本文设计了一种实用的突发码移键控扩频通信系统,从理论推导及仿真验证的角度分析上述问题的解决思路,并基于精度、速度、资源均衡原则对解调接扩、同步等算法进行优化设计,使其适用于实际工程实现,对其他测控与信息系统的工程设计具有一定参考意义。

1 系统设计

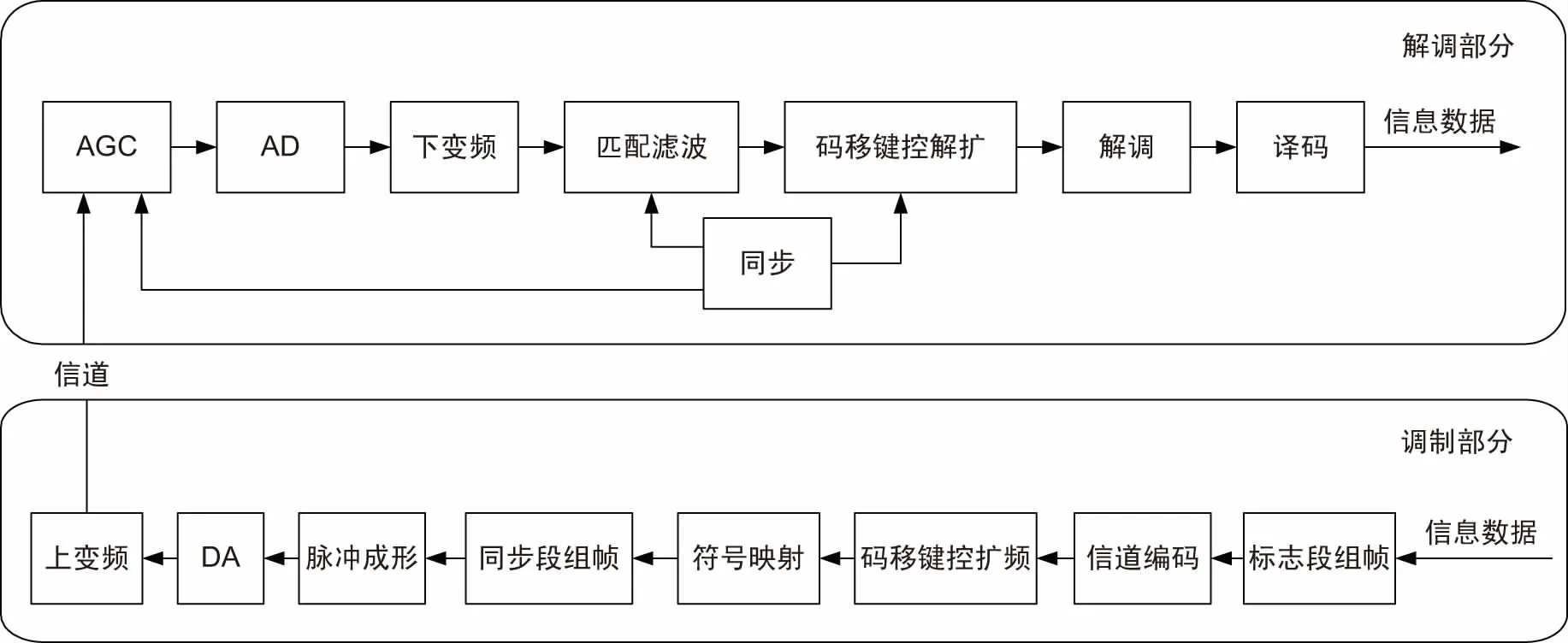

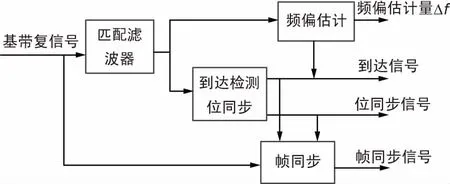

系统采用DBPSK+码移键控扩频调制,伪随机(Pseudo Noise,PN)码长为127位,码速率为8 MHz。为适应突发扩频通信系统,设计帧结构由同步段、标志段和数据段3部分构成。同步段主要完成突发信号到达检测、自动增益(Automatic Gain Control,AGC)控制、频偏估计、伪码同步、位同步和帧同步等功能。标志段用于传送消息长度、纠错方式和数据发送模式等有效信息。数据段用于传输用户数据。系统设计原理框图如图1所示。

图1 系统原理

2 调制算法设计与实现

调制部分工作流程:串行输入用户数据经信道编码后串并转换形成4路信息流,前3路信息用于控制扩频码的选择,第4路信息差分编码后与选出的扩频码进行正反码选择,然后经符号映射、同步段组帧、脉冲成型得到基带数据。基带数据经DA转换、低通滤波、模拟中频调制,产生中频码移键控扩频调制信号,送入信道分机。

信道编码设计采用循环冗余校验(Cyclic Redundancy Check,CRC)编码、RS编码、卷积编码、加扰和交织,加扰的目的是保证传输数据的随机性,使信号频谱弥散而保持稳恒,对同步提取、降低信号峰值—平均值功率比有重要意义[4],交织的作用则是把突发错误离散为随机错误,以保证纠错码的有效性。扩频码选用自、互相关性良好、码型数量较多的平衡Gold码,具有较好的频谱特性,有利于载波抑制。脉冲成型滤波采用平方根升余弦滚降滤波器,滚降系数取0.35。

3 解调算法设计与实现

解调部分工作流程:中频信号经带通滤波、可变增益放大器(Variable Gain Amplifier,VGA)电路调整、AD采样得到数字码流送入FPGA解调,在FPGA中对其进行数字下变频、匹配滤波,得到I、Q两路基带信号,经同步后送码移键控解扩解调,信道译码后输出原始用户信息。

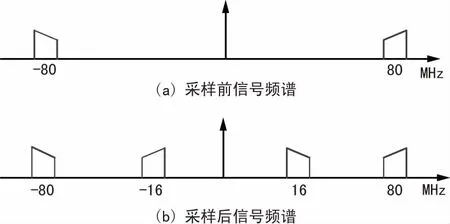

3.1 采样率的确定

本系统接收中频信号中心频率fIF=80 MHz,带宽B=PN码速率(1+滚降系数)=10.8 MHz,适合采用带通采样定理。为满足窄带中频信号无混叠采样条件,带通信号采样率fs应该满足如下充要条件[5]:

(1)

式中,fH为带通信号的最大频率点;fL为带通信号的最小频率点;N为整数,其取值范围为:

(2)

式中,int(·)表示取整数。

为便于数字下变频后的抽取处理,采样率的选取通常需保证采样后的数据速率为PN码速率的整数倍。同时为简化电路设计,系统采用单路A/D实采样,为减小频谱混叠,则要求采样率至少为PN码速率的8倍以上。这里取12倍基带码元速率fs=96 MHz。带通采样的频谱搬移如图2所示,信号从高中频变换到低中频fLF=fIF-lfs=16 MHz,其中l是使fLF的绝对值最小的自然数,本方案设计中l取1。

图2 A/D采样频谱搬移示意

3.2 数字下变频

数字下变频作用是将A/D采样后的数字信号从低中频搬移到基带,同时根据同步模块计算的频率偏差估计值对信号进行校正,并实现采样率的变换。

假设收发端存在载波频率偏差Δf,A/D带通采样后的低中频分量可表示为:

rLF(t)=d(t)c(t)cos[2π(fLF+Δf)t],

(3)

式中,d(t)表示基带波形;c(t)表示扩频波形;载波功率归一化为1。

对rLF(t)混频、低通滤波后即得到基带信号为:

rB(t)=d(t)c(t)ej2πΔft。

(4)

A/D采样数字信号经混频到零中频后,输出到低通滤波器以滤除倍频分量,然后进行抽取,降低样本速率,以利于后续信号处理。低通滤波器同时实现了抽取前的抗混叠滤波功能。基于处理精度、资源和计算速度的综合考虑,后级匹配滤波处理要求采样速率至少为PN码速率4倍以上,因此选取抽取因子为3。

数字下变频实现框图如图3所示,由数控振荡器(Numerically Controlled Oscillator,NCO)、混频器(乘法器)、低通滤波器和抽取器组成。

图3 数字下变频实现原理

3.3 匹配滤波

匹配滤波的目的是从4倍符号采样的数字信号中恢复出具有最佳采样点的信号,与调制部分的脉冲成型滤波器对应,采用相同滚降系数的平方根升余弦滚降滤波器对数据进行FIR滤波。

3.4 码移键控扩频解扩/解调

系统的扩频调制采用PN码和数据符号同步的方式,即一个数据符号转换点对应着一个PN码周期的转换点,扩频码周期也不太长,因此可采用数字匹配滤波器进行数字相关解扩,在解扩的同时实现信息解调,并且达到PN码快速捕获的目的[6]。

匹配相关输出相关函数可表示为:

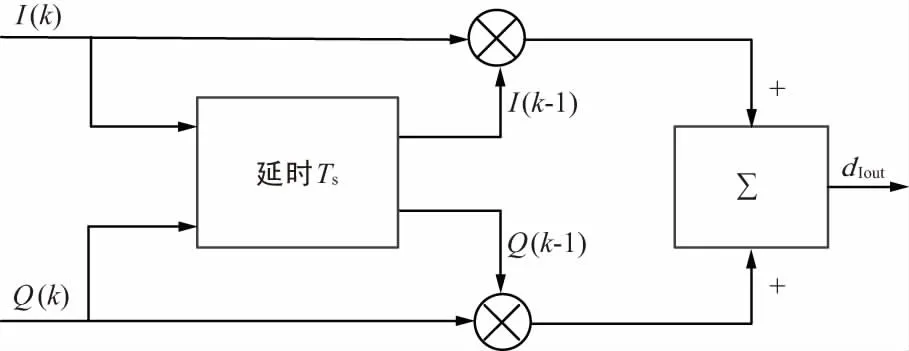

0≤τ (5) 式中,Ts为一个PN码周期的时间长度。 ① 当载波频偏Δf=0时, R(kTs+τ)=d(k)Rc(kTs+τ), (6) (7) 式中,d(k)为接收的第kTs时刻差分用户信息;Rc(kTs+τ)为扩频波形c(t)的相关函数。 ② 当载波频偏Δf≠0时,载波频率偏差会对相关峰各样值点幅度带来不同程度的衰减。此时,若接收信号与本地PN码波形完全匹配,输出相关函数峰值为: R(kTs)=d(k)ej2πΔfkTssinc(ΔfTs)。 (8) 从上述定量分析可以看出,匹配滤波器的输出R(kTs+τ)是一个与PN码同周期的周期函数,幅度受用户数据符号调制。载波频偏对相关峰峰值的影响是会产生一个sinc函数衰减因子。因此,相关解扩前先做载波频偏纠正,在相关峰最大值处采样即可解调出差分信息d(k)。 系统实现时设计采用16个PN码相关器代替I、Q两路16个匹配滤波器,在位同步时钟控制下对相关器运算结果进行采样、清零处理,这样,每127×4=508个时钟周期输出一组8个样值,输出峰值的相关器序号即对应着解调信息的前3位。这种方案的运算量是匹配滤波器实现方案的1/508,并且不占用延时寄存器单元。另外,为便于数字电路实现,相关峰幅度计算由式(9)近似算法来替代: SMAG=max{abs(I),abs(Q)}+ (9) 式中,I、Q分别表示I路、Q路相关器输出信号。 DBPSK解调采用延迟差分解调方式,输入基带差分信号d(k),I(k)和Q(k)分别表示d(k)的实部和虚部,A(k)和φ(k)分别表示d(k)的幅度和相位,其复数表示如下: d(k)=I(k)+jQ(k)=A(k)ejφ(k)。 (10) 延迟差分解调输出信号为: A(k)A(k-1)ej(φmod(k)+Δφrot(k)), (11) 式中,Δφmod(k)表示由于调制而引起的相邻符号间的相差;Δφrot(k)表示由于收发频差而引起的相邻符号间的相差。 对于DBPSK信号,相邻符号间调制相差Δφmod(k)为0或π,经过频偏纠正后Δφrot(k)≈0,因此可通过dout的实部进行符号判决获得解调信息,dout的实部可用其内积表示: dIout(k)=I(k)I(k-1)+Q(k)Q(k-1)。 (12) 延迟差分解调方式实现原理框图如图4所示。 图4 DBPSK信号解调实现原理 由于收发时钟频率源的异步工作以及频率的漂移、扩频序列的启动时差、电波传播的时延、多普勒频偏、多径效应以及突发时间的不确定性等因素[7],会造成扩频通信系统收发两端的不同步。而突发模式的扩频通信中,往往为了抗侦收、抗截获,突发时隙较短,要求系统快速、准确地建立同步。传统的锁相环路同步方法不能满足其同步时间要求。本系统采用同步头方式,设计了一种开销小、快速同步的算法,其实现原理框图如图5所示。下面介绍其详细算法设计。 图5 同步算法实现原理 3.6.1到达检测 突发通信的信号到达检测至关重要,决定着AGC能否正常起控以及后续的同步能否准确建立。同时,由于信号在传输过程中不可避免地受到噪声、干扰和频偏等影响,导致相关峰幅度衰减、丢失或出现假的相关峰,信号到达检测算法的设计必须充分考虑降低假同步、漏同步概率。目前熟知的检测方法有3种[8-9]:滑动相关能量检测(只适用于正信噪比条件)、序列相关检测(同步头开销大)、相关峰检测(并行检测,耗费资源),本系统综合考虑后采用相关峰检测法,算法设计如下: 设计多个连续的时间窗,每个窗口的时间长度等于一个PN码周期,如图6所示(图中以4个相关峰为例)。同时,在所有大的时间窗内的相同位置处设置小的时间窗,窗口长度大于相关峰宽度(8个时钟周期),设为40。在小时间窗内搜索最大值,如果所有时间窗内最大值出现的位置均相同,也就是检测到多个连续的相关峰,则判决信号到达。 图6 相关峰检测原理 实际通信过程中因多径、多普勒频偏、信道噪声以及干扰等影响,相关峰可能丢失或出现随机相位抖动。仿真分析发现,噪声会导致相关峰随机衰减,频偏对每一个相关峰的衰减是一致的,但它是导致相关峰幅度严重衰减的因素,同时导致相关峰主瓣和旁瓣的比值大大减小。因此,该算法实现时需将相关峰个数门限适当降低,相关峰发生一两个点的漂移时也判决为最大值出现位置相同,以减小漏同步的概率。仿真1 000次,结果显示信噪比不小于-9 dB、多普勒频偏不大于25 kHz时该算法无漏检。 3.6.2伪码同步、位同步 系统设计一个数据符号转换点对应一个PN码周期的转换点,并且同步段、信息段和数据段所用PN码长度相同,信号到达检测的同时也实现了伪码同步、位同步的粗同步。但由于每一个码片内有4个采样点,粗同步时刻可能在相关峰最大值处提前几个点或相关函数的旁瓣峰值处,伪码同步、位同步的精确同步算法设计如下:粗同步时刻存储相关函数值最大的一路所有大时间窗内样值,然后分别搜索每个时间窗内的最大值时刻,出现峰值最多的时刻即为位同步时刻。 需要说明的是,本系统为短时突发通信系统,不适合采用复杂符号同步算法对符号时钟进行精确跟踪,经过上述同步处理后,符号误差已在±1/8符号宽度内,对后续符号判决基本没影响。 3.6.3帧同步 帧同步的建立决定着信道译码的起始,是减少漏帧、错帧的关键算法。系统设计在位同步码后添加特别的识别器序列“0 0 0 1”作帧同步,识别器序列的选择要求序列具有小的自相关旁瓣,与同步码之间具有小的互相关。一旦获得精确位同步即开始对后续接收信号进行解调,在连续的解调序列中检测到“0 0 0 1”序列时即获得帧同步。帧同步检测原理如图7所示。 图7 帧同步检测原理 3.6.4载波同步 载波频偏差一般来源于发射机和接收机之间晶振的不匹配和无线移动信道多普勒效应2个方面[10-11]。载波同步包括相偏估计、频偏估计。对于载波相偏,相关函数I、Q两路的平方和运算可以消除固定相偏的影响,同时差分解调对固定相偏不敏感,故本系统只设计载波频偏估计算法。 匹配滤波器的输出相关函数具有如下特性: R(t+Ts)=ej2πΔfTsR(t)。 (13) 利用相关函数的周期重复性,采用基于双滑动窗口的方法进行频偏估计,原理如图8所示。 图8 频谱估计算法原理 对于双滑动窗口tA-tB=Ts,t时刻的相关值相位表示为: 2πΔf(t)Ts。 (14) 载波频偏估计结果: (15) 双滑动窗口相关值相位φ(t)的变化范围为[-π,π),所以这种频偏估计方法的频率估计范围: (16) 由于噪声的影响,式(16)计算得到的载波频偏估计值总是在频偏均值附近呈方差分布,为减少频偏估计抖动,可对一段时间内的频偏估计结果做统计平均,统计时间越长,估计精度越高,同样计算量也会增加。仿真结果显示,信噪比不小于-9 dB、8个PN码的统计平均结果就能较好地满足系统性能要求。 3.6.5AGC算法 AGC算法设计的关键指标是稳定性和响应速度[12],稳定性要求电压抖动小,不易受脉冲干扰影响,响应速度要求电路在尽量短的时间内将输入信号放大/衰减到正常范围,并能跟踪信号幅度的低频变化。若采用普通的反馈AGC算法,无法满足短时突发系统的响应速度要求,且容易产生“尖峰”和“凹陷”。本系统采用如下AGC方案:若未检测到信号时,设置固定增益;检测到信号到达时,则进入AGC起控流程,根据相关杉树幅度进行AGC控制,每一帧信号进行一次AGC控制,帧内信号的平稳性主要由信道分机保证。 相关函数幅度与输入信号幅度的平方成正比,假定在没有衰减的情况下全部用于到达检测的相关值幅度之和为y0,实际接收信号的相关值幅度之和为y,完成到达检测后,AGC模块根据下式的运算结果控制衰减器: (17) 式中,plusn为衰减器上一次衰减分贝值。 AGC算法实现原理框图如图9所示。 图9 AGC实现原理 基于前文设计对系统解调性能进行仿真分析,仿真结果如表1所示。其中,信息速率设为最大值200 kbps,多普勒频偏分别设为10 kHz、31 kHz,到达检测门限设定为8。 表1不同信噪比条件下的解调性能 信噪比/dB无频偏10kHz31kHz31kHz[无频偏纠正]无噪声0000.25-80000.25-90000.25-10000.00020.2507 理论推导及算法仿真均表明,本系统算法设计可支持低信噪比(-9 dB)、大动态多普勒频移(±31 kHz)条件下最高200 kbps信息传输速率。若采用预先纠正频偏和3路并行复用同步检测方法,可在不增加硬件资源占用的情况下进一步提升系统抗多普勒频移能力(最大±62 kHz)。 本文设计的相关峰同步检测算法与传统的序列监测和滑动相关检测算法相比,占用硬件资源相当,但帧利用效率和同步捕获时间都大大提升。如采用序列检测算法或滑动相关算法,仿真表明在-9 dB信噪比要求下,71个PN码长度才能具备较好的性能,而本文算法仅需16个PN码,且这2种算法因帧长过长,AGC和频偏还需额外增加跟踪校正处理。 码移键控扩频通信技术具有抗干扰能力强、隐蔽性、保密性和传输速率高等诸多优点,适合应用于高速无人飞行器视距测控通信,但突发工作方式下的高传输效率、快速同步以及硬件资源消耗矛盾是技术难题。本文详细描述了系统设计原理、各环节参数选择方法,给出一种利用匹配相关实现解扩解调、快速同步及AGC控制算法,并对算法进行优化, 满足利用较少同步头即实现快速同步的同时,大大减少了硬件资源占用。通过仿真分析,该算法具有良好的解调性能,满足系统应用需求。 系统已在AD+FPGA+DA全数字平台实现,并应用到某测控与信息传输系统中,试验测试表明这是一种可靠的高速扩频实现方案。 [1]周祥生.无人机测控与信息传输技术发展综述[J].无线电工程,2008,38(1):30-33. [2]张晶.无人机测控与信息传输信道的建模与仿真设计[J].电子技术应用,2012,38(2):98-104. [3]陈远友.无人机测控与通信系统信道传输特性研究[J].无线电工程,2014,44(3):15-17. [4]曹志刚,钱亚生.现代通信原理[M].北京:清华大学出版社,1999. [5]马永奎,张中兆,张乃通.带通采样定理在软件无线电中的应用研究[J].无线电工程,2002,32(10):17-19. [6]石代军.直接序列扩频突发信号同步算法[D].成都:电子科技大学,2007. [7]黄振,杨士中.匹配滤波器接扩方式及性能[J].重庆大学学报(自然科学版),2002,25(1):92-95. [8]谭晓衡,杨丽丽,张毛.改进的数字匹配滤波器的设计及FPGA实现[J].重庆大学学报,2010,33(4):109-114. [9]张斌,王华奎,李艳萍.直接扩频码捕获技术的研究[J].现代电子技术,2006(9):23-26. [10] 叶宇.基于低量化比特的数字通信系统技术方法研究[D].成都:电子科技大学,2015. [11] 贾龙龙.高速数据传输系统中载波同步技术研究[D].西安:西安电子科技大学,2012. [12] 华清.突发通信中的快速载波同步技术研究[D].西安:西安电子科技大学,2013.3.5 DBPSK解调

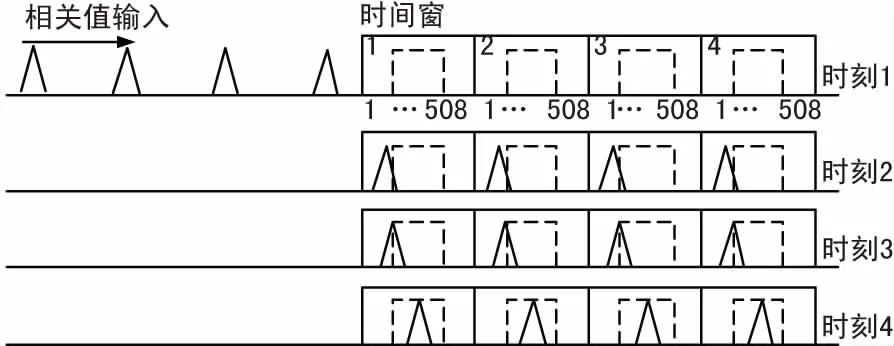

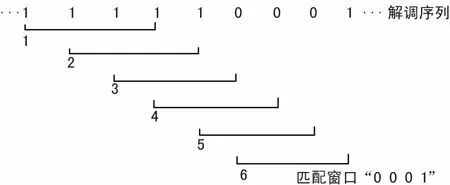

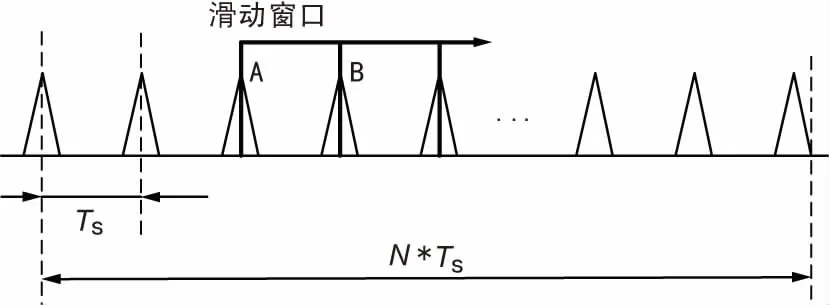

3.6 同步算法

4 仿真分析

5 结束语