声纳水下多通道数据采集模块设计

许 乔,殷志刚,周艳玲

(湖北大学 计算机与信息工程学院,武汉 430062)

0 引言

声纳技术是利用水下声波判断海洋中物体的位置,类型以及其他参量的方法和技术,是完成水下信息获取的有效途径[1]。数据采集主要是指将各种模拟非电参量如温度、位移、速度等经过调理和数字化后,再通过计算机进行后续处理的过程[2]。传统数据采集系统存在着采集通道少、采样速率低、转换精度低等问题,这无疑对应用环境提出了更高要求[3-4]。随着数字器件的飞速发展,采集系统的相关性能指标如计算速度和通信带宽都有了很大提高,使得数字采集系统得到广泛普遍应用。现代数字数据采集技术具有采集精度高、采集速度快、工作稳定性好,应用领域广,并可通过软件进行功能重构和应用升级等特点[5]。另一方面,互联网行业的飞速发展促使了底层设备网能够和局域网进行有效的连接,使得计算机能够对现场工作的数据采集设备进行实时控制和管理[6]。传统的通信方式大多采用RS-232或RS-485等通信接口总线,效率比较低且不利于信息共享。因此通信接口总线需要有标准化、快速化、抗电磁干扰等优良特点,而以太网总线恰好满足了应用需求[7-8]。工业以太网的出现使得信息能实现内部共享,而且还能够将监测数据上传,实现大范围的信息共享。同时以太网通信的高吞吐率和带宽能够实现海量数据通信[9-10]。

结合上述技术和应用背景,本文以BF537为控制核心,基于AD转换芯片ADS1278设计了一声纳水下多通道数据采集电路模块。该模块实现了8通道、采样率可达32KSPS、24位A/D的采集,通过以太网接口与上位机连接,用于对水下传感器模拟信号进行实时采集和同步打包传输。

1 系统分析

1.1 采集系统基本组成

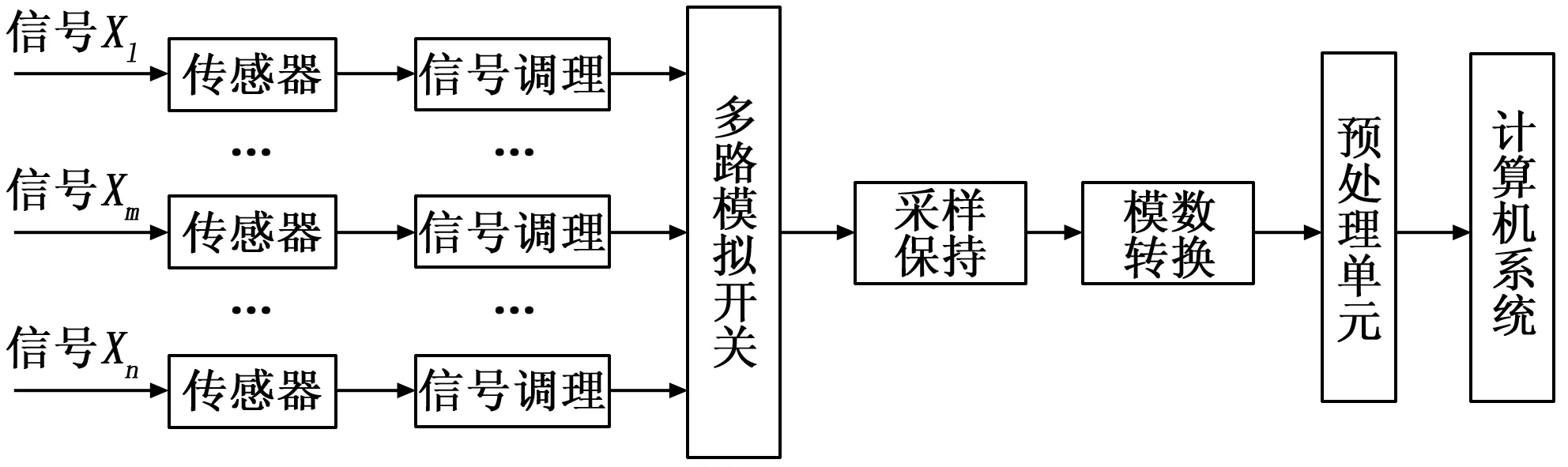

数据采集技术需将外界的各种模拟信号经过传感器转化为电信号,再进行信号调理与数字化,将数字信号传输到计算机中进行后续处理[11]。典型数据采集系统基本组成如图1所示。

图1 数据采集系统基本组成框图

各部分作用如下:

1)传感器:将被检测的非电物理参量转换成模拟电信号;

2)信号调理:主要对模拟电信号进行放大、滤波和隔离等操作;

3)多路模拟开关:选择信号进行采样;

4)采样保持:在AD转换过程中使信号的电平始终保持,保证经过A/D转换后的数字信号能正确反映出原信号信息;

5) A/D转换:模拟信号数字化,分辨率和采样速度等指标取决于A/D芯片选型和配置;

6)预处理单元:进行AD转换后的数字信号需转换为计算机能够识别和处理的信号,通常可使用DSP、FPGA等作为预处理芯片;

7)计算机系统:对整个采集系统起到控制作用,同时可进行数据处理和分析。

1.2 采集模块方案设计

本文设计的数据采集模块主要任务是对8通道的水声信号进行同步采集,转换为数字信号后进行打包传输。数据采集模块结构如图2所示。

图2 数据采集模块结构框图

数据采集模块由4部分组成,即模拟电路部分、A/D转换、数字电路部分和电源电路。信号调理将模拟电信号进行滤波和可控增益放大。AD转换芯片ADS1278对模拟信号进行特征量提取,可对芯片上的8路模拟端口信号同时进行采样,再将采样后的数据通过SPI接口传送至主控DSP芯片BF537,对数据进行打包传输。主控芯片同时能对上位机发送的请求命令进行确认回答,实现采集模块与上位机之间的通信。

该模块的主要设计参数见表1。

表1 设计参数

2 硬件设计

电路板设计是数据采集技术实现的硬件基础。电路板主要由可控增益放大电路、采集串口电路以及以太网通信接口电路等组成。

2.1 可控增益放大电路

本文中原始模拟信号的幅度值范围可划分为几个区间。可控增益放大电路的增益通过主控芯片进行控制,当输入模拟信号较大时,控制信号使增益变小,反之则增益变大。

该模块由芯片OP2177和ISL43841来实现可控增益放大。OP2177是低噪声、低输入偏置电流双通道运算放大器,具有极低失调电压和漂移、低输入偏置电流、低噪声及低功耗等特性。ISL43841是低压的、双向4选1的多路模拟开关,其输入电压为单电源电压2~12 V,或者是双电压±2~±6 V。可控增益放大电如图3。其中OP2177起到放大的作用,多路模拟开关ISL43841通过DSP控制实现不同的放大增益。NO为模拟开关,COM为通用模拟开关,输出电压与输入之间的关系如下。

OUT×R1/(R2+R1)

(1)

图3 可控增益放大电路图

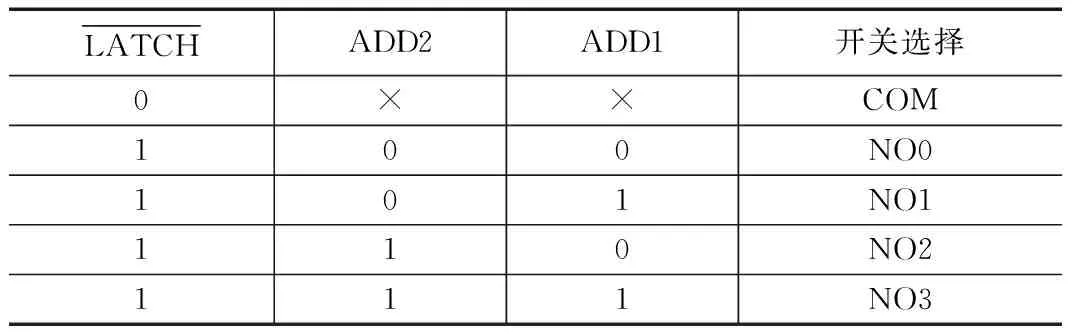

DSP通过控制(数字控制输入管脚)的逻辑电平,以及ADD(地址输入管脚)的逻辑电平来实现对应增益放大。逻辑增值表见表2。

表2 真值表

2.2 采集串口电路

模数转换芯片(ADC)将连续的模拟信号转换成数字信号。ADC芯片的性能好坏将直接影响到数据采集质量的好坏。ADC芯片选型主要考虑以下两点[12]:1)性能指标符合设计需求,如通道数、分辨率、采样速率、串并行、动态范围、输入带宽、功耗等;2)与主控制器接口连接方便,不需要其他复杂的逻辑电路来连接。其中采集通道数、采样速率和分辨率是ADC芯片选取的重要指标。

1)采集通道数。多通道能同时采集多路信号,节约成本。但是通道数量的增多会降低采集效率。现有的多通道同步采集技术,每增加一个通道,就要增加一个采样保持,所以设计上需要合理考虑芯片采样通道数。

2)采样速率。系统在单位时间内对模拟信号的采样次数称为采样速率。采样速率越高,则转换后的数字信号越能包含原信号的信息。

3)分辨率。信号经过模数转换后,直接输出一个二进制数码,码的固定位数表示这个A/D转换的分辨率。位数越长,量化步长越小,产生的误差也就越小。

ADS1278是八路同步采样24位模数转换器,采用三角积分高精度采样,采样速率可达128KSPS,带宽62KHz, 偏移漂移和增益漂移基本为0,性能稳定。同时,它的4个运行模式(高速率、高分辨率、低功耗、低分辨率)可实现速度、分辨率和功率的优化。所有操作直接由引脚控制,无需寄存器编程。综上所述,ADS1278芯片符合设计需求。

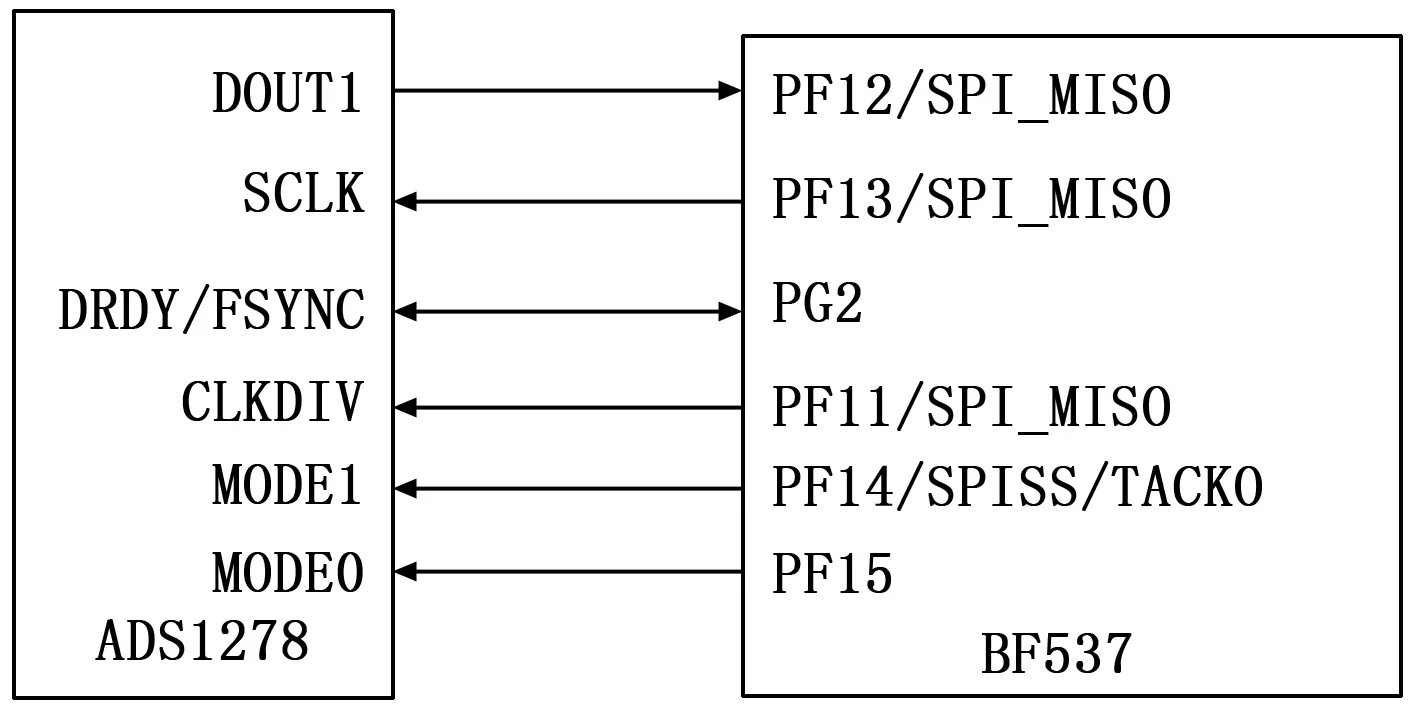

BF537主控芯片与ADS1278之间通过SPI接口进行数据通信,SPI是一个4线全双工同步串行接口,支持主机模式、从机模式和从主机环境。串行接口SPI有4个引脚,MOSI(主出从入),MISO(主入从出),SCK(门控时钟引脚)和SPISS(片选引脚)。SPI数据可以通过移位寄存器同时发送和接收,SCK用于把MISO和MOSI线上的驱动数据移入和移出,在时钟有效沿数据移出,无效沿数据采样。采集串口电路示意如图4。由于ADS1278芯片配置为SPITDMDynamic(串行时分复用)方式输出,因此DOUT1和SCLK分别为TDM数据输出和串行时钟输入。MODE[1:0]为运行模式选择配置引脚,可选择高速率、低速率、高分辨率、低功耗模式。在此选择低功耗模式。

图4 采集串口电路图

2.3 以太网通信接口电路

以太网遵循IEEE802.3标准,IEEE802.3 描述了物理层和数据链路层的MAC子层的实现方法。物理层的主要功能是比特流的传输和接收。数据链路层的MAC子层的主要功能是将上层交下来的数据封装成帧进行发送,接收时对帧进行拆卸,然后将数据交给上层,并实现和维护MAC协议。

数据链路层和物理层之间是通过IEEE802.3定义的MII(介质独立接口)接口连接MAC和PHY(物理接口收发器)。MII接口传递了网络的所有数据和数据的控制,它包括一个数据接口,以及一个MAC和PHY之间的管理接口。数据接口包括用于发送器和接收器的两条独立信道,每条信道都有自己的时钟、数据和控制信号。管理接口是个双信号接口:一个是时钟信号,另一个是数据双信号线接口。通过管理接口,上层能监视和控制PHY。

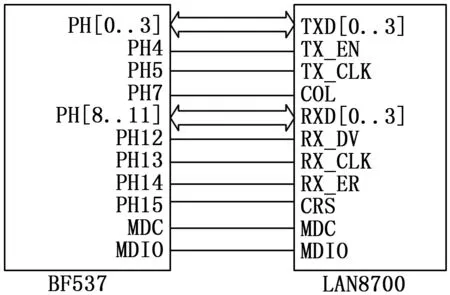

以太网接口电路设计中,使用了LAN8700芯片,这款PHY以太网控制器是单端物理层芯片。芯片BF537集成了数据链路层中MAC子层的功能。在电路设计中,参照MII规范,在10/100Mb/s系统中,将LAN8700的物理层与媒体接入控制(MAC)层进行连接。以太网通信接口电路如图5所示。

图5 以太网接口通信电路图

MII接口中发送和接收时钟是分开的。TX_EN是MII发送使能引脚,TXD[0:3]是MII发送数据引脚,RXD[0:3]是MII接收数据引脚。LAN8700 提供一个RX_DV信号(接收数据有效),使得恢复接收数据的方法简单而无需从CRS_DV(校验)中分离出RX_DV信号。接收数据RXD[3:0]转换与RX_CLK(接收时钟)同步。在确认CRS_DV的每个时钟周期内,RXD[3:0]转换来自LAN8700的4位回复数据。在数据恢复或者错误情况发生时期,转换的是RXD[3:0]的预确定值而非恢复数据。在CRS_DV解除确认时,RXD[3:0]为“0000”,表示是空闲状态。一旦CRS_DV确认,LAN8700确保RXD[3:0]为“0000”,直到产生正确的接收解码。

在接收数据RX_CLK期间内,确认RX_ER(接收错误)使其标识。发送使能(TX_EN)指示MAC在TXD[3:0]上呈现4位以用于传送信号。TX_EN应被前导符的首个半字节同步确认,而且在所有的被传送的4位信号呈现时都应保持确认。在跟随着帧的最后两位的第一个TX_CLK上升沿之前,MAC应该确认。TX_EN转换相对于TX_CLK(发送时钟)是同步的。

COL为冲突检测,MDC和MDIO为PHY管理接口。

3 软件设计和功能测试

采集模块软件设计是数据采集技术实现的重要组成部分,在硬件电路完成的基础上,通过软件编写相关程序实现系统所需功能。软件程序设计主要包括两部分,一是数据采集处理程序,另一是以太网通信程序。而性能测试结果是能保证系统稳定可靠运行,并且能实际投入到工业应用的关键因素。本模块使用信号发生器做测试信号源,将采集的数据传输至计算机中,通过MATLAB计算仿真验证结果是否达到相应标准。

3.1 基于BF537的数据采集处理程序设计

基于BF537的数据采集处理程序通过VisualDSP+平台实现,将程序下载到主控芯片BF537中,通过SPI(串行外设接口)去控制AD芯片ADS1278,使其按需进行采样,将8通道数据通过SPI接口传输给DSP芯片进行处理。

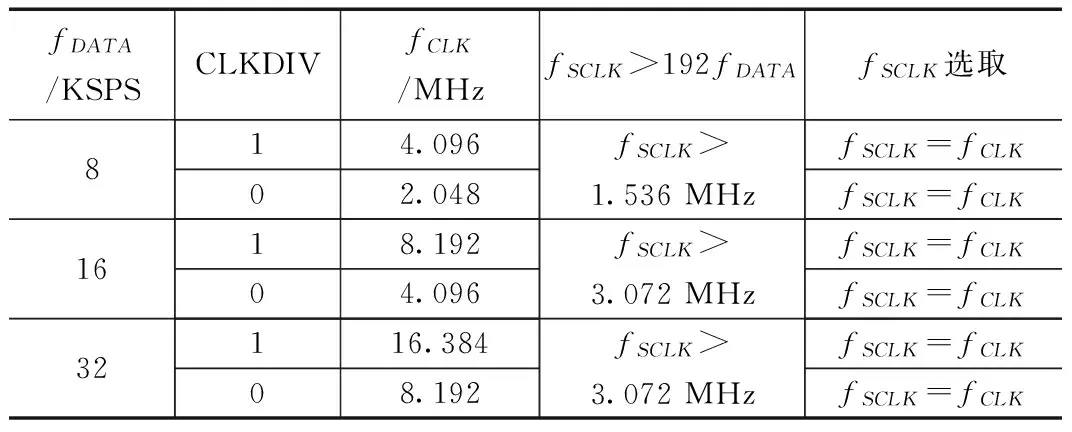

其中设置引脚MODE[1:0]为10低功耗模式。CLKDIV为主时钟输入分频控制引脚, 通过CLKDIV控制引脚后,fCLK=k×f。其中为主时钟频率,f为采样速率。时钟输入选择见表3。

表3 时钟输入选择

AD芯片每通道有24个SCLK(串行时钟),1个SCLK对应1bit。

8通道采集一次需要24bit*8=192SLCK,则串行时钟频率应该大于192个数据采样频率,即fSCLK>192fDATA,TDATA>192/TSCLK,其中fSCLK为串行时钟频率,TSCLK为串行时钟周期,TDATA为采样周期。通常情况下fSCLK=fCLK/2^n,其中n为自然数。当采样频率fDATA不同时,串行时钟频率fSCLK选择见表4。由于芯片模式为低功耗模式,所以采样速率要小于52.734KSPS。

表4 fDATA-fSCLK频率大小选择

主控芯片BF537对ADC的基本设置为:

设置PG9=0,ADS1278_ClkDiv;

CPHA=0,CPOL=0,SIZE=8 :SCK(SPI时钟频率)高电平有效,传输格式从第一个数据位的终点处SCK切换。持续接收,覆盖原数据;

TIMOD[1:0]=00:读SPI_RDBR(SPI接收数据缓冲寄存器)开始传输,当SPI_RDBR满时产生中断。

3.2 基于BF537的以太网通信程序

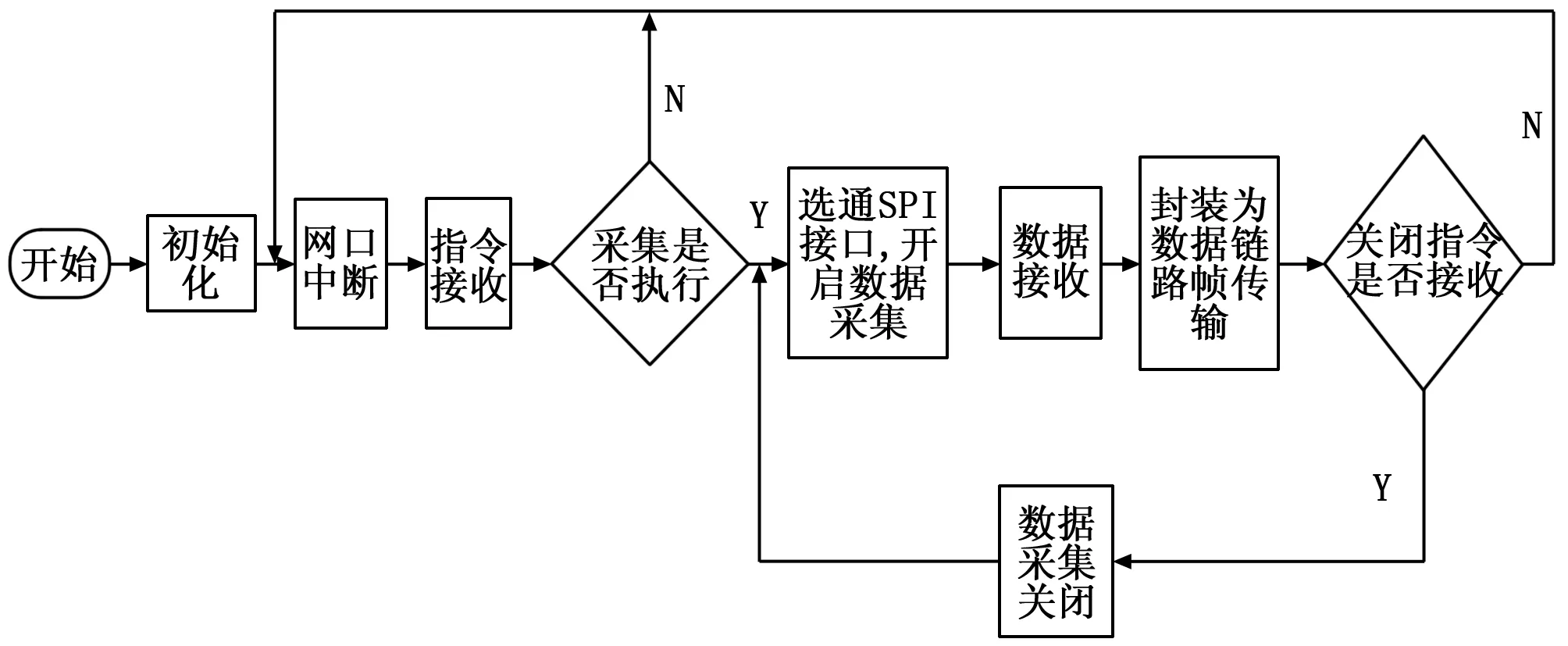

数据采集模块主控程序和以太网接口通信主要是在芯片BF537上完成。其开发环境是仍然采用VisualDSP+开发套件。主控程序流程如图6所示。

图6 主控程序流程图

主控芯片BF537在经过系统初始化后,进入以太网接口通信模式,等待计算机发来指令,系统产生网口中断。判断指令是否为数据采集开启指令,如果是,则开始采集数据。选通 SPI 接口接收数据,将数据以以太网标准数据包格式上传至计算机。

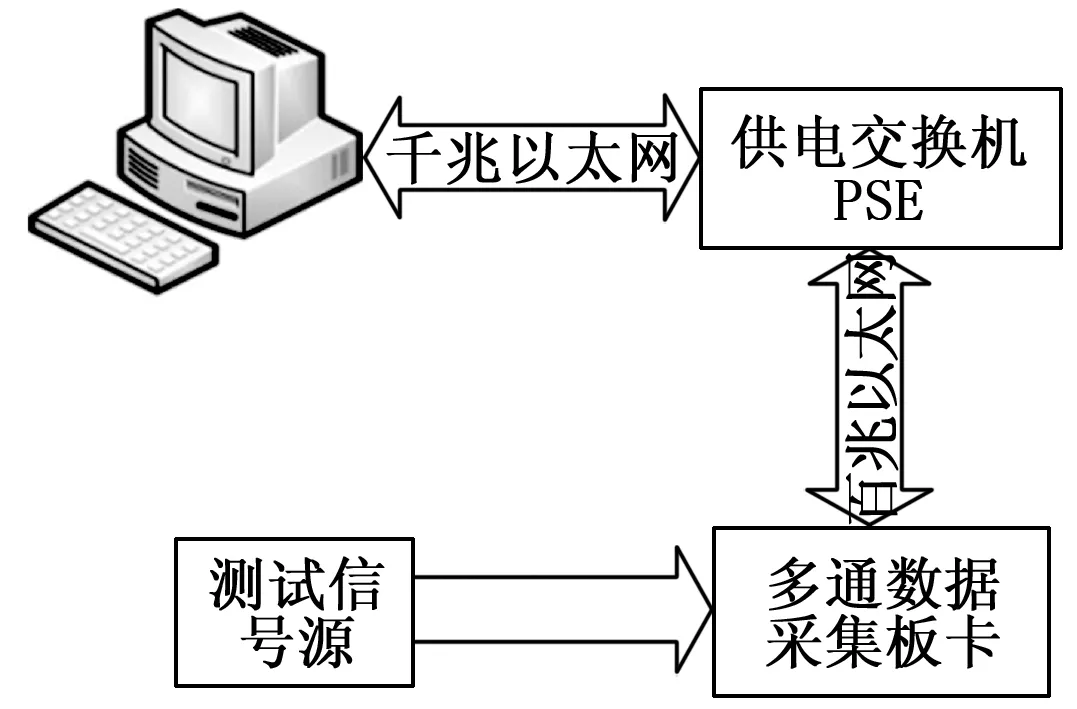

3.3 功能测试

信号源产生测试信号,连接到采集模块输入端口,模拟实际信号输入。同时将以太网交换机和采集模块连接,起到对数据采集模块供电和中继转发的作用。采集模块测试如图7所示。

图7 测试平台

测试的性能指标为通道串扰和动态范围、谐波失真、相位一致性误差和幅度一致性误差等。测试流程为:

1)烧写Flash。通用计算机通过VisualDSP++软件写入。将ADI DSP仿真器系列EBF-EMU-II下载电缆插入DSP的JTAG接口,在查看寄存器处数据内容是否改变为正确。

2)烧写CPLD PROM。

3)访问硬件调试

主要包含检测是否找到硬件设备,检测设备是否能进行配置,检测设备是否能进行自检和采集,检测设备是否能停止。

4)记录数据。通过MATLAB源代码程序处理AD采集后的数据。查看测试结果是否符合性能指标规范。

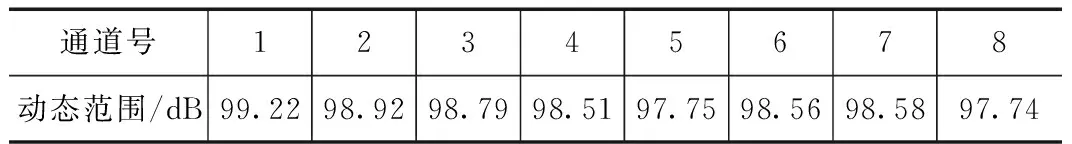

3.3.1 动态范围

当采集模块所有8通道的模拟输入短路接地时,动态范围测试结果见表5,从表中可以看出,采集模块各通道动态范围满足≥90 dB的设计指标要求。

表5 动态范围

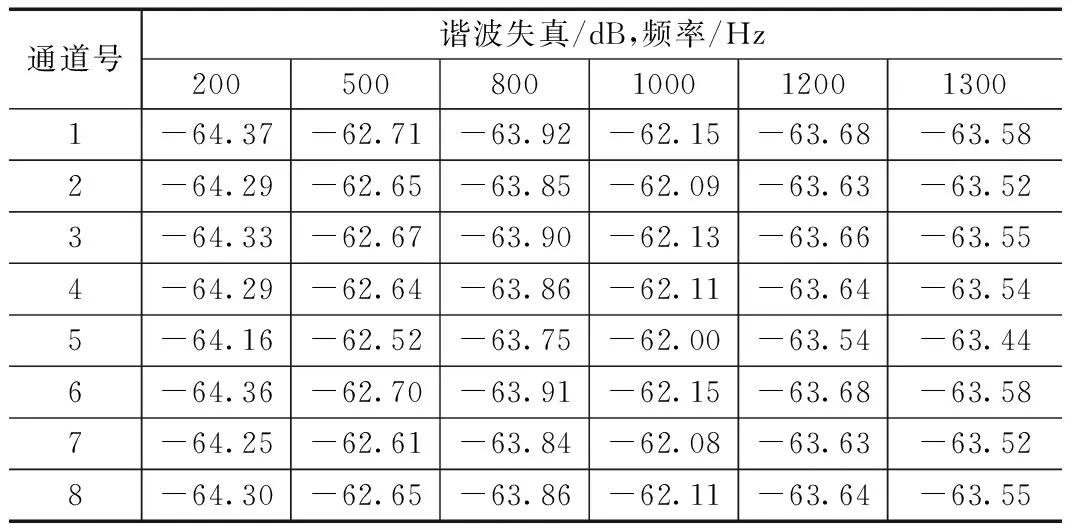

3.3.2 谐波失真

当采集模块8通道模拟输入VPP=2 V,谐波失真测试结果见表6。结果表明采集模块谐波失真满足≤-60 dB设计指标要求。

表6 谐波失真

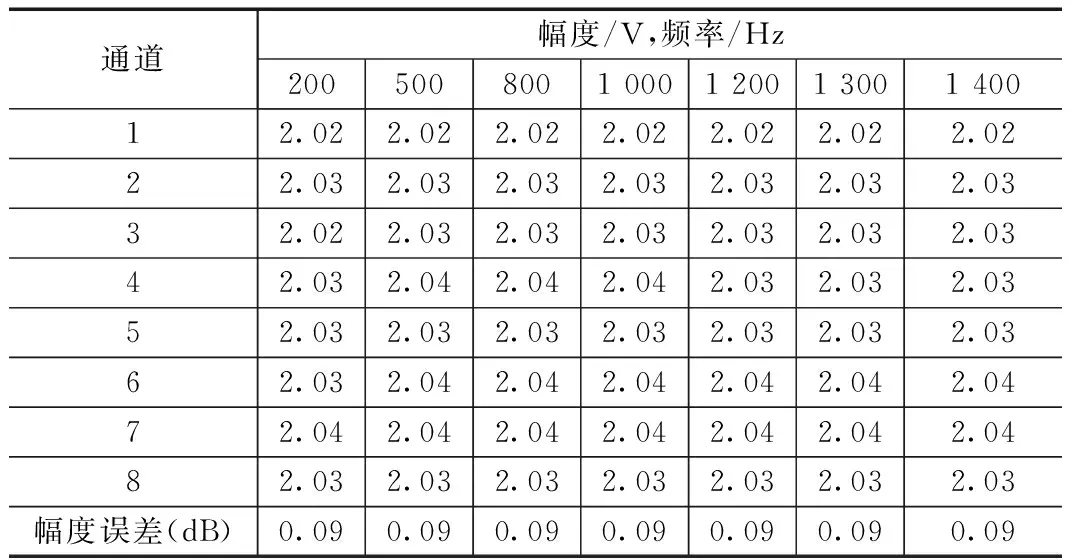

3.3.3 幅度一致性

当采集模块8通道模拟输入,幅度一致性测试结果见表7。

结果表明输入信号通过采集模块后,各通道输出信号幅度基本保持一致,符合设计要求。

表7 幅度一致性

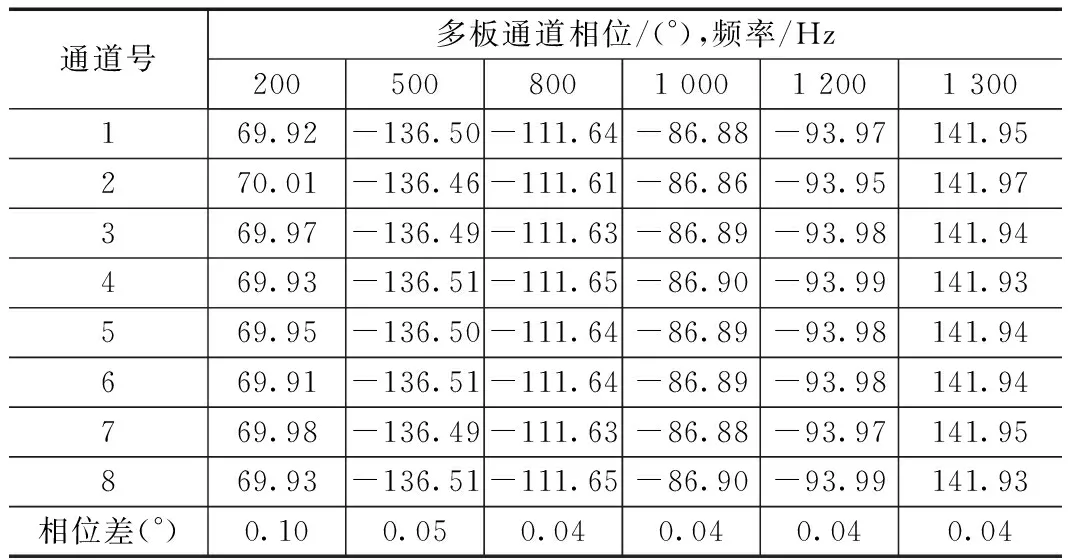

3.3.4 相位一致性

当采集模块8通道模拟输入,相位一致性测试结果见表8。测试结果表明各通道延时基本保持同步,相位基本无偏差,符合设计要求。

表8 相位一致性

以上结果表明多通道数据采集模块性能满足设计需求。

4 结语

多通道数据采集模块主要对数据进行实时采集和同步打包传输。该电路模块配置了DSP芯片BF537,使得用户可自行配置I/O口,配置灵活,易于扩展;模块使用一块百兆以太网PHY芯片LAN8700i,可以实现较大数据量通信;模块使用ADS1278作为A/D转换芯片,集成有8路通道,转换精度为24位,每通道最大采样率为32 ksps,可利用同步时钟接口实现多板多路信号同步采集;该模块应用方便,可通过软件调整相应参数实现放大倍数、采样率的调整。测试结果表明该模块性能优异,符合一般工业应用需求,能广泛应用于声纳、语音等微弱信号探测前端硬件技术领域。

[1]田 坦,刘国枝,孙大军.声纳技术[M].哈尔滨:哈尔滨工程大学出版社,2000.

[2]王华刚,邓志燕,董鹏飞.多功能多通道数据采集系统设计与实现[J].自动化与仪器仪表,2016(9):36-37.

[3]刘立军. 基于FPGA多通道数据采集系统的设计[J].仪器仪表用户,2017(6):31-34.

[4]马晓蓉,吴银川.一种多通道数据采集系统设计研究[J].电子工程设计,2012,20(19): 14-16.

[5] Siew W H, Wang Y, Faheem M. Wireless digital data acquisition system for EMI measurement in power substions[J]. IEEE Trans Inform Theary,2006,17(4):288-291.

[6]Besaw L E, Rizzo D M, Bierman P R. Advances in ungauged stream flow prediction using artificial neural networks[J]. Journal of Hydrology,2010,386(14):67-71.

[7]黄安贻,叶 菁.基于交换式技术的工业以太网实时性问题的研究[J].机电工程技术,2005,34(4):13-16.

[8]高吉星,赵 强,佟为明. 基于ENC28J60的TMS320F2812以太网通信接口设计[J]. 计算机测量与控制,2013,20(3):709-711.

[9]邓 伟,王文菊. 基于TMS320 C6455的以太网通信程序的设计[J]. 电子设计工程,2013(7):165-168.

[10]吴 升,潘宏侠,高 阳.基于TMS320F2812的以太网通信系统的设计[J].机械设计与制造, 2011(3):203-205.

[11]肖忠祥.数据采集原理[M].西安:西北工业大学出版社,2001.

[12]高忠斌.模块化接收机与多通道数据采集电路设计[D].哈尔滨:哈尔滨工程大学,2010.