一种新型栅压自举开关的设计

卞腾飞,莫冰,高城,高磊,傅文渊

(华侨大学信息科学与工程学院,厦门 361021)

0 引言

随着CMOS工艺的不断迅速发展,工艺尺寸也在不断地降低,电源电压也按一定比例降低,因此对模数转换器(ADC)要求也越来越苛刻。由于在现有的ADC架构中逐次逼近模数转换器(SAR ADC)中等精度、低功耗等特点,适应于低压小尺寸CMOS工艺,广泛应用于传感器网络、微处理器中。SAR ADC的主要结构包括:采样保持电路、比较器、DAC、逻辑控制模块等。高性能采样保持电路是ADC重要组成部分,其动态性能直接影响SAR ADC的性能。为了提高ADC的线性度。在栅压自举开关工作过程中部分节点电压会高于供电电压,以达到一个合理的等效电阻。本文设计了一种新型栅压自举开关电路,并实现over-rail输入。

1 采样保持电路[1-2]

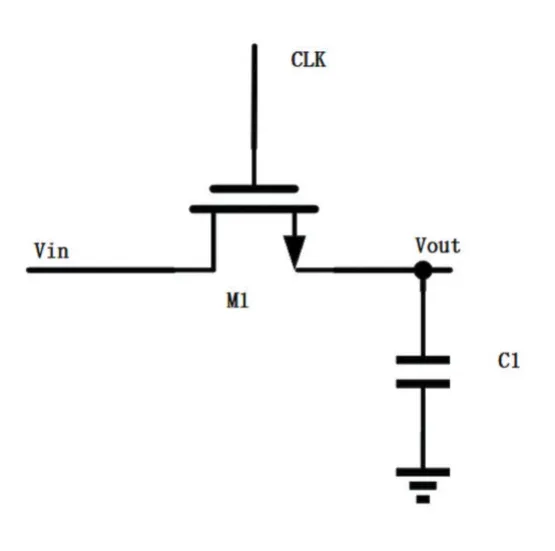

一个MOS管在大信号工作的情况下,利用其导通和截止特性可以简单的构成一个开关。用一个MOS开关和一个电容串联就可以简单的构成一个采样电路。图1为基本采样开关示意图,它的栅极由CLK控制,CLK为高电平时,采样开关进入开启阶段,VOUT开始跟随VIN信号,CLK为低电平,采样开关关闭,NMOS截至,Vout将保持在CLK由高转低时跟随的Vin,从而完成了一次采样过程,并保持了电压。所谓采样保持也就是说在一个时钟周期内输入信号通过开关对负载电容进行充电和保持,使电容上的电压值在开关断开前和输入值近似相等,并在开关断开后保持电压不变[3]。可以分为三种情况理解上述采样过程。

图1 基本采样保持电路

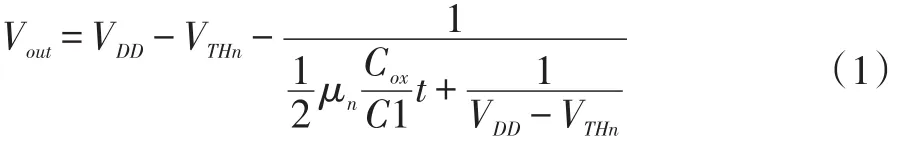

输入信号为高电平,采样电容初始电压为零条件下的采样电路相应,假设开关NMOS管M1栅端的时钟信号在t0时刻由低电平转为高电平,从而将M1管导通,闭合了开关。因为Vin端的电压高,因此电流从Vin端流向Vout端。对于NMOS管M1来说,在电流的方向下,和电容C1相连的一端是NMOS管的源端。因为M1管的栅端和漏端都有相同的电位,因此M1管一直工作在饱和区。根据电容两端电压和充放电电流的关系,可得:

从式1中可以看出,当t→∞时,由于当Vout接近VDD-VTHn时,M1管的过驱动电压接近零,使得电容C1的充电电流可以忽略不计,故在一般采样情况下VOUT→VDD-VTHn。在输入电压终值小于VDD-VTHn情况下,M1管一直工作在线性区,根据上述分析,电容C1将被充电,并且使得输出Vout接近Vin。当Vout接近Vin时M1管等效为电阻。其阻值为

根据式(2)可以得到采样电压稳定时,NMOS的导通电阻,由公式(2)可以看出导通电阻与输入电压之间成正相关,当输入接近VDD-VTHn时,NMOS管的导通电阻迅速增大,从而增大了采样电路的时间常数(Ron*C),进而降低了电路响应速度。在ADC应用中直接降低了采样速率,影响精度。

由于采样保持电路是决定ADC性能的关键电路,为了保证其具有较高的线性度,通常采用CMOS互补开关和栅压自举开关[4-5]改善等效电阻,使其不随输入信号的变化而变化。本文就是为了改善Ron的线性度,设计了一款改进型栅压自举采样开关电路。

2 新型栅压自举采样开关电路

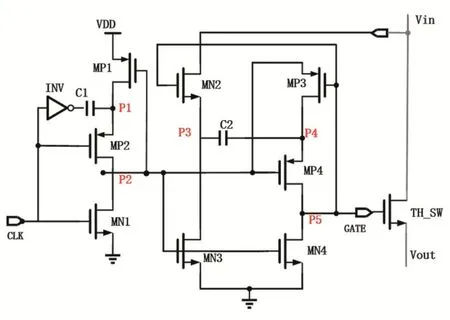

在深亚微米工艺条件下,关键的采样开关一般采用栅电压自举结构来降低开关导通电阻及其电阻的非线性变化[6-7],为了满足低压SAR ADC电路设计的需求,并保证输入信号的过摆幅输入,采样开关仍然可以保持较高的线性度,使等效电阻不受输入信号的影响,本文设计了一种新型栅压自举采样开关,并应用于10位SAR ADC中。

传统的栅压自举采样开关电路[8],做到了使自举的栅压远远大于供电电压,实现了较小的等效电阻,有的采样开关内部部分节点的电压可以达到2倍的VDD,在输入信号小于2倍VDD时,采样开关的等效电阻具有很好的线性度,但没有解决当输入信号大于2倍VDD时,可能出现漏电情况从而导致采样开关栅压采样期间不能跟随输入信号,降低线性度。

本文所设计的栅压自举采样开关电路如图3所示,其中CLK高电平为VDD,低电平为gnd。MP1,MP2,MN1,C1,INV构成了boost电路,其工作原理可分为两步:首先,CLK高电平使MN1开启和MP2截止,同时也反相器输出低电平,由于MN1开启从而使P2点低至低电平,MP1随着P2的拉低而完全导通,P1点被逐渐充电至VDD;然后,CLK变为低电平使MN1关断,MP2开启,反相器输出高电平,根据电容两端电压不能突变的特性,以及电容P1端没有放电回路,P1被boost到2*VDD并维持到下一个CLK高电平到来,由于MP2的开启P2的电压与P1电压相同并维持到下一个CLK高电平到来。

图 2中,MN2,MN3,MN4,MP3,MP4,C2 构成了Bootstrap电路,根据上文分析的结果可以得出如下结论:CLK=VDD,P1=VDD,P2=0;CLK=0,P1=2*VDD,P2=2*VDD,从而的到P2与CLK反相并被升压到2*VDD。Bootstrap的工作过程也可分为两步:首先,CLK=0,P2=2*VDD,MN3和 MN4开启,MP4工作在截止区;由于MN3和MN4相应的P3和P4被拉gnd,从而MN2工作在截止区,MP3工作在深度线性区,P4点电压逐渐被P2点充电至2*VDD;然后,CLK=VDD,P2=0,MN3和MN4将工作在截止区,MP4开启P5=P4=2*VDD,从而使MP3工作在截止区,由于P5电压的升高,同时MN2也被开启,P3点电压被垃止Vin,根据电容的电荷守恒定律,在没有放电回路情况下电容两端电压不能突变,因此,P5=P4=2*VDD+Vin,由于这个过程是正反馈,MN2栅端电压也始终比Vin大2*VDD;最终,栅压 GATE(GATE=P5)被自举至(2*VDD+Vin)。

根据上述结果可以得到栅压自举开关的等效电阻:

由上式可知Ron的阻值与输入信号Vin无关,具有较高的线性度,由于正反馈的存在可以输入信号实现过摆幅输入,增大了采样信号的输入范围。

图2 栅压自举开关电路

3 电路设计及仿真结果

设计的栅压自举开关电路使用SMIC(中芯国际)单层多晶硅5层金属(1P5M)55nm CMOS工艺库,电源电压设为VDD=0.6V,CLK的高电平也为0.6V。利用Ca⁃dence spectre软件对电路进行了瞬态仿真,图3为根据原理图2设计的电路瞬态仿真结果。根据图3取出的两组点可以算出平均GATE-Vin=1.178V很接近2*VDD。

4 结语

本文在SMIC工艺下设计了用于SAR ADC的采样保持电路开关,基于文献[8]的结构改进了栅压自举开关电路,允许采样保持电路的输入信号过摆幅输入。这种栅压自举电路可以应用各种ADC采样保持电路中,可以保证采样开关工作在深度线性区,提高等效电阻的线性度。

图3 栅压自举开关的仿真波形

[1]Ravavi B.模拟CMOS集成电路设计.西安交通大学出版社,2003.

[2]Allen P E.CMOS模拟集成电路设计.第2版.北京:电子工业出版社,2005.

[3]何乐年模拟集成电路设计与仿真[M].北京:科学出版社,2008-8.

[4]Hong H C,Lee G M.A 65-fJ/Conversion-Step 0.9-V 200-kS/s Rail-to-Rail 8-bit Successive Approximation ADC[J].IEEE Journal of Solid-State Circuits,2007,42(10):2161-2168.

[5]Huang G Y,Liu C C,Lin Y Z,et al.A 10-bit 12-MS/s Successive Approximation ADC with 1.2-pF Input Capacitance[C].Solid-State Circuits Conference,2009.A-SSCC 2009.IEEE Asian.IEEE,2009:157-160.

[6]Sumanen L,Waltari M,Halonen K A I.A 10-bit 200-MS/s CMOS Parallel Pipeline A/D Converter[J].Solid-State Circuits,IEEE Jour⁃nal of,2000,36(7):1048-1055.

[7]Li J,Zeng X,Xie L,et al.A 1.8-V 22-mW 10-bit 30-MS/s Pipelined CMOS ADC for Low-Power Subsampling Applications[J].IEEE Journal of Solid-State Circuits,2008,43(2):321-329.

[8]Rabuske T,Fernandes J.A SAR ADC With a MOSCAP-DAC[J].IEEE Journal of Solid-State Circuits,2016,51(6):1410-1422.