利用AD7616的V型采样实现准同步数据采集

于克泳+叶健

摘要:AD7616是ADI公司推出的一款16位数据采集系统(DAS)。对于多通道非同步采样型ADC,本文采用“V型采样十数据平均”的模式在AD7616的应用中实现了准同步采样,同时基于AD76、6的实验结果也验证了理论上的误差分析。

关键词:AD7616 V型采样准 同步采样

DOI: 10.3969/j.issn.1005-5517.2017.9.018

1 AD7616简介

AD7616是ADI公司推出的一款16位16通道数据采集系统(DAS),同一封装内集成了两个16位逐次逼近寄存器型(SAR)模数转换器(ADC),支持对16个通道进行双路同步采样。AD7616的模拟输入端为真双极性输入,每个通道的量程可独立设置,有±10 V、±5V或±2.5 V供选择,同时输入端具有±20V的箝位(CLAMP)保护,而且片内集成有抗混叠模拟滤波器。AD7616采用+5 V单电源供电,拥有lMsps的采样速率并达到90dB的信噪比(SNR),输入阻抗与采样速率无关,恒定为1MΩ,因此无需外部的驱动电路及双极性电源。

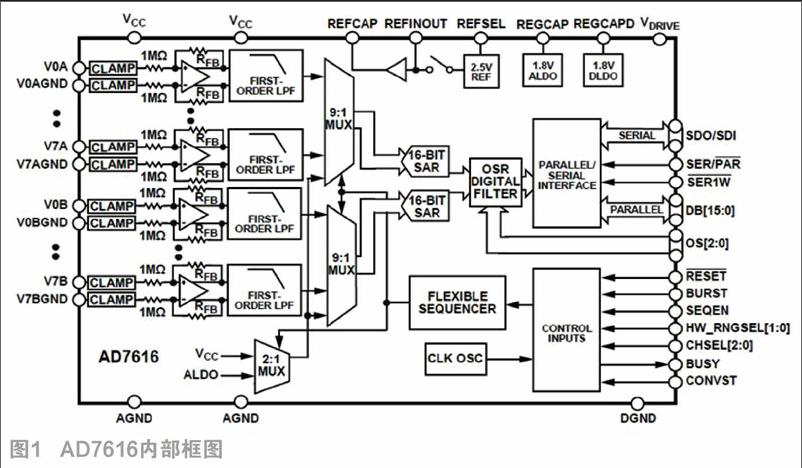

AD7616通过HW_RNGSEL[1:0]管脚进行选择,工作在硬件模式或软件模式。硬件模式下,AD7616由引脚进行配置。软件模式下,AD7616支持并口或串口对内部的寄存器及灵活的序列器(Flexible Sequencer)进行配置,以获得更多的功能。AD7616的内部框图如图1所示。

2 多通道准同步采样

电力系统保护与测控的应用中,需要实时监测电网中多相的电压和电流信号。为了满足各种标准的精度要求,传统的设计中通常都是对多路信号进行同步采样,因此一般选用多通道同步采样型的ADC,例如AD7865,AD7656-1,AD7606等都是典型的应用选择。

在某些需要低成本但精度要求不高的应用中,工程师尝试采用一种“MUX模拟开关+单通道ADC”的设计方案,如图2所示,利用模拟开关切换输入通道,用单通道ADC循环对输入信号进行采样。由于多通道信号的非同步采样,采样点的间隔时间会导致通道间采样的延迟,并由此带来一定的相位误差或相位失配,误差的大小与多个因素相关,取决于输入

信号的频率、幅值、采样时刻信号的相位等。

为了减少非同步采样所带来的通道间相位误差, 设计一种采样序列, 通道顺序为 “VINO→VIN1→VlN 2→…>VIN6>VIN7>VIN6>…>VIN2>VIN1>VINO”,如图3所示。由于采样序列像一个大写的字母“V”,我们不妨称之为“V型采样”模式。

在图3“V型采样”配置下,VINO - VIN6的每个通道前后采样两次,而且采样时刻在VIN7采样时刻的两侧呈对称分布。如果ADC的采样间隔控制为等间距,当输入信号为线性信号时,VINO - VIN6通道前后两次采样数据的平均值与在VIN7采样时刻的结果是相同的,这就通过“V型采样+数据平均”的方式实现了多通道间的准同步采样,因此把VIN7的采样时间点称之为“准同步采样时刻”,如图4所示。

如果输入信号为正弦波,采用“V型采样+数据平均”的模式会带来一定的误差,但相比传统的“MUX模拟开关+单通道ADC”非同步采样模式而言,仍然可以大幅减少由于非同步采样而带来的通道间误差。

3 “V型采样+数据平均”的误差分析

以正弦波为例,分析“V型采样+数据平均”模式得到的平均值与准同步采样时刻的采样值之间误差的大小。为了简化分析,将输入正弦波信号的幅值归一化为1.0,并假定第一个采样点时刻对应正弦波的相位为α,β,第二个采样点时刻对应正弦波的相位为α+2 β,系统应用为例,用Tspan=14μs来计算“V型采样+数据平均”所带来误差的最大值:

对于50Hz(基波),误差最大值为:1 - COS(π*50Hz* 14μs)<0.01‰;

对于250Hz(5次谐波),误差最大值为:1-COS(π*250Hz*14μs)<0.1%:

对于2550 kHz(51次谐波),误差最大值为:1-COS(π*2550Hz*14μs)<6.3‰;

从以上的计算结果来看, “V型采样+数据平均”的模式完全可以满足电力系统中保护和测控的精度要求。下一步将会用实验的方法进行验证。

4 AD7616准同步采样的实现

在传统的“MUX模拟开关+单通道ADC”模式中,ADC每收到一个CONVST启动转换控制信号后,仅完成一个通道的转换。这就意味着,要通过“V型采样+数据平均”的方式来实现“准同步采样”,需要处理器(Processor)发出一系列的CONVST启动转换控制信号来实现多个通道的采样序列,还要求处理器在每次启动转换之前读出ADC的转换数据,这既增加了处理器的负担,又降低了系统的可靠性。

AD7616内部集成了MUX模拟开关和SAR型ADC,特别之处在于还集成有突发模式(Burst Mode)和灵活的通道序列器(Flexible Sequencer)。当AD7616工作在软件模式(Software Mode)下,通过设置序列栈寄存器(Sequencer stack registers),处理器只需要发出一个CONVST启动转换控制信号,AD7616将会自行完成所有设置通道的转换,并把每一次的转换结果放在数据缓存区中,待全部通道转换完成后,AD7616将BUSY忙碌指示信号置低,等待处理器读取所有通道的转换结果。AD7616与处理器的连接及内部通道序列器的示意图如图6所示。

AD7616内部有两个高速ADC核,称为A核和B核。通道的序列栈寄存器地址为Ox20到Ox3F,总共包含32个寄存器,由用户编程来实现1到32个预定的采样序列。每个寄存器的宽度为16bit,其中[7:4] bit定义为BSEL,用来设定B核的转换通道 [3:0] bit定义为ASEL,用来设定A核的转换通道。寄存器中的[8] bit定義为SSREN,是通道转换序列的结束控制位,如果设定为0,AD7616将调入下一个序列寄存器的设置进行转换,如果设定为1,通道转换序列在完成本次转换后结束。转换通道的选择,除了模拟输入通道VINO -VIN7,还可以选择内部Vcc,内部LDO,或者固定输出一个标志字Ox5555或OxAAAA。AD7616序列栈寄存器的描述如图7所示。endprint

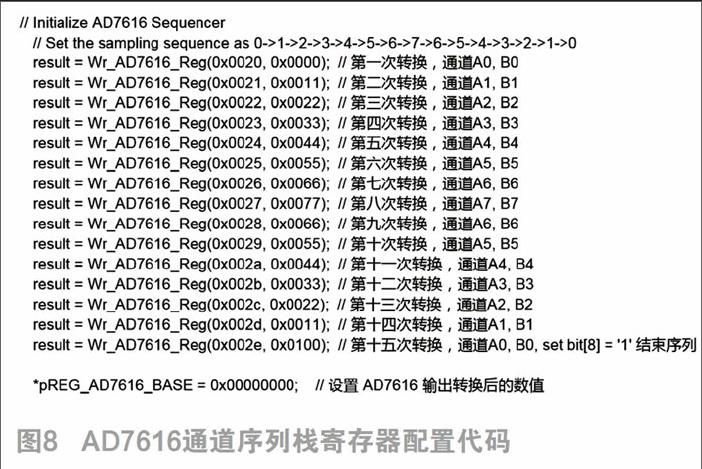

在應用中,处理器上电后,需要对AD7616内部的通道序列栈寄存器进行初始化。初始化完成后,需要把AD7616寻址寄存器的REGADDR[4:0]设置为00000,使得AD7616的状态为输出ADC转换数值。假定按照图3的模式进行设置,即采样通道顺序为“VINO→VIN1→VIN2→…→VIN6→VIN7→VIN6→…→VIN2→VIN1→VINO”。处理器与AD7616并口连接的情况下,序列栈寄存器的配置代码参考图8所示。在这样的配置下,VINO-VIN6通道都分别被采样了两次,数据平均由处理器来计算,这样准同步采样时刻正好对应于VIN7通道采样点在时间轴的位置。

应用中特别需要注意的是:软件模式下,完成AD7616所有寄存器的配置后,由于需要一个CONVST启动转换来使得所有寄存器配置都有效,因此AD7616第一次转换的输出结果是不可靠的,应用中需要把第一次的转换数据丢弃,数据手册中也把这第一次的转换称为“伪转换” (Dummy Convert)。另外,为了实现一次CONVST完成序列栈寄存器中全部通道的转换,在AD7616配置寄存器(Ox02 - Configuration Register)中的SEQEN、BURSTEN位(bit5,bit6)者l必须使台旨。AD7616的工作流程图参考图9所示。

5 测试验证

配合理论分析,同时搭建了AD7616的测试系统,如图10所示。验证系统中,信号源为Audio Precision2712,输出高SNR(信噪比)、低THD(总谐波失真)的正弦波供AD7616进行测试。处理器采用Cortex-M4内核的混合信号控制处理器ADSP-CM408F,AD7616采集的数据通过串口(UART)发送给PC电脑,使用VisualAnalog rM软件分析AD7616数据获得交流性能指标(SNR和THD),使用Microsoft Excel@运行DFT算法获得幅值和相位信息。

测试中,AD7616的采样序列按照图4的“V型采样+数据平均”模式进行设置,但为了让实验的结果对比更为容易,同时排除AD7616各通道间性能差异的影响,序列栈寄存器设置为对同一个输入通道VINO进行连续多次采样,这样在一次“V型采样”中,VINO先后总共被采样1 5次,分别定义为SO-S14,如图1 1所示。

数据计算中,把SO与S14配对并取均值,S1与S13配对取均值,以此类推,但S7不参与任何平均计算。这样,将(SO+S14)/2,(S1+S1 3)/2,(S2+S12)/2, (S3+S11)/2,(S4+S10)/2, (S5+S9)/2, (S6+S8)/2的平均值结果,与S7的VINO原始信号进行比较,获得测试结果。

测试中,AD7616的VINO量程设置为±10V,输入正弦波的幅值为9.6Vp,(即-0.352 dBFS),分别设定输入正弦波频率为50Hz,250Hz,2550Hz(50Hz电力线基频的5次,51次谐波)进行测试。

当输入信号为50Hz正弦波(电力线基频)的测试结果如表1所示。

由表1可以看出,对于50Hz输入信号采用平均值计算得到的结果相对于原始信号的幅值和相位误差完全在可接受的范围内。事实上,在采用平均值计算时,由于过采样(前后共两次采样)的存在,相比单次采样时的信噪比(SNR)性能还略有提高。

当输入信号为250Hz正弦波(50Hz电力线基频的5次谐波)的测试结果如表2所示。

当输入信号的频率提高到250Hz时,幅值有-O.OOldB衰减,相当于0.1%,与之前数学公式推导的结果一致,相位误差完全在可接受的范围内。

当输入信号为2550Hz正弦波(50Hz电力线基频的51次谐波)的测试结果如表3所示。

当输入信号的频率提高到2550 Hz时,“V型采样+数据平均”所带来的误差开始比较明显。SO与S14的间隔最远,因此平均值的计算结果是误差最大的情况,对比S7,误差为-0.055dB,相当于6.3‰的误差,与数学公式推导的结果一致。S7幅值的计算结果为-0.38ldBFS,对比50Hz时有所衰减,这是由于AD7616内部低通滤波器的滚降所致,并非“V型采样+数据平均”所带来的误差。

6 结论

对输入为50Hz、250Hz、2550Hz正弦波的测试数据也可以看出,AD7616配置在“V型采样+数据平均”模式下的实验结果完全符合数学理论推导的结果。

受益于AD7616的lMsps高采样率,通过配置AD7616内部的序列栈寄存器,在“V型采样+数据平均”的模式下,非同步采样型的AD7616也可以实现各个模拟量输入通道之间近似于同步的采样,因此称为AD7616的准同步采样。

大多数电力自动化应用中需要测量的信号在50 Hz到2550Hz范围内,如果采用AD7616来实现准同步采样,系统的交流幅值测量误差以及通道间的相位失配误差都降至可以接受的范围内,并且显著降低了系统的成本。

参考文献

[1]AD7616 datasheet. 16-Channel DAS with 16-Bit, Bipolar Input, Dual Simultaneous SamplingADC. Analog Device Inc.

[2]ADSP-CM408F datasheet. 240MHz ARM Cortex-M4 with 13+ ENOB ADC. Analog DeviceInc.

[3]Audio Precision. AP2700 series.

[4]Visual Analog. Analog Device Inc.endprint