基于FPGA的SD-SDI视频传输系统设计

刘梁然,何宇奇,周宽

(中国电子科技集团公司第十一研究所北京100015)

基于FPGA的SD-SDI视频传输系统设计

刘梁然,何宇奇,周宽

(中国电子科技集团公司第十一研究所北京100015)

在红外成像处理技术方案中,现如今比较成熟的红外图像处理设计是基于FPGA(Field-Programmable Gate Array,现场可编程门阵列)+Nios软核的构架,经过处理的红外视频信号既可以转化成模拟视频输出,也可以根据系统的需要转换成其他数字视频格式输出。本文提出了一种基于FPGA的标清SDI(Standard Definition-Serial Digital Interface)视频传输系统设计。该设计采用FPGA实现SDI标准时序设计,结合外部线缆驱动的方式完成SDI图像数据的传输。FPGA采用Altera公司的EP3S系列芯片。实验调试结果表明,SD-SDI数字视频信号处理及传输工作稳定可靠,目前已应用于实际工程当中。

SD-SDI;FPGA;VHDL;LVDS

红外成像设计常用模拟视频输出以便在监视器上直接成像观看,为了将现有模拟视频系统接入到数字串行视频系统,需要将模拟视频转换成SDI信号。SDI接口作为当前主要的数字视频外部接口,可以实时地传送无压缩的视频数据,其高质量的视频信号,对我国视频监控系统及广电设备而言具有重要作用。目前,国际上如NS、GENNUM公司针对广电行业的SDI芯片种类繁多,但价格普遍较高。一方面采用这种专用的SDI转换芯片实现SDI视频接口的方案对于安防行业来说并不太合适。安防产品出货量大,对成本控制非常严格。同时鉴于安防领域对低成本SDI标准视频接口的要求。另一方面在红外成像处理设计中,基于FPGA+Nios软核的构架,可以利用FPGA来实现SDI标准的视频输出,减少其他视频转换芯片的使用而节约成本和减少硬件设计空间。本文提出了一种以FPGA作为视频接口转换芯片的更加灵活的低成本解决方案。该方案采用FPGA内部逻辑资源实现SDI标准时序,并结合外部线缆驱动的方式实现SDI视频数据的传输。

1 系统总体结构

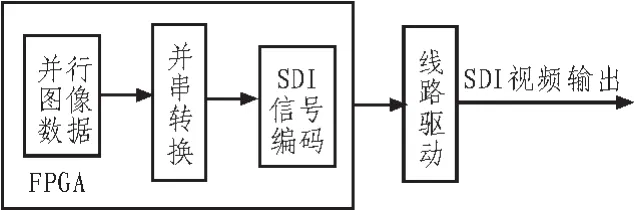

本文提出的SDI视频传输系统以Altera公司的一款EP3S系列FPGA作为核心器件,采用VHDL语言生成ITU-R BT656格式的并行测试图像数据,然后实现数据的并串转换以及SDI信号编码,最后FPGA输出的串行数据经过线路驱动输出幅度为800 mV的标准SDI信号。

SDI接口采用75欧同轴电缆传输未经压缩的数字视频信号,在SMPTE259M中规定了A、B、C、D 4种标准,传输速率分别为143 Mbit/s、177 Mbit/s、270 Mbit/s、360 Mbit/s,其中最常见的是270Mbit/s[1]。本文实现的SD-SDI视频传输方案符合SMPTE259M LEVELC标准,数据传输速率270 Mbit/s[1]。系统总体结构框图如图1所示。

图1 系统总体结构框图

本文提出的SDI视频传输系统包括软件设计和硬件设计两部分。软件设计包括采用VHDL语言生成测试图像数据,完成并行数据的并串转换以及SDI信号编码。硬件设计完成对FPGA输出差分信号的线缆驱动。本设计中并串转换模块的读存储器时钟为270 MHz,而Altera公司 EP3S系列 FPGA内嵌SRAM支持最高600 M时钟的读写操作,LVDS接口支持最高800 MHz速率的数据传输,因此完全满足设计要求。另外,由于FPGA引脚输出的差分信号满足ANSI/TIA/EIA-644 LVDS标准,与SDI接口遵循的SMPTE259M标准不兼容,因而需要对其进行线缆驱动,以满足SDI视频采集卡的接收要求。具体设计方案见第2节。

2 系统具体设计

2.1 软件设计

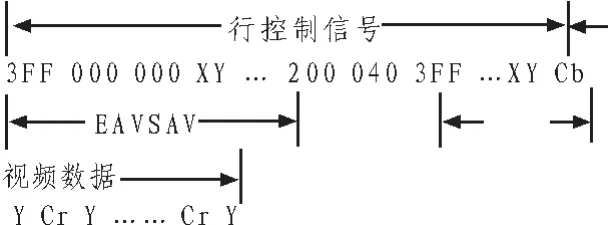

本设计首先采用VHDL语言生成ITU-R BT656格式的并行测试图像数据流[2],每行的数据结构如图2所示。

图2 ITU-R BT656格式数据流

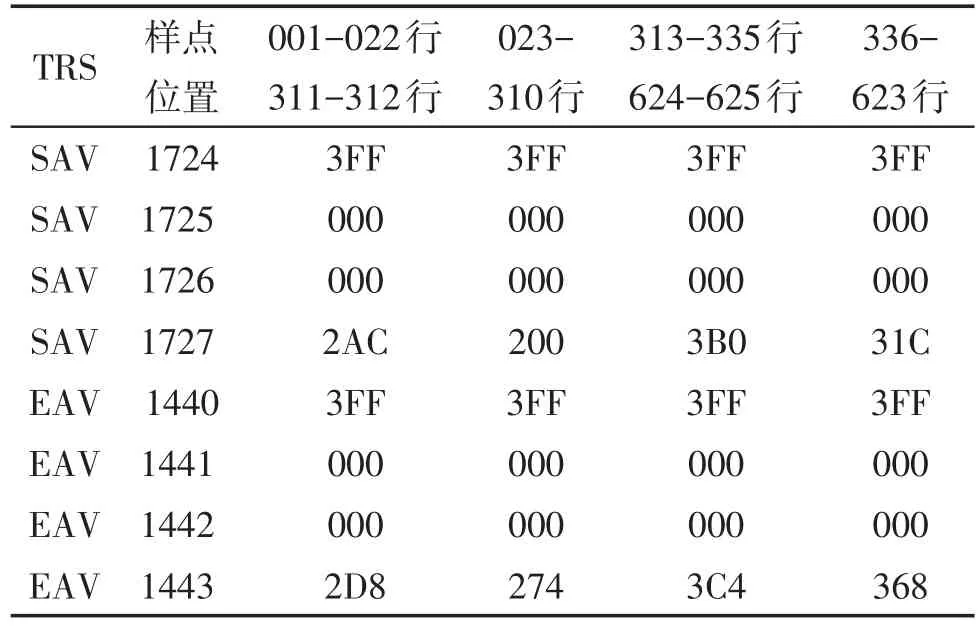

数据流数据宽度为10 bit,包含4:2:2的YCbCr视频数据,并内嵌有水平同步控制信号。一帧测试图像数据包含625行,每行1728 bit。其中23~310行是偶场视频数据,336~623行是奇场视频数据,其余为垂直控制信号[2]。视频信号排列顺序为Cb-Y-Cr-Y。SAV(有效视频起始)和EAV(有效视频结束)信号有3个字节的前导:3FF、000、000,最后1个字节的XY表示该行位于整个数据帧的位置及如何区分SAV、EAV[3]。一帧当中每行的SAV和EAV在数据流中的定义如表1所示:

表1 SAV和EAV在数据流各行中的定义

图像数据的并串转换仍然采用VHDL语言实现:在FPGA内部,并串转换模块将满足ITU656标准的并行数据流在字节时钟(27 MHz)的控制下并行写入移位寄存器,然后在位时钟(270 MHz)的控制下串行读出,完成并串转换,产生270 Mbps的串行图像数据流。

最后,串行数据再通过SDI信号编码——扰码和NRZ-NRZI编码转换为SDI视频数据。扰码操作先将信号编码为NRZ(不归零)扰码信号,再把NRZ扰码信号转换成对电平极性不敏感、只对电平极性变换敏感的NRZI(倒相不归零)信号。

在数据传输时,首先需要通过生成多项式(1)的计算:

形成NRZ(不归零)信号。目的是重新排列串行数据流,减小长串的连“0”和连“1”,从而使电平跳变多、时钟信息丰富。其次,串行数据中如果“0”电平或“1”电平持续的次数过多的话,在接收端不利于从接收数据信号中恢复时钟信号。因此利用生成多项式(2)对NRZ信号作第2次计算:

得到NRZI(倒相不归零)信号。

扰码模块的原理图框图如图3所示[3]。

图3 SDI扰码原理框图

2.2 硬件设计

经过扰码形成的SDI数据流通过FPGA的LVDS引脚以差分信号形式输出,然后进行线缆驱动。线路驱动选用国家半导体公司的CLC001芯片,该芯片采用3.3 V电源供电。该芯片专为SMPTE 259M串行数字视频和ITU-TG.703串行数据传输而设计,在75 Ω同轴线缆上最高传输速率可达622 Mbps。CLC001输出电压幅度可以通过调节一个外部参考电阻的阻值来改变,该电阻的典型值为1.91 kΩ(输出幅值800 mV)或为1.5 kΩ(输出幅值1 000 mV)。线路驱动电路只需要CLC001和几个外部电阻、电容即可,原理图如图4所示。

图4 线缆驱动原理图

3 实际应用与测试

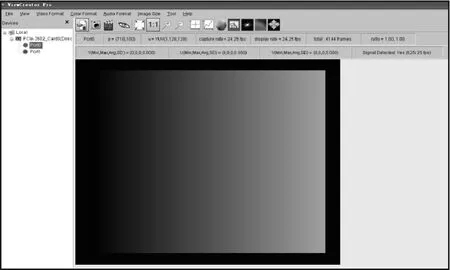

本设计采用ADLINK公司的型号为PCIe-2602的SDI视频采集卡进行图像显示测试。经过测试,本系统能够以25帧/s的速率发送720*576分辨率的标清SDI视频图像,并在PC机上正确显示。从测试结果可以看出图像清晰稳定,显示效果良好。

图5 SDI视频图像显示效果图

4 结论

本文设计并实现了一种基于FPGA的SD-SDI视频传输系统。经测试该系统具有低功耗、低成本、设计灵活、设计周期短等一系列特点,成像效果清晰、稳定,能满足视频监控场合的应用。由于该设计采用FPGA实现视频时序,在以Channallink接口输出LVDS差分信号的系统中,都可以通过以更改软件程序并外接线缆驱动的方式实现SDI接口标准的视频输出,具有很实际的工程意义。目前该设计已应用于实际工程当中。

[1]聂杨,陶庆肖.基于FPGA的模拟视频转SDI的转换器设计与实现[J].电子产品世界,2013(3):54-56.

[2]ITU-RBT.656,Interfacefor digital component video signals in 525-line and 625-line television systems operating at the 4:2:2 Level of Recommendation ITURBT.601[S].2010.

[3]SMPTE-259M,Television10bit4:2:2 component and 4FSC composite digital signal serial interface[S].2011-03.

[4]徐大鹏,孙海江.HD-SDI视频嵌入式图像采集系统设计[J].计算机测量与控制,2015,23(9):16-20.

[5]李鸿强,苗长云.高清晰度数字视频SDI卡的设计[J].电子器件,2012,24(10):24-27.

[6]陈东成,朱明,郝志成.基于FPGA的Camera Link转HD-SDI接口转换系统[J].液晶与显示,2014,(6):66-69.

[7]田佳天.基于FPGA的高清SDI测试信号源的硬件设计与实现[D].北京:北京邮电大学,2011.

[8]朱超,刘艳滢,董月芳.基于FPGA的SDI到Camera Link视频接口转换系统设计[J].测控技术,2011,30(2):15-29.

[9]杨润利,宋文生,周宇,等.基于FPGA的3G/HD/SD-SDI信号光纤传输系统的设计[J].电子产品世界,2015,22(9):36-42.

[10]梁国龙,何丁龙,张磊.Camera Link Full至HDSDI接口的高清传输显示系统[J].液晶与显示,2016(4):36-40.

[11]杨帆.基于FPGA的SDI接口的研究与开发[D].天津:天津理工大学,2010.

[12]黄隶凡,郑学仁.基于FPGA的三速SDI设计[J].电视技术,2011,35(3):13-18.

[13]岳元,彭量节.SDI红外图像在火炮光电跟踪系统中的应用[J].激光与红外 2016,46(8):1024-1027.

[14]杨洋.基于FPGA的4路HD-SDI光纤传输系统[J].光通信技术,2015,39(5):97-103.

[15]苏建,林水生.基于FPGA的SDI接口设计[J].中国有线电视,2015(24):62-68.

[16]李彦迪,金伟正,王丹.基于FPGA的HD-SDI编解码技术的研究与开发[J].电子技术应用,2012(12):16-21.

[17]党俊博,李哲,李雅俊.基于FPGA的串口通信电路设计与实现[J].电子科技,2016(7):106-109.

[18]罗帅,徐进,夏杰,等.一种光纤数据采集系统的设计[J].西安工程大学学报,2016(3):312-315.

[19]严明,李斌康,郭明安,等.高速光电探测器阵列实时信号处理系统[J].现代应用物理,2014(4):316-321.

FPGA-based SD-SDI transmission system design

LIU Liang-ran,HE Yu-qi,ZHOU Kuan

(Eleventh Research Institute of China Electronics Technology Group Corporation,Beijing100015,China)

In the technical scheme of infrared imaging processing,now more mature design of infrared image processing is based on FPGA(field programmable Gate Array field programmable gate array)architecture of+Nios core,through the infrared video signal processing can be transformed into analog video output,can be converted into other digital video format output according to the needs of the system.The system of FPGA-Based standard definition SDI transmission presented in this article.The system uses FPGA to achieve the SDI standard timing design,completing the transmission of SDI image data by the way of combined with the external cable driven.FPGA uses EP3S company’s Altera series chip.The experimental results show that the SD-SDI digital video signal processing and transmission is stable and reliable.It has been applied in practical engineering.

SD-SDI;FPGA;VHDL;LVDS

TN911.72

A

1674-6236(2017)23-0094-03

2016-10-18稿件编号:201610090

刘梁然(1991—),男,四川眉山人,助理工程师。研究方向:红外探测器成像电路设计。