基于频域辨识的合并单元额定延时测量技术

庞福滨,刘玙,嵇建飞,袁宇波,卜强生

(国网江苏省电力公司电力科学研究院,南京211103)

0 引 言

在智能变电站中,合并单元将各路互感器采集到的电压、电流信号进行合并处理,并按照规定的协议生成采样值报文传输给二次设备,简化了二次设备的硬件结构,实现了数据共享,在数字化变电站的建设中有着不可或缺的作用[1-4]。然而,数字量取代模拟量传输,会不可避免地引入信号的采集、传输、处理等环节的延时,进而影响继电保护装置对保护速动性的要求[5-7]。为了保障电网系统的安全运行,使继电保护装置能够快速有效地切除故障,必须减小合并单元环节引入的延时,而这又以准确地测量出延时的大小为前提。目前,常用的延时环节的测量方法有间接法和直接法[8-10],前者通过比较工频输入量经过合并单元后SV报文输出的相位与模拟输入量之间的相位差,并将其换算为对应的时间延时,这种方法包含了互感器一次传感单元及合并单元本身的相位传变特性,导致测量结果存在偏差[11];直接法则对互感器及合并单元外接同步脉冲,通过对比测试仪接收SV报文生成时刻与报文采样的时间差来计算合并单元的输出延时,这种方法测量精度高[12],但硬件实现较为复杂,测试成本高。鉴于此,本文首先了介绍合并单元环节延时的构成部分,分析了其采样、传输及处理过程中的延时特性,将合并单元看作滤波器系统,研究了其输出相位与频率之间的线性关系,并提出了基于频域识别的合并单元延时测量技术。

1 采样延时特性分析

1.1 采样延时的构成

互感器将一次电气量转换为二次信号,并经由A/D转换将其转化为数字量,再由合并单元对各路数字量进行打包处理,生成SV报文发送给保护、测控等间隔层设备,整个采样延时环节构成图如图1所示。

图1 采样延时环节构成图Fig.1 Composition diagram of sampling delay time

从图1可以看出,智能站中采样延时的构成包括以下环节:

ttrs1:一次电气量经由互感器转换为二次量,并传输到A/D采样装置的传输时间,称为传变延时,互感器的传变延时与输入信号的频率、互感器自身的特性及外界环境有关[13];

tcvt:A/D采集装置将二次模拟量转化为数字量的转换时间,目前主流的16位A/D转换芯片其转换时间一般为微秒量级或更小。当采用电磁式互感器时,A/D采样环节集成在合并单元内部;

ttrs2:数字量到合并单元的传输时间,此值一般较小,可以忽略;

twat:合并单元等待各路采集装置的数字信号到达时间,当存在合并单元级联时,还包括各间隔的合并单元SV报文等待时间;

tpak:合并单元对各路数据进行处理,并打包生成SV报文的时间;

ttrs3:SV报文传输到间隔层设备的时间,可以忽略不计。

在图1中,除ttrs1为互感器的传变延时外,称其余各项的和为合并单元的额定延时。为保证各环节所消耗时间的时间是确知的,A/D数据的转换、合并单元等待SV报文及数据打包发送等环节均是基于中断方式完成的,且中断信号一般为采样周期的整数倍[14]。图2给出了系统的工作流程图。

图2 系统工作流程图Fig.2 System working flow chart

如图2所示,t1时刻,在中断采样脉冲的触发下,A/D采集装置对互感器输出二次模拟量信号S(t1)进行采样,经过tcvt后将该信号转换为数字信号,在ttrs2后将数字信号传送至合并单元;此时,为了提高处理效率及等待其他路信号的到来,合并单元并不是在S(t1)的数字信号到来后就进行接收处理,而是等待twat后,在处理中断脉冲的触发下开始对该数据进行打包处理,并经过tpak后,在t2时刻,也即下一个中断处理脉冲到来时将生成S(t1)的采样值报文,并开始采集二次模拟量信号S(t2)。

1.2 额定延时的现有测量方法

目前,针对合并单元额定延时的测量方法主要有间接法和直接法,两种方法在测量机理上有所区别,所测结果的精度也不相同。

(1)间接法

图3 间接法测量原理示意图Fig.3 Schematic diagram of indirect measuring theory

如图3所示,间接法将一次电气量输入标准互感器,标准互感器输出两路信号:一路通过电子式互感器或模拟量输入合并单元输出SV报文到延时测试仪,另一路直接将二次模拟量信号输出到延时测试仪。通过对比合并单元输出信号滞后于标准互感器直接输出二次信号模拟量之间的相位差Δφ及信号频率f,即可得到合并单元的额定延时:

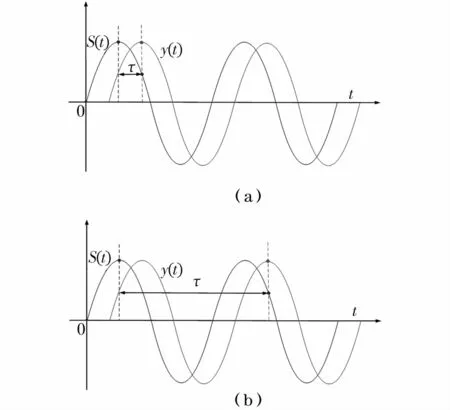

间接法是实际工程中应用较多的测量方法,但该方法存在两个缺陷:一是测量的结果并非合并单元自身的额定延时,它还包含了由互感器引入的传变延时,导致合并单元额定延时的测量出现偏差;二是这种方法无法区分相位差超过2π的额定延时情况,如图4(a)中所示,输出 ()y t相对输入 ()S t的延时较小,其相位差为2πfτ<2π;但当合并单元的延迟较大或信号频率较高时,可能出现输出 ()y t相对输入 ()S t的延时超出整周期的现象,如图4(b)所示。此时输出 ()y t相对输入 ()S t延迟了一个整周期,即2πfτ>2π。虽然国内要求合并单元的延时不大约2 ms,但在实际工程应用中,故障情况下可能出现采样延时超过一个整周期的现象[15],如果不能准确测量出此延时,就会导致保护装置不正确动作而跳闸,给变电站的安全运行埋下隐患。

图4 合并单元额定延时不同情况示意图Fig.4 Schematic diagrams ofmerging unit rated delay time under different situations

(2)直接法

针对间接法的弊端和不足,工程中提出了测量合并单元额定延的直接法,其测量原理如图5所示。

图5 直接法测量原理示意图Fig.5 Schematic diagram of indirectmeasuring theory

从图5中可以看出,直接法较间接法增加了GPS时间同步装置。其测量原理为:互感器转换的二次信号通过A/D转换生成数字信号,并将其送入合并单元以生成SV报文。加装GPS时间同步装置后,外部同步信号输出分两路:一路到合并单元,另一路到延时测试仪。其中,在外部同步信号的触发下,合并单元接收A/D转换装置发送的采样信号,并通过打时标的方式标记出信号接收时间,再生成SV报文发送到延时测试仪;延时测试仪接收合并单元发送的SV报文并记录下接收时刻,此时刻相对于合并单元接收A/D转换装置发送的采样信号的接收时间滞后了时间τ,显然τ即为合并单元的额定延时时间。为了简化测试,一般选取0号报文为标识的SV报文。由直接法的测量原理可以看出,该方法隔离了测量过程中可能引入的互感器的传变延时,直接对比合并单元接收A/D转换装置输出的采样信号与合并单元输出SV报文之间的时间差,测量结果的精度更高。

2 基于频域识别的延时测量原理

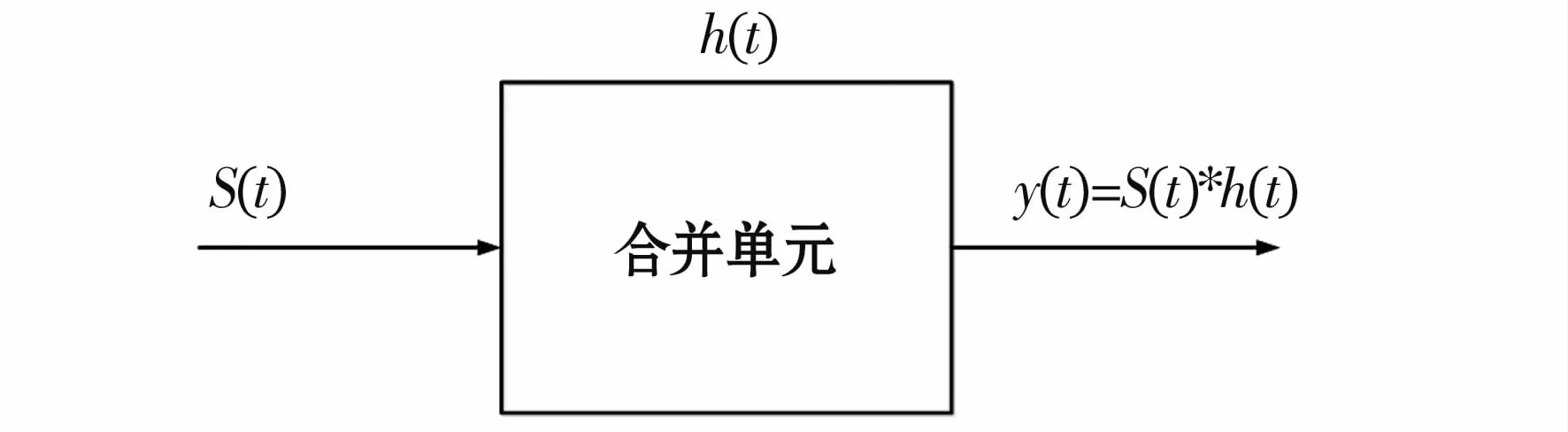

合并单元接收各路数字信号,并对数据进行处理打包,生成SV报文发送给间隔层设备,输入信号S(t)与输出信号 y(t)与关系如图6所示。

图6 合并单元输入与输出关系示意图Fig.6 Relationship schematic diagram of input and output of MU

不论信号S(t)的频率如何改变,通过合并单元后,输入信号S(t)的幅度并未发生改变,只是输出将输入信号延迟了τ的时间,因此可将合并单元看作一个延时滤波器。设合并单元的单位脉冲响应为h(t),则通过合并单元后信号的输入输出关系可以表示为:

在频域上,输入输出则存在如下关系:

其中 S(j w)、Y(j w)分别为 S(t)、y(t)的频谱。当只存在时间延迟时,合并单元相当于线性相位滤波器,其传递函数为:

因此,输出信号与输入信号的频谱关系为:

进而可得:

式(6)表明,根据输入信号和输出信号频谱的相位差和信号频率w,可求得合并单元的额定延时,这就是频域辨识的合并单元额定延时的测量方法。 但在实际应用中,式(6)存在一定的问题:在利用arg函数提取输出信号与输入信号频谱比时,由于arg函数得到的相位在[-π,π]之间,因此式(6)无法区别出输入信号与输出信号频谱相位差超过2π的情况,即间接法测量时存在的无法区分相位差超过2π的额定延时。为避免这种现象,可以通过输入不同频率的信号,得到合并单元的相频特性曲线。当输入信号的频率较低时,信号的周期较长,则不会出现合并单元额定延时测量差出整周期的现象。例如,当输入信号频率为1 Hz时,其周期为1 s。而合并单元的额定延时不会超过1 s,这就避免了测量过程中出现相位差超过2π的情况。

3 仿真计算

为了验证基于频域识别的合并单元额定延时测量方法的有效性,采用MATLAB的Simulink建模功能对其进行了仿真计算,仿真模型示意图如图7所示。

图7 基于频域辨识的额定延时测量模型示意图Fig.7 Measuringmodel schematic diagram of rated delay time based on frequency domain identification

图中Sine Wave为输入信号源模块,Transport Delay为合并单元额定延时模块,输入信号通过合并单元后,其时域波形输出到Scope模块的一通道;其频域分别经Fourier和Fourier1模块进行傅里叶变换,并提取输入信号与输出信号频谱的相位差,输出到Scope模块的二通道。这样,通过输入不同频率的信号,可以得到不同频率下合并单元的相频特性曲线,并根据相频特性曲线的斜率即可求得其额定延时的大小。

在仿真过程中,输入信号的扫描频率为1 Hz~100 Hz,合并单元的额定延时设置为1 500μs,分别对输入信号和经过合并单元延时后的输出信号进行傅里叶变换,并求得输入信号与输出信号频谱的相位差,得到图8所示的合并单元相频特性曲线。可以看出,合并单元的相频特性为一条过原点的直线,曲线的斜率即对应了其额定延时的大小。取频率为80 Hz时,合并单元相频特性曲线对应的相位差为43.2°,根据式(6)可得:

显然,理论计算结果与实际设定值相符,验证了频域辨识法测量合并单元额定延时的正确性。但在实际工程应用中,频域辨识法仍会引入互感器自身的传变延时,从而改变合并单元的相频特性曲线,影响额定延时测量的结果。为了分析互感器传变延时对合并单元额定延时测量的影响,选用了某厂家生产的合并单元进行仿真计算。该合并单元传变延时特性可等效为二阶低通滤波器:通带截止频率为2 kHz,3.3 kHz处衰减幅度为 6 dB,经计算其传递函数为:

图8 合并单元相频特性曲线图Fig.8 Curve chart ofmerging unit phase characteristics

仿真可得其幅频和相频特性曲线如图9所示,合并单元的传变特性在低频时衰减较小,随着频率的升高其幅度衰减逐渐增大;低频时其相位偏移较小,随着频率的升高相频特性偏移增大。

图9 合并单元幅频、相频特性曲线图Fig.9 Curve chart ofmerging unit amplitude and phase characteristics

图10给出了考虑传变延时后,输入频率为1 Hz~100 Hz时采用频域识别法得到的合并单元相频特性曲线。

图10 考虑传变延时的合并单元相频特性曲线图Fig.10 Curve chart ofmerging unit phase characteristics allowing for transmission delay

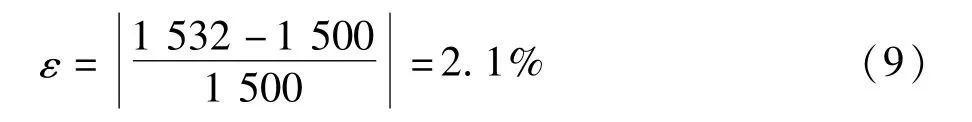

对比图9和图10可以看出,合并单元的相频特性曲线变化不大。为了减小单频率点测量造成的延时测量误差,计算了1 Hz~100 Hz时每个频点的额定延时,并对其进行取平均。计算结果为1 532μs,则传变延时导致的合并单元额定延时测量误差为:

因此,合并单元的传变误差相对其额定延时很小,可以认为频域识别法测得的合并单元延时大小即为其额定延时。在测量过程中,选用低频率的扫描方法有两个优点:一是频率低时信号周期较大,这就大大减小了额定延时测量时出现的信号差出整周期的可能性;二是频率较低时,合并单元的传变延时特性对应的相位偏移较小,其额定延时测量的准确性也越高。

4 结束语

合并单元的额定延时直接关系到继电保护动作的时间,其大小必须得到准确测量。本文根据合并单元的工作原理及流程,分析了其采样环节的延时中传变延时和额定延时的构成,介绍了合并单元额定延时的测量方法。针对现有测量方法的不足,研究了合并单元额定延时引起的输出信号与输入信号频谱之间的相位差的偏移,发现时域中的延时特性对应频域中的线性相位,据此提出了基于频域辨识的额定延时测量方法。理论分析和仿真结果表明,频域辨识法可以有效地测量合并单元的额定延时,为数字化采样工程中测合并单元额定延时的测量提供了一种新的可行方法。