基于FPGA的RGMII与MII协议转换器的实现*

周建文,吴伶锡,唐峦石,詹 杰

(湖南科技大学 物理与电子科学学院,湖南 湘潭 411201)

基于FPGA的RGMII与MII协议转换器的实现*

周建文,吴伶锡,唐峦石,詹 杰

(湖南科技大学 物理与电子科学学院,湖南 湘潭 411201)

为提高嵌入式系统在网络应用的灵活性,降低接口实现和维护成本,通过分析研究MII和RGMII以及以太网IEEE802.3推荐标准,结合FPGA强大的数据处理能力和可重配置能力,设计实现了RGMII与MII接口协议转换器。仿真实验结果表明,该接口转换功能实现正常,工作稳定,有效解决了传统嵌入式系统接口灵活性差和维护成本高的问题,并为其他信号接口系统的设计实现提供了有益的参考。

MII接口;RGMII接口;FPGA;嵌入式系统

0 引言

在网络通信链路中,需要将MAC与PHY连接,用于网络数据的传输,常用的接口有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

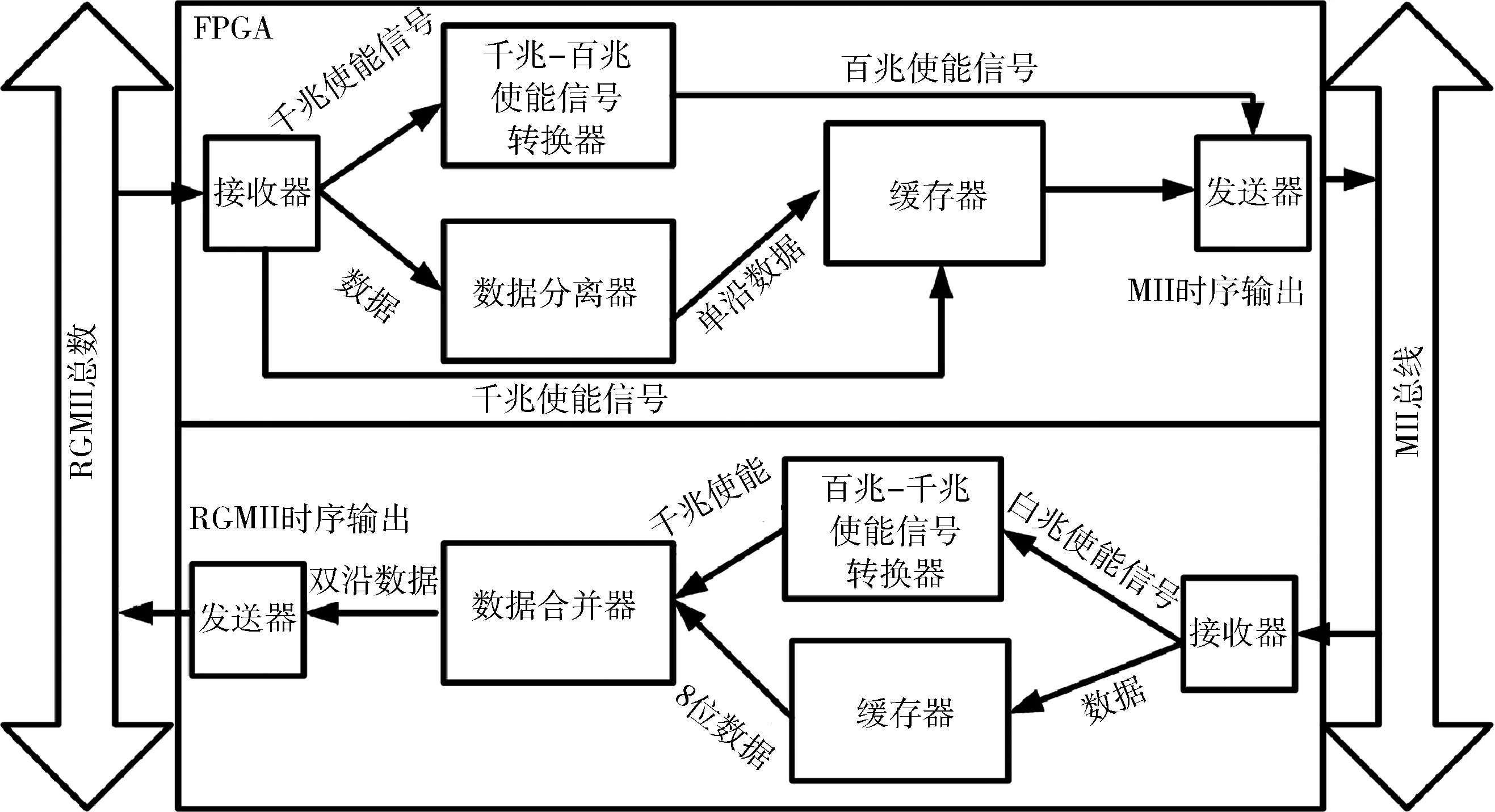

图1 系统原理图

尽管这些接口已经应用于各种嵌入式系统的以太网通信中,但是由于每个PHY和MAC器件产品所使用的接口类型不完全一致,并且每种以太网接口都有各自的通信协议标准,需要双方进行协议转换才可实现通信[1],而且有些接口因为信号线过多,造成系统布局布线复杂以及功耗增加,通过协议转换可以降低系统功耗[2]。

为了改善系统性能,提高数据在系统中传输的兼容性[3],本文通过分析研究以太网IEEE802.3标准,深入剖析MII和RGMII收发时序,采用模块化方式[4]设计系统的总体架构,在功能上设计并实现了基于FPGA的RGMII与MII的接口转换模块。

1 系统工作原理

RGMII和MII接口能够通信,其原理是将两种接口的数据分别进行变换得出双方都可以接收的时序[5],系统原理如图1所示。

在RGMII转换成MII时,数据和使能信号先被接收器接收,因RGMII的双沿采样特性,需将数据传入数据分离器,经分离器输出单沿数据,再以千兆使能信号作为缓存器的写使能,RGMII的GRX_CLK时钟作为缓存器的写时钟,把单沿数据存入缓存器。将经过千兆-百兆使能信号转换器处理后的百兆使能信号作为缓存器的读使能信号,以MII工作时钟25 MHz作为缓存器读时钟,提取数据后经发送器以MII接口时序发送出去。

图4 RGMII-MII使能信号产生示意图

由MII转换成RGMII时,以MII_RX_CLK作为缓存器的写时钟,MII_RX_DV作为写使能,将数据存入缓存器,再将百兆-千兆使能信号转换器处理之后的千兆使能信号作为缓存器的读使能,RGMII的125 MHz工作时钟作为读时钟,将数据提取送入数据合并器,最后将千兆使能信号和双沿数据结合,以RGMII时序发送出去。

系统将产生3种工作状态:第一种是监听总线是否有数据传输,如果有数据传输则进行数据转换,即进入第二种状态,转换处理完成之后才能将数据用于发送,则将进入第三种状态。发送完成后又继续监听系统总线传输信号,系统在这三种状态中循环,如图2所示。

图2 接口转换图

2 FPGA逻辑设计

MII接口应用在100 Mb/s速率时,TX_ER、RX_ER都不起作用,而且目前的嵌入式系统中以太网通信速率基本都是运行在100 Mb/s模式下,而且在TX_EN/RX_DV信号有效的前提下TXD/RXD数据信号才有效,并且CRS和COL只在半双工模式下有效,所以在全双工和100 Mb/s的模式下,将这4个信号优化并不影响整个系统的性能(如图3),优化后不但可以提高布局布线能力和整个系统的性能,而且对RGMII和MII接口的通信提供了支持。

图3 接口信号简化图

在RGMII向MII转换过程中,将RGMII的使能信号转换成MII的使能信号,同时还需将RGMII数据时序转换成MII的数据时序。

RGMII-MII使能信号转换通过图4方法得出(图中的使能信号长度不表示实际长度,只是示意产生的过程)。因为FIFO具有亚稳态保护措施[6],如图4在FIFO内部的读空信号Rdempty为低电平就避免了进入亚稳态[7],因此以Rdempty由高变低时作为读FIFO开始,由低变高时作为读使能结束,即将Rdempty信号反向之后则产生了MII时序的使能信号[8]。

RGMII-MII的数据时序通过以下方法转换。因为数据在RGMII中是双沿采样,在MII中是单沿采样,所以使用FPGA的双数据速率接口(Double Data Rate I/O,DDIO)[9]将数据的采样沿进行变换。将RGMII信号中的TX_EN信号作为DDIO的使能输入端,其4位数据线作为DDIO端口的数据输入端,将其变化成单沿采样数据类型,因此DDIO将产生8 bit的数据输出。因为MII的接口是4 bit,需将经过DDIO处理之后的输出数据存入缓存器,变换成4 bit的输出数据发送给MII接收端,因为设备之间进行通信一般都会使用ACK机制,而且应用在嵌入式系统中的以太网帧长度一般都是1 500 B左右,所以应建立一个8输入带使能输入端和4输出带使能输出端,缓存大小为2 048 B并且输入与输出时钟不相同的FIFO[10]。

根据DDIO时序图可知从输入到输出的转换大概需要一个时钟周期,因为FIFO的输入采样的数据是DDIO的输出,并且因为RGMII信号中的RX_DV用作DDIO的使能输入,所以FIFO的输入使能需要比RGMII的RX_DV延迟一个周期,因此将RGMII的使能信号延迟一个时钟周期作为FIFO的输入使能,正好符合时序要求。将FIFO的输出数据和使能信号一同发送到接收端则满足MII的时序。

因为MII比RGMII的工作时钟频率低,且RGMII上下沿采样都采样4 bit数据,而MII每个时钟周期只发送4 bit数据,如果MII接口每传入4 bit数据就直接将其转换成RGMII时序,则缓存器的状态几乎总是为空,且RGMII有一时钟边沿无数据采样,使得程序难以判断并且没有充分利用时钟采样沿。因此缓存完一帧数据后再进行发送。

MII-RGMII的使能信号转换如图5所示(图中的使能信号长度不表示实际长度,只是示意产生的过程)。

图5 MII-RGMII使能信号产生示意图

图7 RGMII-MII模块设计图

图8 MII-RGMII模块设计图

因为FIFO的Rdempty信号在无数据时总是保持高电平,有数据时总是保持低电平,而当MII_RX_DV由高变低时说明已经接收完一帧数据,由于FIFO写时钟和读时钟频率相差较大,为了保证最后几个写入的数据已经完成同步操作,所以在MII_RX_DV和Rdempty两个信号同时都为低电平时开始计数,计数值为3时说明FIFO里已经同步完毕,这时产生读使能信号开始端,当FIFO读完数据时Rdempty为高电平,则产生使能信号结束端。以此产生RGMII时序的使能信号。

将读取的数据送入DDIO处理之后输出双沿的数据时序,将使能信号和双沿数据以及时钟信号同步发送至接收端就完成了MII时序至RGMII时序的转换。系统运行如图6。

图6 系统运行流程图

图9 RGMII-MII仿真结果

3 逻辑验证与仿真

根据系统整体原理和运行流程使用模块化设计方法分别建立了RGMII-MII(如图7)和MII-RGMII(如图8)转换模块。

对图7设计模块进行仿真,得到结果如图9,RGMII的GRX_CLK时钟在使能信号的作用下,将RGMII_RXD[3..0]四位双沿采样的数据送入DDIO,数据分离输出DDIO_OUT[7..0]发送至缓存器,经过PLL移相后产生与数据及使能信号相符合的时钟信号MII_TX_CLK,从仿真图中可得信号满足MII时序。

图10 MII-RGMII模块仿真图

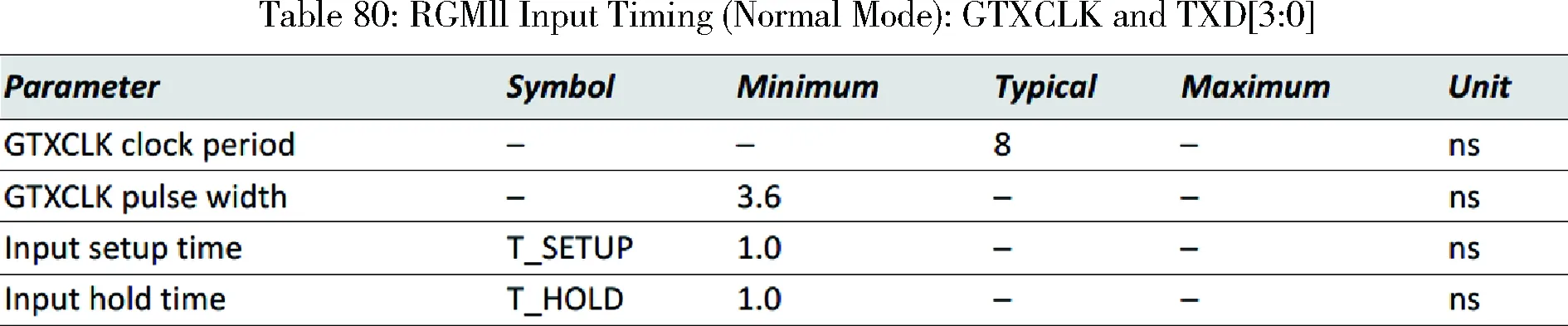

对MII-RGMII设计模块仿真,得到仿真结果如图10。MII_RXD[3..0]为四位数据信号线,在MII_RX_CLK时钟的作用下,将数据接收至FIFO缓存,缓存完一帧后送入数据合并器DDIO,经数据合并器处理之后从RGMII_TXD[3..0]引脚输出数据,最后经过发送器将RGMII_TX_EN信号和数据信号以及经过PLL移相后的GTX_CLK同步发送至外部接收端,结合收发器时序要求(如图11所示),得知结果满足时序要求。

图11 B50610收发器时序要求

4 结束语

本文通过对以太网MII和RGMII接口时序的分析研究,以Quartus II开发套件作为软件开发环境,以VHDL硬件描述语言实现了以太网MAC控制器的RGMII接口与MII接口通信,整个设计完成了代码的设计、仿真、逻辑综

合、布局布线和时序仿真验证,有效解决了传统嵌入式系统在以太网MAC层接口灵活性差和维护成本高的问题。

[1] 刘志华,郭付才,彭新伟,等. 基于CY7C68013A的FPGA配置和通信接口设计[J]. 电子技术应用,2013,39(2):18-21.

[2] 吴俊杰,吴建辉. 以太网MAC控制器的MII接口转RMII接口的实现[J].电子器件,2008(2):712-715.

[3] 侯义合,张冬冬,丁雷.基于FPGA+MAC+PHY的千兆以太网数传系统设计[J].科学技术与工程,2014(19):275-279.

[4] 张松,李筠. FPGA的模块化设计方法[J]. 电子测量与仪器学报,2014(5):560-565.

[5] 马飞,刘琦,包斌. 基于FPGA的AXI4总线时序设计与实现[J]. 电子技术应用,2015,41(6):13-15,19.

[6] 徐世伟,刘严严,刘红侠. 异步时钟亚稳态及FIFO标志位的产生[J]. 电子技术应用,2006,32(11):99-102.

[7] Yang Mengfei, Liu Bo, Gong Jian, et al. Architecture design for reliable and reconfigurable FPGA-based GNC computer for deep space exploration[J]. Science China(Technological Sciences),2016(2):289-300.

[8] 关世友,刘魁.基于FPGA的同步时钟报文检测电路的设计[J].计算机测量与控制,2010(11):2485-2487.

[9] Xing Kefei, Yang Jianwei, Zhang Chuangsheng, et al. Single event upset induced multi-block error and its mitigation strategy for SRAM-based FPGA[J]. Science China(Technological Sciences),2011(10):2657-2664.

[10] 庾志衡,叶俊明,邓迪文. 基于FPGA与DDR2 SDRAM的大容量异步FIFO缓存设计[J]. 微型机与应用,2011,30(4):34-36,40.

Implementation of RGMII and MII protocol converter based on FPGA

Zhou Jianwen, Wu Lingxi, Tang Luanshi, Zhan Jie

(School of Physics and Electronic Science, Hunan University of Science and Technology, Xiangtan 411201, China)

In order to improve the flexibility of embedded system in network application and reduce the realization and maintenance cost of interface, through analysing the MII and RGMII and Ethernet IEEE802.3 recommendation standards and combining with FPGA’s strong data processing capabilities and reconfigurable capabilities, we have designed and implemented the RGMII And MII protocol converter. Simulation results show that the interface conversion function is normal and stable, which effectively solves the problem of poor flexibility and high maintenance cost of traditional embedded system interface, and provides a useful reference for the design and implementation of other signal interface systems.

MII interface; RGMII interface; FPGA; embedded system

TN492

A

10.19358/j.issn.1674- 7720.2017.23.011

周建文,吴伶锡,唐峦石,等.基于FPGA的RGMII与MII协议转换器的实现[J].微型机与应用,2017,36(23):37-40,43.

国家自然科学基金项目(61540012)

2017-06-02)

周建文(1992-),男,硕士研究生,主要研究方向:电子电路设计。

吴伶锡(1964-),通信作者,男,硕士,教授,主要研究方向:传感技术与网络。E-mail:lxw241@126.com。

唐峦石(1973-),男,硕士,工程师,主要研究方向:高清LED显示屏控制系统及亮化控制系统。