一种高阶低通FIR滤波器的Matlab与FPGA实现

顾梦祺

(淮阴师范学院 物理与电子电气工程学院,江苏 淮安 223300)

一种高阶低通FIR滤波器的Matlab与FPGA实现

顾梦祺

(淮阴师范学院 物理与电子电气工程学院,江苏 淮安 223300)

滤波器是电子专业常用的信号处理工具,是用来减少或消除干扰的电气部件。文章基于FPGA开发的自顶向下层次化的设计思路,采用Matlab以及QuartusⅡ软件设计实现16阶低通滤波器,仿真以及实物测试结果都显示达到低通滤波性能。与传统的数字滤波器相比,FPGA器件更优越的性能使得所设计的滤波器具有更好的实时性、可移植性等。

Matlab;FPGA;滤波器;仿真

滤波器在各种控制系统中应用的极其普遍,其功能主要是对特定频率或者某频率之外的所有频率信号进行滤除,进而达到实现滤除干扰或噪声的目的。随着数字信号处理理论的不断成熟以及电子器件各方面性能的不断提升,越来越多的技术人员开始研究滤波器的实现方法。有限脉冲响应(Finite Impulse Response,FIR)数字滤波器的实现,一般可以分为硬件和软件两种设计路线。其中用软件实现方法是在普通计算机上用编程实现的。需要借用计算机的内存、计算器和控制算法编译,通过计算机执行滤波器的操作。因为这个方法很慢,所以很难用于对时间精度要求较高的信号进行处理,主要用于教学和研究。

硬件实现是专门设计的数字滤波电路,现在FIR滤波器的硬件设计有多种实现方法。(1)用单片机来实现,但单片机的处理速度相对较慢。(2)专用的数字信号处理(Digital Signal Processing,DSP)芯片,但DSP的串行指令执行使其速度和效率大大降低,所以随着滤波器系数或字长的增长,计算时间将大大增加,并且在一些高速应用中,DSP的性能增长的背后是系统需求的增长。(3)使用商用FIR滤波器集成电路,但由于其通用性,很难满足设计师的独特要求。(4)利用可编程逻辑器件来实现。

可编程逻辑器件如现场可编程门阵列(Field Programmable Gate Array,FPGA)等在电子技术领域的应用给数字硬件电路系统的设计带来了极大的灵活性和主动性。由于可编程逻辑器件可以由软件编程,其硬件结构可以随具体项目需要进行调整,所以其硬件设计和软件设计一样方便。

本文根据自顶向下的层次化、模块化的设计思想,将整个滤波器的设计划分为多个模块,利用硬件描述语言(Hardware Description Language,VHDL)的描述方法进行了各个模块的功能设计,并用Matlab软件设计16阶滤波器各抽头系数,最终在QuartusⅡ软件上进行编程仿真,并利用FPGA芯片对设计结果进行验证。

1 低通滤波器的设计

1.1 直接型滤波器结构

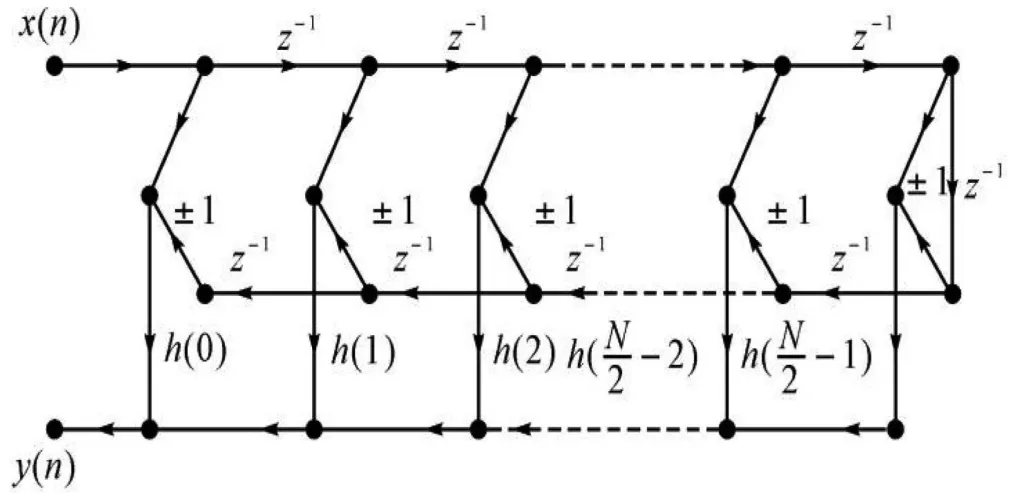

考虑到既要使滤波器工作速度快,又要使得相应的资源功耗比较少,所以选定用线性相位型来设计实现,且N=16为偶数,选用如图1所示的线性相位FIR滤波器对称结构。

图1 若N为偶数,线性相位FIR滤波器的对称结构

图中之路增益应取“+1”。如图1所示,要完成滤波器的设计,需包含延时单元、加法电路单元,乘以负一单元、乘法器单元及截取8位数单元的底层文件设计。

1.2 窗函数设计法

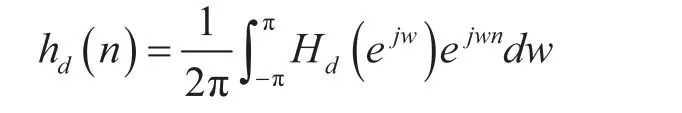

设计FIR数字滤波器最简单、最普通的方法是窗函数法。这种方法通常是理想滤波器的频率响应在给定的条件下,按照要求设计一个F I R滤波器频率响应去无限接近理想的频率响应通常使用窗函数法设计FIR数字滤波器是在时域中进行的,因此,必须首先由理想频率响应的傅里叶反变换推导出对应的单位脉冲响应hd(n),

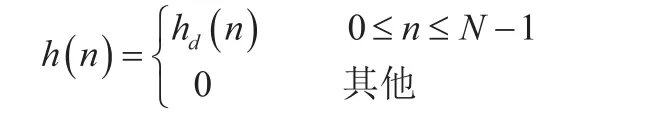

分段恒定的或分段函数表示的频率响应是用来定义许多理想系统的常用手段,但是这种系统具有非因果的和无限长的脉冲响应,即hd(n)一定是无限长的序列,且是非因果的。而我们要设计的是FIR滤波器,其h(n)必定是有限长的,所以要用有限长的h(n)来逼近无限长的hd(n),最简单且最有效的方法是截断hd(n)

可以把h(n)表示为所需单位脉冲响应与一个有限长的窗口函数序列w(n)的乘积,即

1.3 Matlab软件中设置滤波器系数

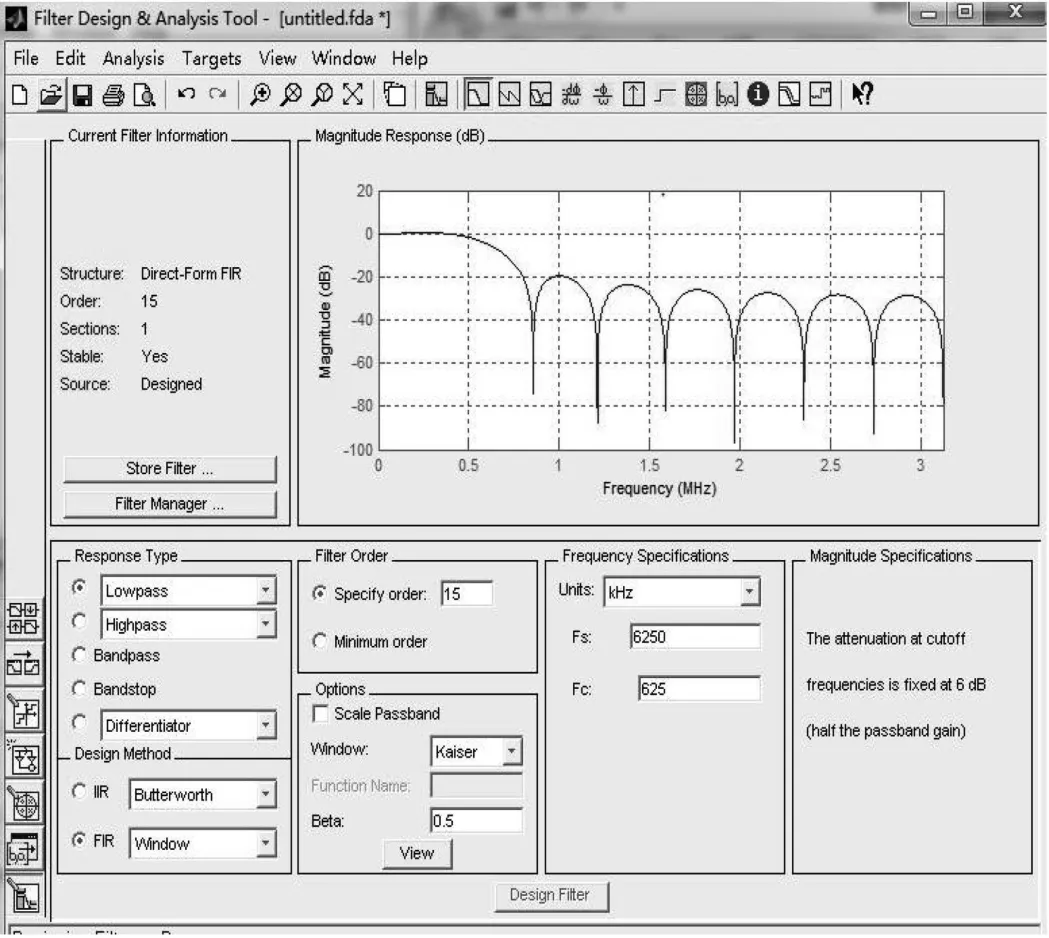

打开Matlab的FDAtool设计工具,分别设定响应类型为低通,设计方法为FIR,窗函数取Kaiser窗,Beta设为0.5,滤波器阶数指定为15,其采样频率为6.25 MHz,截止频率是625 kHz,如图2所示。完成滤波器参数设定后,单击设计滤波器按钮,即可得到设计滤波器的幅频特性、相频特性、冲击响应等。且可生成FIR滤波器系数为:

1.4 顶层文件设计

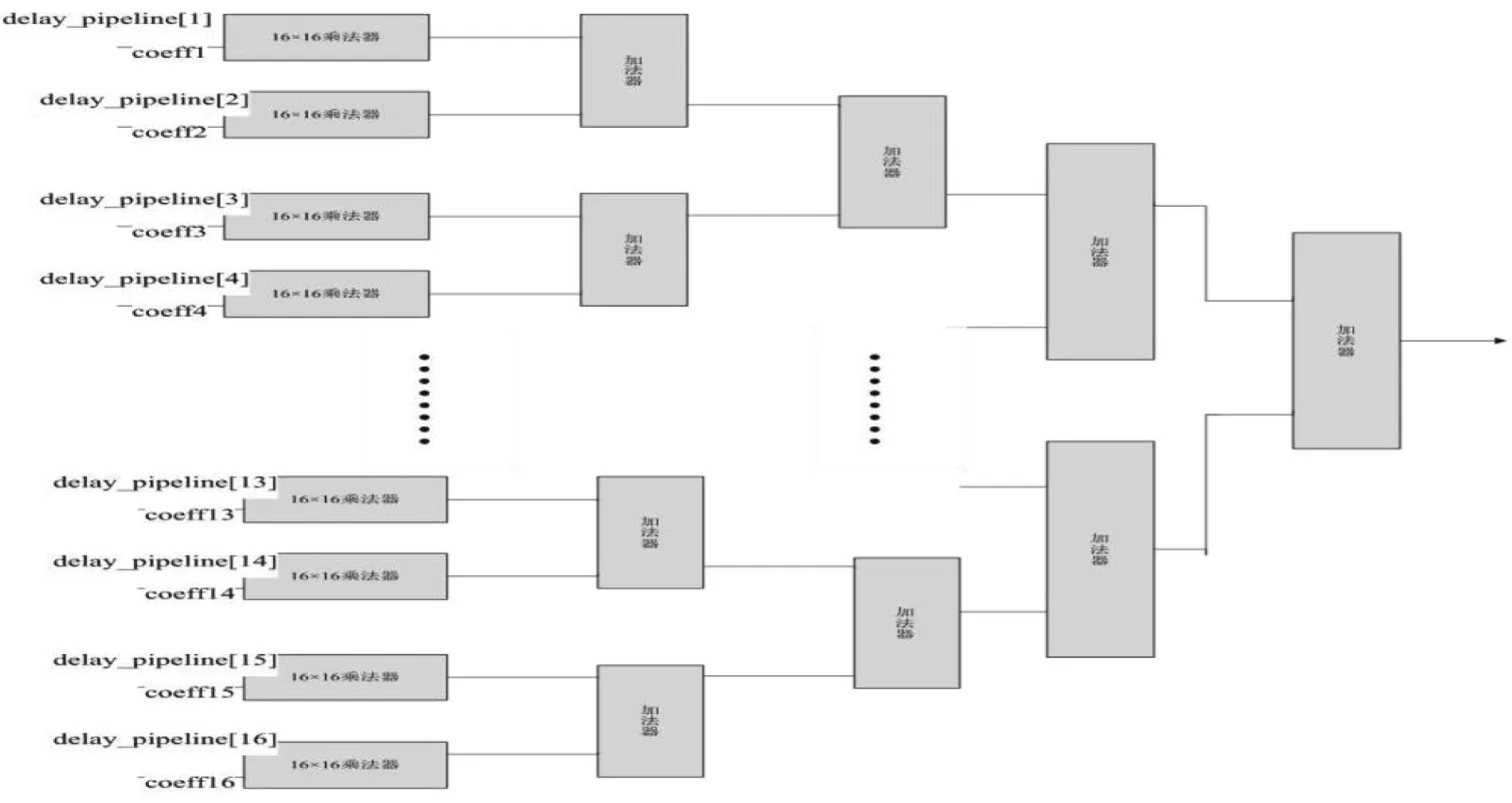

因为卷积运算与加乘运算间的换算关系,可以将滤波功能用加乘模块具体实现。在QuartusⅡ软件中,针对各加乘模块单元进行VHDL编程编译后,生成相应的符号文件。最后连接成顶层原理图。整个电路的原理设置方案如图3所示。

图2 Matlab设计工具FDAtool的设计界面

2 验证

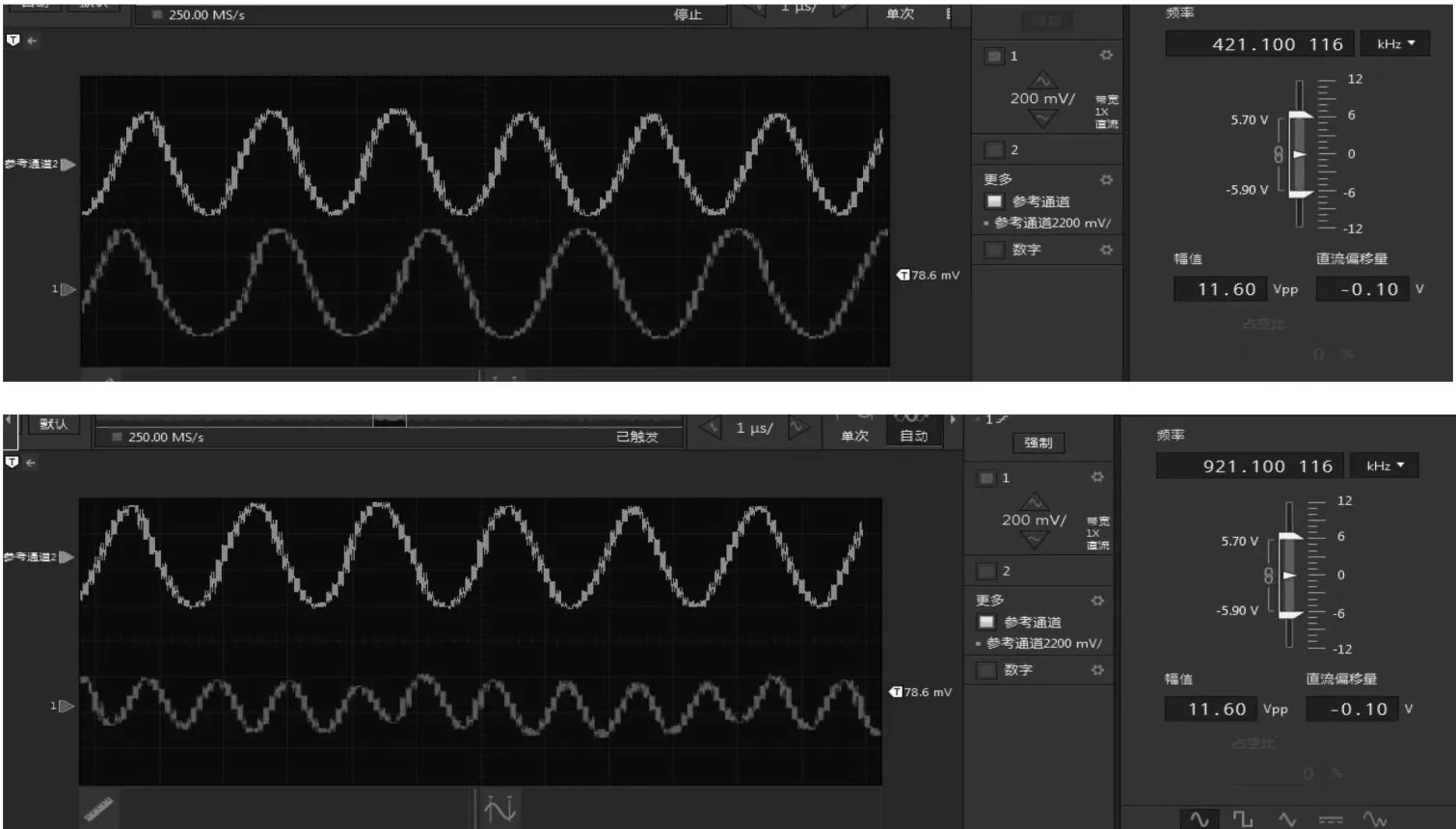

对于滤波器滤波性能的验证方法,本文采用是输入频率计一定幅值的频率信号,并逐渐增大输入信号频率,观察随着信号频率的增大,在跨越截止频率之后信号幅值是否有大幅度衰减。由于所设计的滤波器的通带截止频率是625 kHz,阻带截止频率是1 250 kHz,可以从如图4所示的验证结果中看出当输入信号的频率为421 kHz时,信号滤波的结果几乎与原信号相同,但当信号频率增加为921 kHz时,可明显观察出滤波后的信号幅值被衰减。

图3 FIR滤波器整体设计方案原理

图4 滤波效果

3 结语

FIR滤波器是最常见、使用也最为广泛的一类滤波器。本文首先简单介绍滤波器目前常用的设计方法,然后在此基础上介绍了滤波器的直接型结构、窗函数设计法等,并且利用Matlab软件设计符合要求的16阶滤波器的抽头系数,最后用VHDL语言进行编程,并在QuartusⅡ软件上进行编译仿真,最终在FPGA器件上下载验证滤波效果,从验证结果来看,该FIR滤波器的实现方案,具有工作速度快、实时信号好等特点,能够满足实际数字系统的要求。

[1] 赵颖,刘祖深,李胜寅.基于MATLAB的FIR数字滤波器的方法设计[J].国外电子测量技术,2012(10):35-37.

[2] 马月红,马彦恒,王雪飞.基于MATLAB的FIR数字滤波器设计与仿真[J].电子测量技术,2010(11):66-69.

[3] 孙耀奇,高火涛,熊超,等.基于Matlab和FPGA的FIR数字滤波器设计及实现[J].现代电子技术,2008(11):89-92.

[4] 张猛.基于Matlab的FIR数字滤波器设计[J].长春大学学报,2009(2):47-49.

Realization of high-order low-pass FIR filter by Matlab and FPGA

Gu Mengqi

(Physics and Electronic Electrical Engineering School, Huaiyin Normal University, Huai’an 223300, China)

Filter is signal processing tools that electronic professional commonly use and is electrical components to reduce or eliminate interference. Based on the top-down hierarchical design idea developed by FPGA, the 16th-order low-pass filter is realized and designed by Matlab and QuartusⅡ software, the simulation and the real test results show that the low-pass filter performance is achieved. Compared with the traditional digital filter, FPGA device superior performance makes the design of the filter better real-time, portability and so on.

MATLAB; FPGA; filter; simulation

顾梦祺(1987— ),女,江苏徐州人,助理实验师,硕士;研究方向:复杂动态网络同步控制,电子产品开发。