基于MIPI标准下的D-PHY的设计与验证

,,,

(1.上海大学 机电工程与自动化学院,上海 200072; 2.上海市电站 自动化技术重点实验室,上海 200072;3.上海大学 微电子研究与开发中心,上海 200072)

基于MIPI标准下的D-PHY的设计与验证

承文龙1,3,胡越黎1,2,3,杨晔晨3,胡云生3

(1.上海大学机电工程与自动化学院,上海200072; 2.上海市电站自动化技术重点实验室,上海200072;3.上海大学微电子研究与开发中心,上海200072)

目前大部分移动设备均使用MIPI接口,主要是MIPI接口可以实现高速数据传输,同时不会造成功耗的损失过大的功能;为了理解MIPI接口的工作原理,通过对MIPI接口中物理层的设计和研究;阐述MIPI接口实现低功耗模式和高速传输数据模式的本质原理;对MIPI接口物理层的设计,采用40 nm的CMOS工艺,实现以500 MHz的速率来传输数据,功耗损失仅在0.74 mW左右。

移动产业处理器接口;物理层;高速模式;低功耗模式

0 引言

随着信息技术的飞速发展,越来越多的智能便携式设备走入人们的生活。人们对于移动设备设计要求越来越高,不仅要满足高性能显示效果的追求,同时也要极大的减少移动设备的功耗损失。因此,在2003年由ARM,Nokia,ST,TI等公司成立MIPI联盟,把手机内部的多个接口标准化,减少设计的复杂程度和增加设计灵活性。MIPI不仅是一个联盟也是一套接口协议规范的名称,它下面有不同的工作组,以满足移动终端各个子系统的不同需求,比如摄像头接口CSI、显示接口DSI、射频接口Dig RF、麦克风/喇叭接口SLIM bus等[1-2]。而对应的物理层也是MIPI设计的最重要的模块,其决定MIPI接口能否实现高速数据传输和低功耗命令传输的电气特性。

目前,大部分MIPI接口的使用者,只知道MIPI接口包含高速传输和低功耗传输的功能,而没有理解MIPI接口如何实现数据传输的原理和内部电路,同时国内也很少有相关的文献详细介绍MIPI接口中物理层的概念和原理。目前,主要应用的物理层有C-PHY,D-PHY和M-PHY,而D-PHY是应用最广泛的物理层。所以,本文根据通过对D-PHY的设计和仿真验证,详细阐述物理层的工作原理和电路结构。

1 MIPI D-PHY基本原理介绍

1.1 MIPI D-PHY之间的通信

目前,MIPI主要有两种类别,一种是基于DSI协议用于实现主处理器与显示器件交互,多用于移动设备的显示接口[3-4];一种是基于CSI协议用于实现主处理器与摄像器件交互,多用于移动设备的摄像接口[5]。MIPI-DSI和MIPI-CSI都可以共享同一个D-PHY,即它们的物理层是相同的。通常,D-PHY采用一对源同步的时钟和一到四对差分时钟数据线来进行数据传输,对应的时钟通道是单向的,数据通道是单向或者双向的,命令传递控制双向通道的传输方向。如图1是MIPI接口的物理连接图,其主机和从机通过彼此的物理层相互连接,CLK为时钟传输通道,以DDR的方式进行时钟的控制,Data0~Data3为数据传输通道,当每条通道设置为高速传输模式时,传输速率可达80 Mbps到1 000 Mbps之间,但实际应用中存在各种外在限制,通常运行速率在500 Mbps左右,用于传输有效数据。当每条通道为低功耗传输模式时,最大传输速率仅为10 Mbps左右,用于传输控制命令。D-PHY工作时,最多可以有4个通道同时进行传输,可以实现4倍的速率进行数据和命令的传输。通过时钟通道和数据通道,可以实现主机和从机之间的数据和命令的交互,传递有效信息。同时,主机和从机都可以作为数据发送端或接受端,但时钟信号只能由主机提供给从机。

1.2 MIPI D-PHY的电气特性

由图1可知,物理层与物理层之间的数据传输是利用数据通道进行,而数据通道中数据传输仅由两根数据线控制。一般定义Dp和Dn构成数据通道的两根数据线,Dp和Dn数据线上可以传输不同的电气特性。由于MIPI接口包含两种传输模式,对于不同的传输模式,传输的高低电平的定义也不同。见表1所示,在低功耗传输模式下,根据数据通道的Dp和Dn数据线中输出电平组合不同,可以分为4种输出格式LP-00,LP-01,LP-10,LP-11,而4种不同的输出格式也表示不同的指令模式或工作状态,控制D-PHY运行的工作状态。对比低功耗模式,高速模式利用Dp和Dn数据线中输出电平进行差分处理,产生只有两种输出格式HS-0和HS-1。当Dp数据线为逻辑高电平,Dn数据线为逻辑低电平时,代表输出格式为高速传输的逻辑高电平;当Dp数据线为逻辑低电平,Dn数据线为逻辑高电平时,代表输出格式为高速传输的逻辑低电平。因此,高速模式下的逻辑“1”和逻辑“0”就可以代表数据传输的逻辑电平,避免出现逻辑混乱的问题。一般情况下,低功耗模式的工作电压大约在0 V到1.2 V之间波动;而高速模式的工作电压大约在100~300 mV之间波动。

表1 D-PHY通道状态表

图1 DSI/CSI物理连接图

1.3 MIPI D-PHY通道的工作原理

目前,D-PHY支持两种传输模式,高速传输模式和低功耗传输模式,两种模式共同工作,实现MIPI接口的协议层中的数据和命令的传输。当D-PHY工作在高速传输模式时,主要实现有效像素数据的传输;当D-PHY工作在低功耗传输模式时,主要实现控制信号或命令的传输。通过高速传输和低功耗传输之间的合理切换,可以实现高速传输数据的同时减少功耗的损失。通常,D-PHY数据通道包含3种操作模式,分别是逃离模式,高速模式以及控制模式,而从控制模式的停止状态开始可能发生的事件有多种。如图2所示,D-PHY中一个最基本的高速模式状态图,工作的状态主要由Init state,STOP,HS-Rqst,HS-Prpr,SOT,HS-Deskew,EOT七个状态构成。首先,Init state表示D-PHY模块通道的最初始状态;状态STOP,HS-Rqst,HS-Prpr是D-PHY模块工作在低功耗模式下的状态,主要负责传输不同的命令,进行控制状态的转换;状态SOT和EOT是D-PHY工作在低功耗模式下的状态,主要负责给有效数据包添加包头和包尾序列。状态HS-Deskew是D-PHY工作在高速传输模式下的状态,主要负责传输有效的数据包。当SOT接收到00011101指令后,数据通道进入高速有效数据传输阶段HS-Deskew,HS-Deskew阶段的有效数据传输结束后,EOT接收到00指令后,数据通道进入STOP状态等待,指示一次基本完整的数据传输结束。

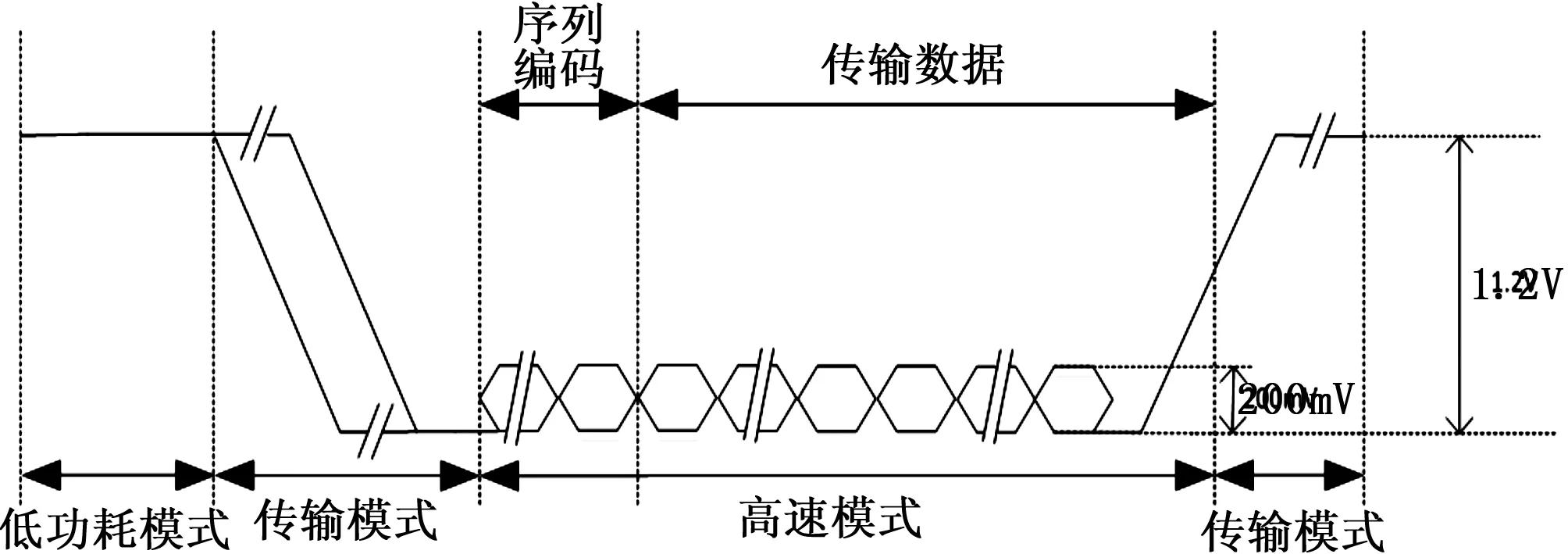

根据图2的D-PHY工作状态的表述,D-PHY中一个完整的数据传输需要高速传输模式和低功耗传输模式相互配合构成。在传输开始阶段D-PHY处于初始状态,即工作在低功耗模式下,当连续接收到低功耗模式下的传输命令LP-11-gt;LP-01-gt;LP-00序列指示后,数据传输模式进入高速数据传输模式。在高速传输模式中,需要给有效的传输数据进行打包处理,在有效数据的开始位置和结束位置添加规定序列SOT和EOT,隔离有效数据和命令序列,减少彼此之间的干扰,避免影响最终传输数据的正确性。在数据传输结束时,接收到低功耗传输命令LP-gt;11序列指示后,数据传输离开高速数据传输模式进入默认状态的低功耗模式。如图3 是D-PHY传输原理图,显示了D-PHY模块实现一次完整的数据传输的波形图。

图2 D-PHY高速模式状态图

图3 D-PHY传输原理图

2 MIPI D-PHY模块设计

2.1 D-PHY通道模块设计

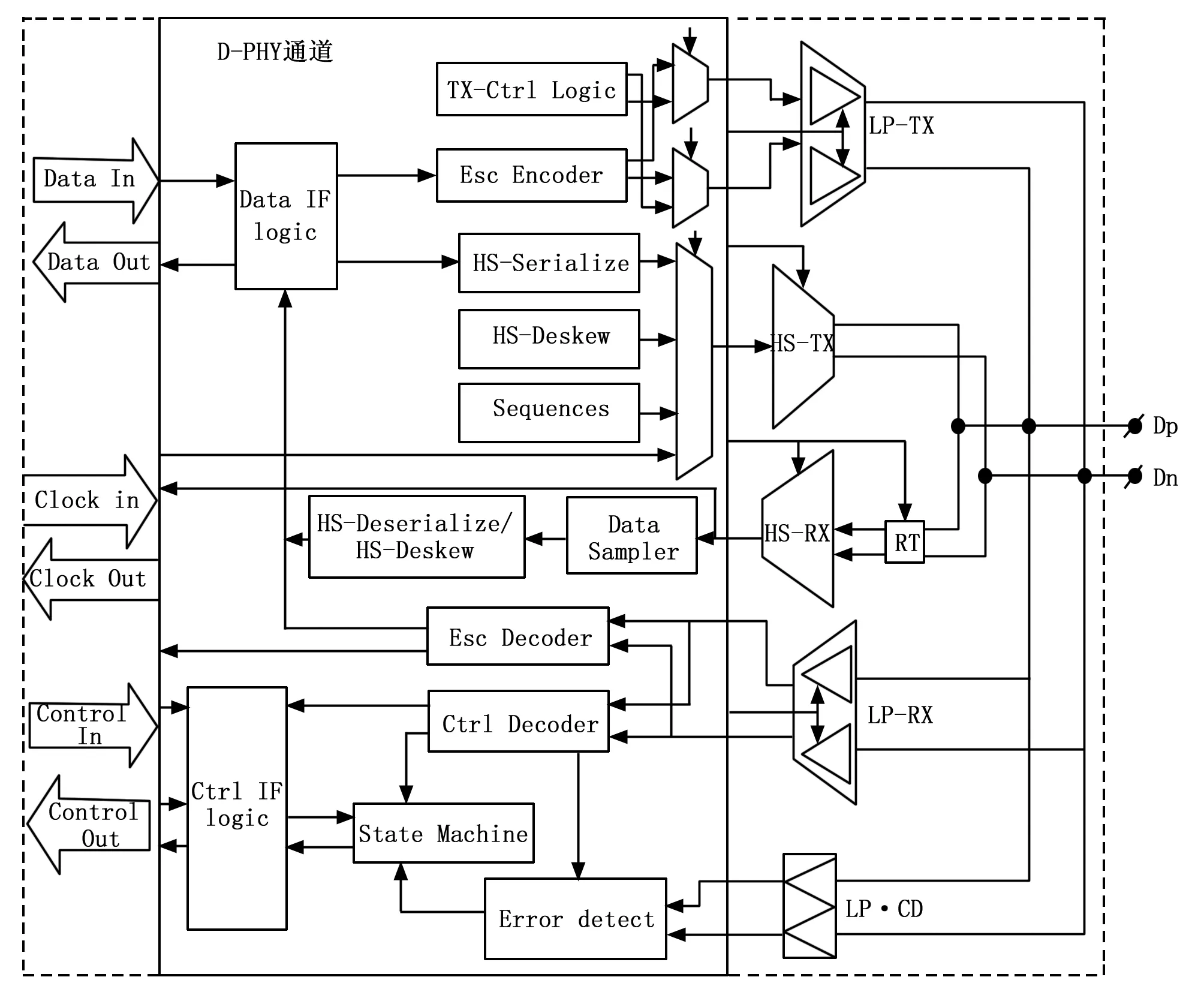

MIPI D-PHY主要由各个通道模块组成,如时钟通道或数据通道,每个通道的传输是遵循串行传输原理,而通道间传输是遵循并行传输原理,不同通道之间彼此独立运行,不会出现相互干扰和影响。如图4所示,一个完整的通道模块主要由两大模块组成,数字模块和模拟模块。对于模拟模块,主要是接收和发送数据到数字模块,利用低压差分电路HS-TX和HS-RX,实现数据的高速发送和接收,利用低功耗传输电路LP-TX和LP-RX,实现控制命令的发送和接收以及控制通道的工作状态和数据传输方向,利用低功耗冲突检测器电路LP-CD,避免低功耗传输模式下,由于传输通道双向性可能会引起的传输冲突现象[6]。数据线Dp和Dn是物理层通道的输出端口,用于物理层与物理层的数据传输,也是主机和从机信息交互的唯一端口,即可传输高速数据也可传输低功耗命令,但不能两种模式同时传输,只能交替传输。因此,物理层中的模拟模块是实现物理层和物理层之间数据传输的重要环节。而物理层数字模块由多个子模块组成,一部分数字模块中的子模块可以接收来自协议层的数据包,并对接收的数据包进行再处理,对传输低功耗命令数据包进行编码,对传输高速有效数据包进行并行转串行操作,转换成能被物理层中模拟电路可以接收处理的格式。一部分数字模块的子模块可以处理来自物理层模拟模块传输的数据,对接收的低功耗命令数据进行解码,对传输高速有效数据进行串行转并行操作,转换成可以被上层协议层接收处理的格式。另一部分数字模块的子模块是对低功耗模式下的命令传输过程出现的错误进行检测,避免传输通道双向性引起的传输冲突问题[7]。因此,D-PHY中的数字模块主要功能就是对传输的数据格式进行处理,解决数据在不同层传输过程中,出现数据格式不匹配问题。

2.2 D-PHY中模拟模块的设计

由图4可知,MIPI D-PHY通道模块中的模拟模块分为高速传输模式的电路和低功耗传输模式的电路。如图5所示,根据两种不同的工作模式,物理层中模拟模块的电路分为两种模式的电路设计,对应的规定正常传输时的有效电平也分为两类,一类是差分的小摆幅电平,用于高速数据传输,另一类是低速的满摆幅电平,用于低功耗数据传输。MIPI的高速数据传输原理与LVDS原理很像,属于低压差分电路,输出结果是由数据线Dp和Dn共同控制,所以电路具有高速、差分、低摆幅特点,这些特点有利于抗EMI干扰和降低功耗,适用于大数据量图像的突发连续传输[8]。在高速差分数据传输时的共模电平在200 mV左右,电压摆幅为100~300 mV之间,数据传输速率为80~1 000 Mbps之间。对应的低功耗传输也可视为低速传输,属于单端输出电路,可以进行读写寄存器等短时间、小数据量操作,使电路在较低的功耗水平运行,一般工作电压从0~1.2 V,最大数据传输速率为10 Mbps。在低功耗传输时,电压摆幅在1.2 V左右,传输速率为10 MHz,而在高速传输时,电压摆幅为200 mV,传输速率可达500 MHz。因此,对于有效的像素数据利用高速传输,对于控制命令利用低功耗传输,这样可实现高速传输数据的同时,减小不必要的功耗损失[9]。

图4 MIPI D-PHY通道模块原理图

3 实验结果分析

3.1 验证平台搭建

本文以Verilog HDL硬件语言为基础,设计D-PHY模块做为验证模块,搭建合理的测试平台,利用Mentor公司的Modelsim进行软件仿真,对设计模块做功能和动态时序的验证,根据需求添加需要的端口进行波形观察。当软件仿真满足要求后,在利用Lattice公司的CrossLink FPGA进行板级的验证,并通过特定的示波器进行波形观察[10-12]。

3.2 软件验证结果分析

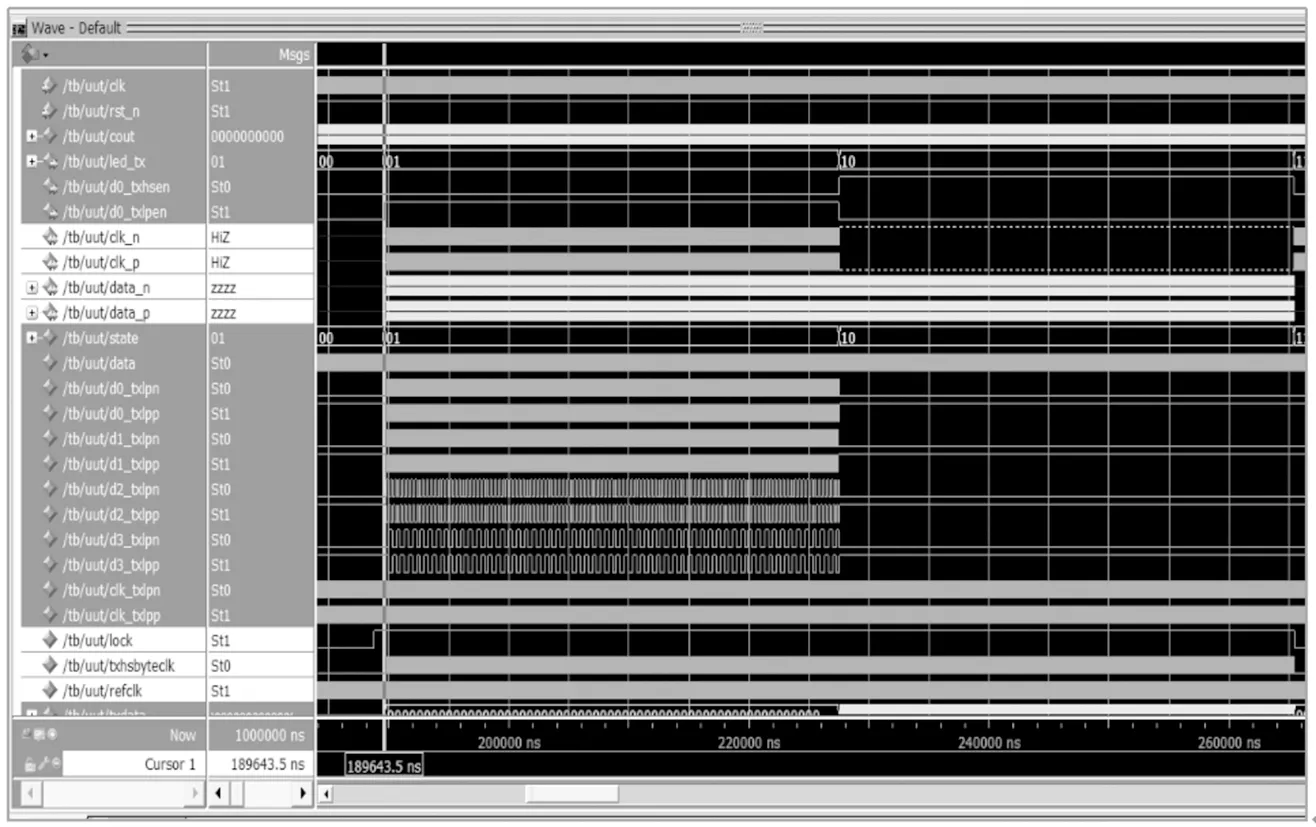

使用Modelsim对D-PHY设计模块进行功能仿真。如图5所示,设置state表示D-PHY工作状态,当state=01表示低功耗数据传输波形,state=10表示高速数据传输波形,state=00和state=11表示其他空闲状态,可以不予考虑。clk_n和clk_p是时钟通道的数据线,用于物理层时钟的传输,data_n和data_p是数据通道的数据线,用于物理层数据的传输。可以发现在state=10时,高速数据传输的时钟频率无法达到要求,所以有效数据无法正常传输。

由图5可知,使用Modelsim软件仿真所得结果与预期结果一样,唯一不足是高速传输无法显示波形。由于高速传输的电压摆幅是200 mV左右,在Modelsim软件仿真中很难显示高速模式下的数据传输波形。

图5 高速传输块和低功耗传输电路

3.3 硬件验证结果分析

所以,对于高速模式的传输测试,需要利用特定的示波器才能仿真出相应的结果。根据不足,本文利用特定的示波器对MIPI D-PHY设计进行高速数据采集的观察。当D-PHY模块设计在Modelsim中满足功能验证后,利用FPGA的灵活性,将设计好的模块,配合Lattice的Diamond软件,将设计模块烧写到CrossLink FPGA中。在进行板级调试时,通过引线引出对应的Dp和Dn端口,连接到特定的示波器上,通过调节示波器的电压摆幅,工作频率和工作通道,直到出现预期波形。如图6、7所示,示波器的波形分别由CH1通道和CH2通道输出,CH1通道的黄色波形为Dp端口的输出波形,CH2通道的蓝色波形为Dn端口的输出波形,通过示波器可以看出CH1和CH2通道的单位电压是100 mV,所以高速输出波形的电压摆幅符合预期要求。对于高速模式的传输就是利用Dp和Dn端口的电压进行差分传输,当Dp端电压大于Dn端电压时,输出为逻辑高电平;当Dn端电压大于Dp端电压时,输出为逻辑低电平。

图6 D-PHY软件仿真图

图7 D-PHY示波器仿真图

4 结论

本文MIPI D-PHY的设计支持高速模式和低功耗模式,符合MIPI芯片的标准,设计采用40 nm的CMOS工艺制造,在高速传输下,速度达到400 MHz~500 MHz之间,所消耗功耗在0.52 mW~0.74 mW之间。通过本文阐述,体现出MIPI在移动设备的独特性和重要性,不仅满足高性能的传输效果,同时可以极大的减少移动设备的功耗。

[1] MIPI Alliance Specification for D-PHY version 1.00.00[S]. MIPI Alliance, 2009.

[2] Lawrence R, Richard. High-speed serial interface for mobile displays[Z]. IDW, 2006:2013-2016,

[3] MIPI Alliance Specification for Display Serial Interface version 1.01.00[S]. MIPI Alliance, 2008.

[4] Kyusam Lim, Gye Su Kim, Suki Kim, Senior Member. A Multi-Lane MIPI CSI Receiver for Mobile Camera Applications[Z]. IEEE Consumer Electronics Society, 2010:1185-1190 .

[5] Yueh-Chuan Lu, Zong-Yi Chen, Pao-Chi Chang. Low power multi-lane MIPI CSI-2 receiver design and hardware implementations[A]. International Symposium on Consumer Electronics (ISCE)[C]. 2013:199-200.

[6] MIPI Alliance Standard for Display Serial Interface V1.0[S]. MIPI Alliance, 2006.

[7] Beom-Dam Kim, Sang-Jin Lee. Design of a D-PHY Chip for Mobile Display Interface Supporting MIPI Standard[A]. IEEE International Conference on Consumer Electronics (ICCE)[C]. 2012:660-661.

[8] 董春雷,王康平,陈 威. LVDS技术在LCD数据传输中的应用[J].电子技术, 2011,(2):48-49.

[9] W Wei, FT Zhang. The Analysis of the Transmission Signal Measured MIPI D-PHY[J]. Advanced Materials Research, 2014,(7):986-987.

[10] 胡越黎, 周 谌. 基于IP复用的片上级系统的构建与验证[J]. 计算机测量与控制, 2010,25(3):629-631.

[11] 曹 阳,胡越黎. 基于UVM的存储控制器功能验证[J]. 计算机测量与控制, 2015,25(3):834-837.

[12] 虞 超,胡越黎,王龙杰,等. 基于MV10微处理器的在线编程IP核设计与验证[J]. 电子技术应用, 2012,8(6):126-128.

DesignandVerificationofD-PHYBasedonMIPIStandard

Cheng Wenlong1,3,Hu Yueli1,2,3,Yan Yechen3,Hu Yunsheng3

(1. College of Mechatronic Engineering and Automation, Shanghai University, Shanghai 200072, China; 2. Shanghai Key Laboratory of Power Station Automation Technology, Shanghai 200072, China; 3. Microelectronics Research and Development Center, Shanghai University, Shanghai 200072, China)

Most mobile devices use MIPI interface at present, MIPI interface can realize high speed data transmission, and will not cause high power consumption. In order to understand the working principle of the MIPI interface, through the design and research of physical layer in MIPI interface. MIPI supports low-power mode and high-speed data transmission mode. The design of MIPI interface physical layer using 40nm CMOS process, and can realize transmitting data at a rate of about 500 MHz. The power consumption of transmitting data is only about 0.74 mW.

mobile industry processor interface; physical layer; high speed mode; low power mode

2017-02-27;

2017-03-31。

承文龙(1993-),男,安徽安庆人,硕士研究生,主要从事芯片设计和验证方向的研究。

胡越黎(1959-),男,上海人,工学博士,教授,博士生导师,主要从事图像处理、机器视觉、片上系统、芯片设计方向的研究。

1671-4598(2017)09-0295-03

10.16526/j.cnki.11-4762/tp.2017.09.075

TP273

A