FT1500A主板上电时序控制的设计与实现

马 强,李竞航,王建民,杨少英

(1. 华北计算机系统工程研究所,北京 100083; 2. 六所智达(北京)科技有限公司,北京 100083)

FT1500A主板上电时序控制的设计与实现

马 强1,李竞航2,王建民1,杨少英1

(1. 华北计算机系统工程研究所,北京100083;2. 六所智达(北京)科技有限公司,北京100083)

研究了一种基于国产处理器FT1500A的主板的上电时序控制方法。硬件部分采用Altera可编程逻辑控制器EPM240作为控制单元,采用电源模块LTM4627实现电源的使能控制与稳定检测;软件部分在Quartus平台上使用VHDL语言,利用统计可编程逻辑控制器的时钟脉冲的方式实现了延时控制,利用控制器内部的逻辑单元实现了电源模块的使能控制。最后利用示波器的单次触发功能验证了设计的正确性和可靠性。

主板上电时序;FT1500A;可编程逻辑控制器;VHDL语言

0 引言

在板卡的上电过程中,当在开启电源后,电压的上升是一个连续的过程,所有芯片必然不能同时瞬间拥有所需的工作电压,而芯片的工作又存在先后顺序,所以必须人为地对电源信号发生的顺序加以控制,使板卡上的芯片依次上电,这就是板卡的上电时序控制[1]。芯片FT1500A是2015年由中国电子新推出的一款高性能国产中央处理器 (Central Processing Unit, CPU),FT-1500A系列处理器是64位通用CPU,具有高性能、低功耗等特点,关键技术在国内处于领先水平。其主板研发是一个崭新的课题,因为主板上的所有元器件均为国产,包括核心CPU,所以国际上无人涉足,在国内也无先例。FT1500A主板的时序控制方法与Intel架构的CPU主板不能同等处理。

1 FT1500A上电时序分析

本课题所设计的FT1500A主板采用的是新主板架构ATX(AT Extended)标准电源,其中关键的控制管脚PS_ON#信号为低电平有效,控制所有主电源开启关闭,需上拉到5 V。5VSB为独立电源,为软电压控制提供电源,powered-down(PS_ON#为高,主电源关断)状态下也有效。PWR_OK信号是+5 V和+3 V电源就绪标志,就绪时拉高,电压不足或断电时拉低。12 V电源插座要紧挨稳压器,保证电源的干净。

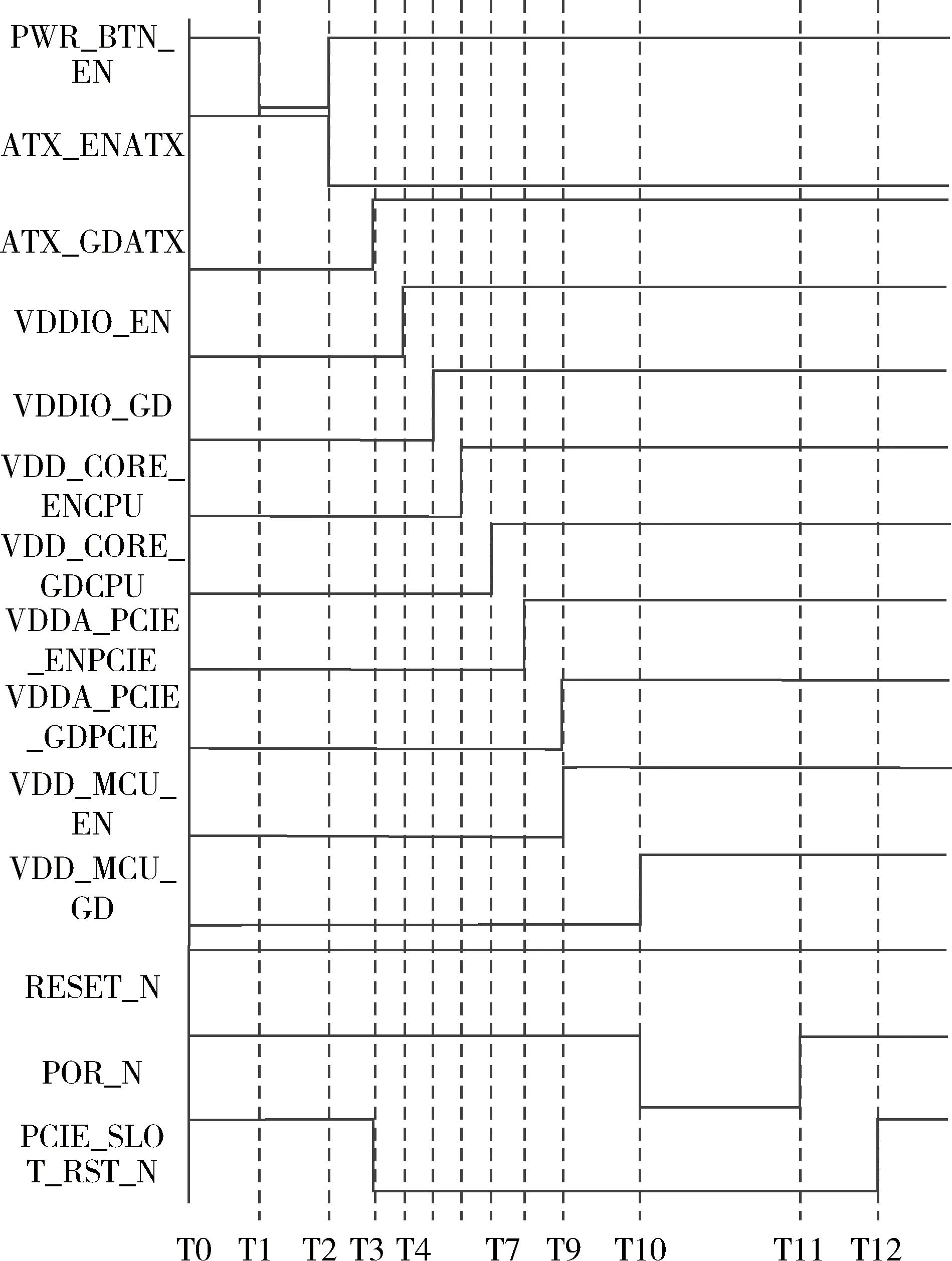

FT1500A对上电时序的要求规定如图1所示,其中PWR_BTN_EN是上电按钮,低电平有效;ATX_ENATX是电源加电信号,低有效;RESET_N是热复位信号,低有效;POR_N是上电复位信号,低有效;PCIE_SLOT_RST_N是所有的总线和接口标准(Peripheral Component Interface Express, PCIE)插槽端的复位信号,信号数目根据PCIE设备而定。

图1 上电时序图

FT1500A对主板上各个模块的上电时序的具体要求如下,T0:作为上电复位控制器的CPLD或FPGA加电并完成复位;T1:加电按钮按下;T2:加电按钮弹起,ATX电源加电;T3:收到ATX加电完成信号,拉低PCIE_SLOT_RST;T4:相对T3时刻约延时约20 ms,给1.8 V IO电源加电;T5:收到加电完成信号;T6:相对T5时刻延时20 ms,VDD_CORE电源上电;T7:收到上电完成信号;T8:相对T7时刻延时10 ms,给PCIE0.95V核心电源加电;T9:收到PCIE0.95V上电完成信号,给VDDQ_MCU1.5V电源加电;T10:收到上电完成信号,保持REST_N信号高电平,拉低POR_N开始上电复位;T11:相对T9时刻延时40 ms,拉高POR_N,完成上电复位;T12:相对于T9时刻延时100 ms,拉高PCIE_SLOT_RST_N,完成PCIE设备复位。

2 硬件电路设计与实现

想要得到可控的上电时序,就需要选择带有使能功能的电源控制芯片。为了得到质量较好的电源,选用Linear公司的高品质的DC-DC线性电源模块LTM4627。其最大工作电流可以达到15A,具有宽输入电压范围4.5 V~20 V,输出电压范围0.6 V~5 V,可以由外部电阻控制;电源效率最多可达93%,采用LGA封装15 mm×15 mm×4.32 mm,较小的封装有利于增大电路设计空间,且输出误差不超过1.5%。LTM4627设计成本较低,只需要极少的外部电路配置就可以实现稳定可靠的直流电源[2]。

这里只列出CPU核心电源FTCORE的设计过程,如图2所示,利用LTM4627将5 V的输入电压VCC5转化为0.9 V的输出电压VCC_FTCORE,为CPU内核供电。FTCORE_RUN是上电控制信号,FTCORE_PGOOD2是上电完成信号。上电阶段,按照系统时序控制程序,控制器将FTCORE_RUN拉高,LTM4627开始工作,数毫秒后,LTM4627自检VCC_FTCORE稳定到0.9 V后拉高FTCORE_PGOOD2,告诉控制器自己上电完毕,系统继续进行下一步时序流程。

图2 CPU核心电源VCC_FTCORE电路实现

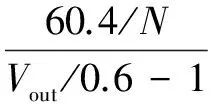

根据芯片手册,输出电压仅由F12脚的下拉电压决定,其公式为:

(1)

其中,N为LTM4627芯片的数量,在本项目中N的取值为4。对于0.9 V的VCC_FTCORE,计算可得出其配置电阻=30.2 kΩ。考虑到不存在30.2 kΩ的电阻,为了输出精确的0.9 V电压,此处电阻精度要求较高,绝对不能以相近的电阻代替,所以采用两个电阻串联的方法,配置出所需的30.2 kΩ阻值。查阅阻值表,确定了两个阻值分别为30.1 kΩ和100 kΩ。

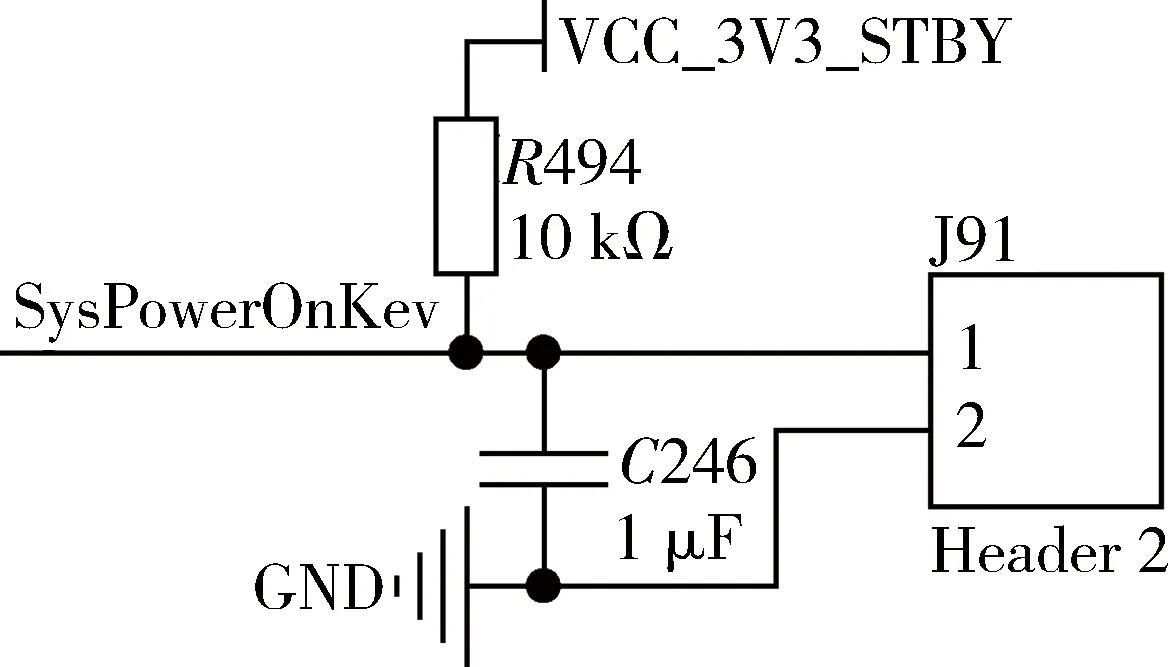

图3是主板开机按钮接口的电路设计,实际应用中将J91接到一个按键开关上,图中电容非常重要,其作用是电路防抖动,没有电容器的存在,电路极易在受到电磁干扰的情况下发生误动作。当开关按下,SysPowerOnKey即被拉低,系统收到开机的命令,开始按照时序控制程序启动各个电源。复位按键的电路设计与图3相似。

图3 开机按钮接口电路

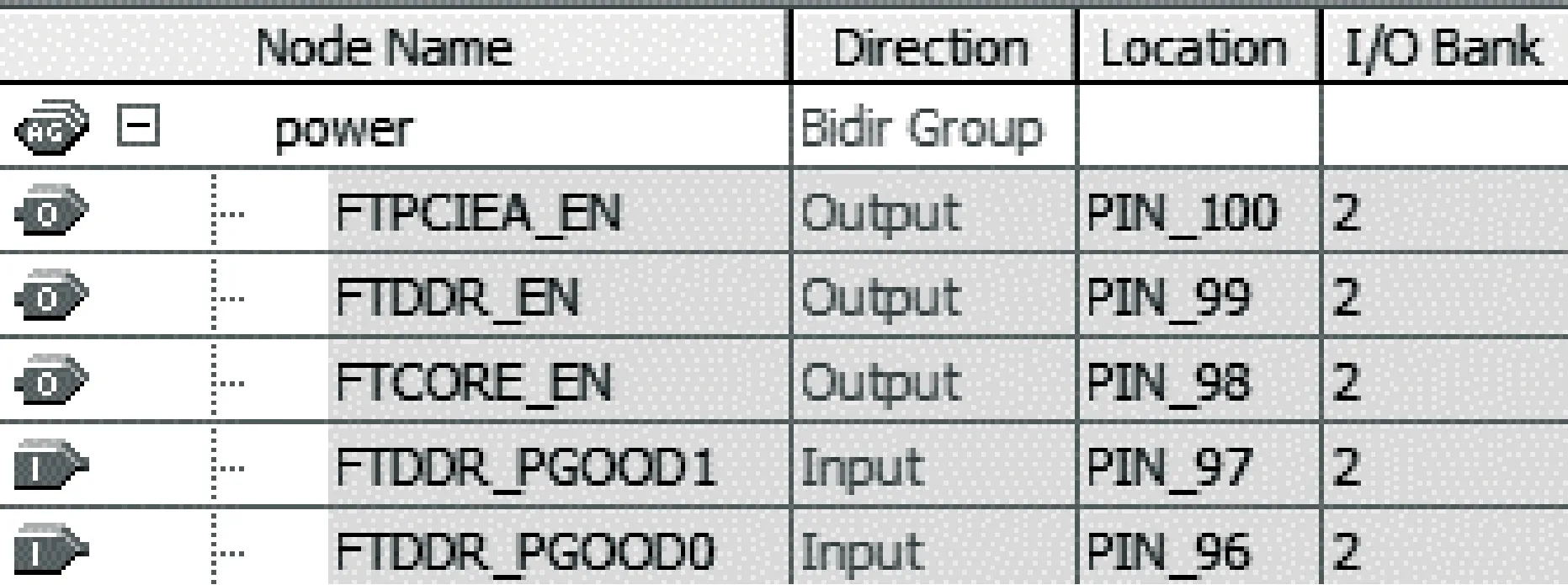

由于需要控制的时序关系比较复杂,外围简单的逻辑电路不能很好地实现,因此考虑使用可编程逻辑控制器CPLD,可以很方便地实现时序控制,同时为主板其他功能提供控制资源。CPLD是一种多输入多输出的逻辑控制器件,利用内部的逻辑单元,通过简单的编程,就能实现信号的顺序控制和延迟控制[3]。本课题选择Altera公司的EPM240作为控制模块的主控芯片,其频率为201.1 MHz,电源电压范围为2.375 V~2.625 V,3 V~3.6 V ,工作温度范围为0℃~+85℃,输入/输出接口标准为LVTTL, LVCMOS, PCI。EPM240包含100个管脚,其中可用的I/O资源多达80个,基本可以满足所有的时序控制需求以及所有的主板电路控制需求[4]。 本课题控制信号统一使用TTL电平,确定CPLD Bank2供电电压为3.3 V。在Quartus中,将需要控制的信号分配到CPLD的各个I/O中,部分I/O分配如图4所示,最后在电路原理图中,将信号对应地连接起来。CPLD具有足够的I/O资源,且设计难度较低,这是它的优势。采用的烧写器是USB Blaster Rev.C,JTAG模式定义:1-TCK; 2-GND; 3-TDO; 4-VCC; 5-TMS; 6-NC; 7-NC; 8-NC; 9-TDI; 10-GND。

图4 CPLD的部分引脚分配

3 软件实现

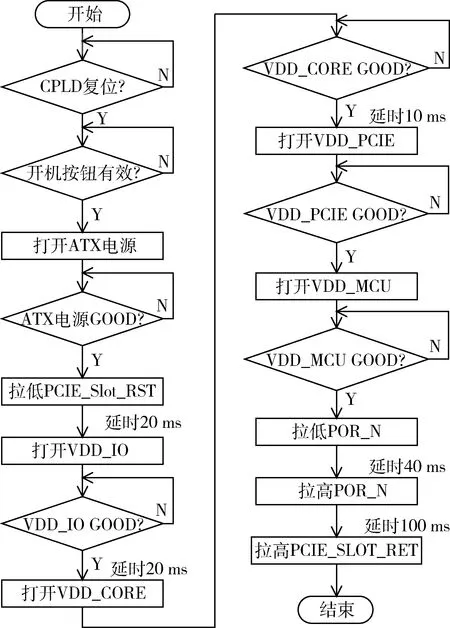

软件部分利用Quartus平台实现,采用的编程语言是VHDL。编程思想是,为了节约系统的计算资源,没有使用计时器和计数器寄存器,而是选择一种以CPLD的时钟作为计时工具,在上一个动作之后,等待相应的时钟数,也就是某个特定的时长,再开启下一个电压,继续重复等待并使能,依次打开主板各部分的电源。根据 FT1500A对时序的要求,设计出CPLD上电时序控制程序流程如图5所示。

图5 CPLD上电时序控制程序流程图

3.1延时的实现

利用统计系统时钟脉冲次数的方法实现计时。CPLD时钟CLK=50 MHz。定义变量sgPowerSeqCounter作为计数器,从检测到电源按键按下起,每次时钟周期自加1,50k个时钟周期即为1 ms。但是开机的时长不能超过3 min,否则视为开机故障。

if sgPowerSeqFlag='1' and SysPowerOnKey = '1' then

sgPowerSeqCounterlt;=sgPowerSeqCounter+1;

if sgPowerSeqCountergt;Xquot;9F437C6quot;then

sgPowerSeqCounterlt;=Xquot;9F437C6quot;;

end if;

end if;

3.2检测电源按键状态

开机是按下50 ms以上,一直等待按键抬起才开机。同样利用变量sgPowOnCounter采集电源按键被按下的时间,这是为了防止按键抖动,如果此时间小于10 ms,则可以认为不是按键动作,视为无效。

if sgKeyState=′1′ and SysPowerOnKey=′0′ and sgKeyFlag=′0′ then

sgPowOnCounterlt;=sgPowOnCounter+1;

if sgPowOnCountergt;500000 and sgKeyFlag =′0′ then

sgKeyFlaglt;=′1′;

end if;

if sgPowOnCountergt;Xquot;8000000quot; then

sgPowOnCounterlt;=Xquot;8000000quot; ;

end if;

end if;

if sgKeyState =′0′and SysPowerOnKey=′1′ and sgPowOnCounterlt;500001 then

sgKeyFlaglt;=′0′;

sgPowOnCounterlt;=Xquot;0000000quot;;

end if;

3.3时序控制部分

当各种检测完成,确定开机状态后,控制电路按照FT1500A规定的时序依次上电。

if sgPowOnCmd=quot;11quot; then

sgPowerSeqFlaglt;=′1′;

if sgPowerSeqCounter=5 then

SysPowerOn3V3lt;=′0′; --打开 ATX power

FTPCIE_ResetSlotlt;=′0′; --拉低PCIE_Slot_RST

FTGN12_RSTlt;=′0′;

end if;

if sgPowerSeqCounter=02500000 then

FTIO_ENlt;=′1′ ; --打开VDD_IO

end if;

if sgPowerSeqCounter=05000000 then

FTCORE_ENlt;=′1′;--打开VDD_CORE

end if;

if sgPowerSeqCounter=07500000 then

FTPCIEA_ENlt;=′1′; -- 打开VDD_PCIE

end if;

if sgPowerSeqCounter=10000000 then

FTDDR_ENlt;=′1′ ; --打开VDD_MCU

end if;

if sgPowerSeqCounter= 11500000 then

FT_PORNlt;=′0′; --拉低POR_N

end if;

if sgPowerSeqCounter=12500000 then

FT_PORNlt;=′1′;--拉高POR_N

FTGN12_RSTlt;=′1′;

end if;

if sgPowerSeqCounter=15500000 then

FTPCIE_ResetSlot lt;=′1′;--拉高PCIE_SLOT_RET

end if;

if sgKeyFlag=′1′ and SysPowerOnKey=′1′ and sgPowerSeqCountergt;Xquot;9F437C0quot; then

--delay 3S=Xquot;8F0D180quot;

sgPowerSeqFlaglt;=′0′;

sgKeyFlaglt;=′0′;

sgPowerSeqCounterlt;=Xquot;0000000quot;;

sgPowOnCounterlt;=Xquot;0000000quot;;

sgPowOnCmdlt;=quot;00quot;;

sgSysStatelt;=′1′;

end if;

end if;

4 结论

软硬件开发之后,在主板上利用示波器对时序电路进行测试。示波器采用双通道、单次出发设置,捕捉上电过程的信号上升沿。通过一一测试,发现利用时钟计时的方法可以比较精确地实现时序的控制,上电过程时延比较稳定,系统运行良好。如果想要调整延迟时间,也可以很方便地进行编程修改。测试中也发现了一个问题,绘制PCB时未充分考虑测试需求,没有能够设置足够的信号测试点,给测试工作带来了一些小困难,所以在以后的设计中要注意安排好系统的可测试性设计。总之,利用文中所设计的软硬件控制方法,成功地实现了FT1500A上电时序部分的设计与实现。为系统的进一步调试和设计奠定了基础。

[1] 钱卫明, 阴泽杰. 可编程延时芯片及其在系统时序控制中的应用[J]. 核电子学与探测技术, 2000, 20(4):305-307.

[2] 陈忠民,李鹰,ATX结构计算机系统的故障诊断[J].微型机与应用,2001,20(9):20-23.

[3] 杨功立. 基于“龙芯”CPU的高性能安全服务器主板的设计与研究[D]. 哈尔滨:哈尔滨工程大学, 2003.

[4] 陈曙光. 基于EPM240T的CPLD开发板设计与实现[J]. 天津职业大学学报, 2010, 19(3):80-82.

2017-04-28)

马强(1991-),男,硕士,主要研究方向:模式识别与智能系统。

李竞航(1984-),男,硕士,主要研究方向:嵌入式系统设计。

王建民(1978-),男,硕士,工程师,主要研究方向:通信与信息系统。

Implementation of power-on timing control of FT1500A motherboard

Ma Qiang1, Li Jinghang2, Wang Jianmin1, Yang Shaoying1

(1. National Computer System Engineering Research Institute of China, Beijing 100083, China; 2. LiuSuoZhiDa (Beijing) Science and Technology Ltd, Beijing 100083, China)

This paper studies a power-on timing control method based on the domestic processor FT1500A. The hardware adopts the programmable logic controller EPM240 as the control unit, and uses the power module LTM4627 to realize the power supply enabling control and the stable detection. The software part uses the VHDL language on the Quartus platform and realizes the delay control by the clock pulse of the statistical programmable logic controller. Using the logic unit within the controller, the power module is achieved to enable the control. Finally the design of the correctness and reliability are verified by the oscilloscope’s single trigger function.

power-on timing control; FT1500A; CPLD; VHDL language

TP30

A

10.19358/j.issn.1674- 7720.2017.22.011

马强,李竞航,王建民,等.FT1500A主板上电时序控制的设计与实现J.微型机与应用,2017,36(22):37-40,44.