神经信息实时处理平台的快速开发*

汤雪娇, 张云鹏, 李 亮, 钱 玲, 王守岩

(1.南京理工大学 电子工程与光电技术学院,江苏 南京 210094; 2.中国科学院 苏州生物医学工程技术研究所,江苏 苏州 215011)

综述与评论

神经信息实时处理平台的快速开发*

汤雪娇1, 张云鹏2, 李 亮2, 钱 玲1, 王守岩2

(1.南京理工大学电子工程与光电技术学院,江苏南京210094;2.中国科学院苏州生物医学工程技术研究所,江苏苏州215011)

针对神经信息处理过程中的高速实时、快速开发、多功能复杂算法实现等需求,对当前几种主流的硬件实时处理开发平台进行比较,并综述神经信息实时处理开发过程及知识产权(IP)核的快速开发方法。同时,对基于可编程片上系统的神经信息实时处理平台快速开发的需求从多平台连接、开发工具之间高效转换和标准化信息处理库三个方面进一步阐述,为神经信息实时处理快速开发的研究提供了参考。

神经信息处理; 可编程片上系统; 快速开发

0 引 言

近年来,脑科学与类脑智能已经成为世界各国研究的热点,其中融合了神经科学、数理科学和信息科学等交叉学科的神经信息处理技术[1],为研究大脑功能提供了重要工具。例如,根据神经信息的处理过程在硬件上对单神经元活动进行建模,以仿真视觉相关神经活动的实时处理过程[2];利用神经集群放电的信息传递过程在硬件上实现神经群的实时放电活动[3],用于类脑研究以及临床实验等。

随着人们对大脑认识的逐渐深入和应用领域的不断扩展,神经信息处理技术的发展有三个特点:在处理速度方面,传输、处理的数据量逐渐增大,神经信息实时处理的需求不断增多[4~6];在处理方法方面,信息处理与智能算法融合[7,8],形成可以应用于模式识别和分类[9]、语音和图像处理[10]、专家系统[11]等场合的复杂算法;在领域应用方面,除医学领域外,自动控制、人工智能等领域亦被广泛关注[12~14]。未来神经信息处理的科研亟需具备更加高速智能的实时处理与控制、更加丰富的算法,以及可以实现复杂算法快速开发的能力。

1 神经信息实时处理硬件开发平台

1.1 3种主流硬件开发平台的比较

目前,用于神经信息处理的硬件开发平台主要有ARM、数字信号处理器(digital signal processor,DSP)和现场可编程门阵列(field programmable gate array,FPGA)3种。其中,ARM是一种通用的32位精简指令集处理器,广泛应用于嵌入式系统设计中[15]。DSP是一种具有特殊结构的专门针对数字信号处理应用而设计的微处理器,该芯片的内部具有专门的硬件乘法器,采用多总线和多流水作业,可以用来快速地实现各种数字信号处理算法[16]。FPGA是一种半定制电路,与DSP和ARM相比,FPGA可利用硬件电路编程灵活实现多种功能,通过并行处理达到更高的信息处理速度。

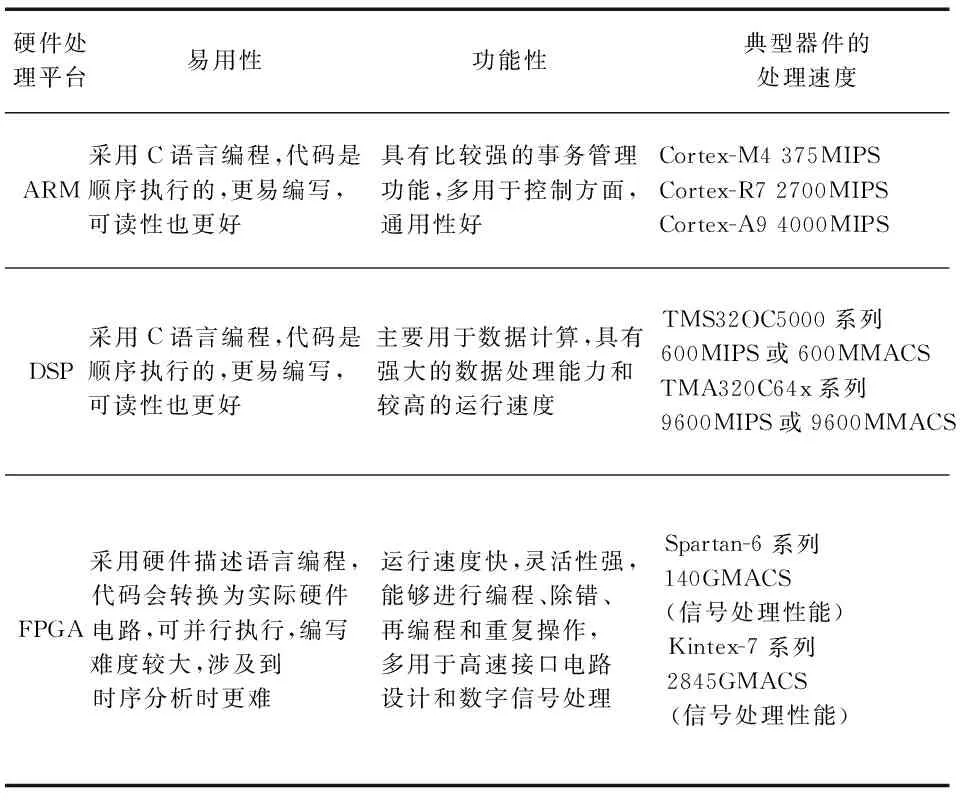

表1为3种开发平台在易用性、功能性之间的比较,同时列出了每种处理器典型器件的处理速度。

表1 硬件开发平台比较

注:MIPS即MillionInstructionsPerSecond,每秒处理的百万级机器语言指令数;MMACS即MillionMultiplicationAccumulationComputingPerSecond,每秒百万次乘法累加运算;GMACS即GigaMultiplicationAccumulationComputingPerSecond,每秒十亿次乘法累加运算。

1.2 3种硬件开发平台的融合

由表1可知,FPGA在运行速度上更胜一筹,更能满足神经信息处理实时性需求。另外,FPGA技术正处在高速发展时期,越来越多的FPGA产品上内嵌了DSP核模块,如Xilinx 7系列产品,能够开发标准的DSP处理器及其相关应用,使FPGA同时具有DSP的良好性能。

此外,随着FPGA芯片集成规模越来越大,速度与信号处理能力不断提高,而且功耗也越来越低,使其在大数据量处理、微小型实时处理平台开发等方面的应用越来越广泛。但FPGA在应用中仍有两个方面需要提升:1)在脑机接口等神经信息实时处理应用中,需要对机械臂等设备进行多自由度控制[17],而FPGA的复杂运算控制能力以及资源协调能力较弱;2)因为使用硬件描述语言,复杂实时处理算法实现过程困难,开发周期长,对编程人员要求高,限制了大量信号处理、机器学习等算法的转换应用。

为了实现高处理速度和灵活控制功能,近年发展出了将FPGA与片上系统相融的可编程片上系统(programmable system on chip,PSoC)技术。PSoC是指将可编程逻辑、硬核或软核处理器、DSP、存储器、外围I/O设备等组件集成在单个器件上,形成一种现场可编程、可重构的通用新型片上系统器件,它是一种可同时实现复杂控制和并行处理的嵌入式系统[18],取代了传统MCU、系统IC等[19]。

以Xilinx公司推出的可扩展平台Zynq®SoC为例,其将通用处理器与可编程逻辑相结合,是一种PSoC。其中,通用处理器由双 ARM Cortex-A9处理器组成,担任控制的“主系统”,以实现灵活的控制能力和强大的资源配置功能;可编程逻辑部分为 Xilinx 7系列构架,提供较高的数据处理能力。

Zynq®SoC系列中,由ARM处理器构成PSoC的处理单元,由FPGA担任可编程逻辑单元。两部分既相互独立,又相互补充,一方面发挥通用处理器顺序执行、控制灵活的特点,另一方面又充分利用FPGA 并行计算、流水线操作、可重构的优势,可以提供更丰富的功能,同时保证高处理速度[20]。以Zynq®系列中的Z-7045器件为例,其数字信号处理性能高达1 334GMACS。此外,Altera公司亦推出了具有相似功能的PSoC。

所以,PSoC融合了ARM与FPGA两种芯片的优点,提供了巨大的串行和并行处理能力,发挥了FPGA逻辑控制对大量数据进行高速处理的优势以及ARM软件编程灵活的特点,能够满足设计具有复杂算法和控制逻辑的实时系统的要求。相对于单独的ARM,DSP,FPGA,PSoC更适合神经信息实时处理、实时控制的发展需求。

2 神经信息实时处理软件开发平台

复杂算法的快速实现是神经信息实时处理性能与应用的另一个关键因素。为了满足神经信息实时处理的快速开发、多功能复杂算法实现等需求,算法开发平台需要具有快速、灵活、高效等特性。

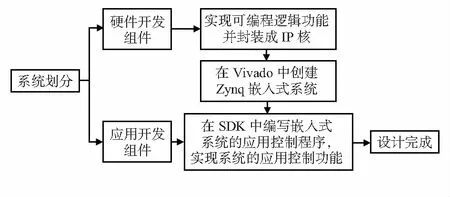

PSoC的开发方式一般基于IP核设计,以Xilinx Zynq®SoC的设计为例,开发过程如图1所示。系统实现的第一步是划分软件设计功能,将系统划分为面向可编程逻辑器件的硬件开发组件和面向ARM处理器的应用开发组件。在实现可编程逻辑后将其封装成IP核,在FPGA的开发环境Vivado中通过接口总线连接各个模块,建立具有定制功能的嵌入式系统。同时,应用开发组件在软件环境下开发工具包,如Xilinx SDK软件环境下开发,编写基于ARM处理系统的应用控制程序,可对在Vivado中创建的嵌入式系统进行控制,建立从硬件、控制到应用的多层级开发流程,增强开发系统的可扩展性及可修改性。所以,对于基于PSoC的神经信息处理开发设计的关键是算法IP核的实现。

IP核的创建方法有很多,传统方法用硬件描述语言实现相应的功能后封装得到,也有使用FPGA快速开发方法实现。使用硬件描述语言创建算法IP核,需要开发人员先在软件上实现算法,再将算法模型转换成硬件描述语言。

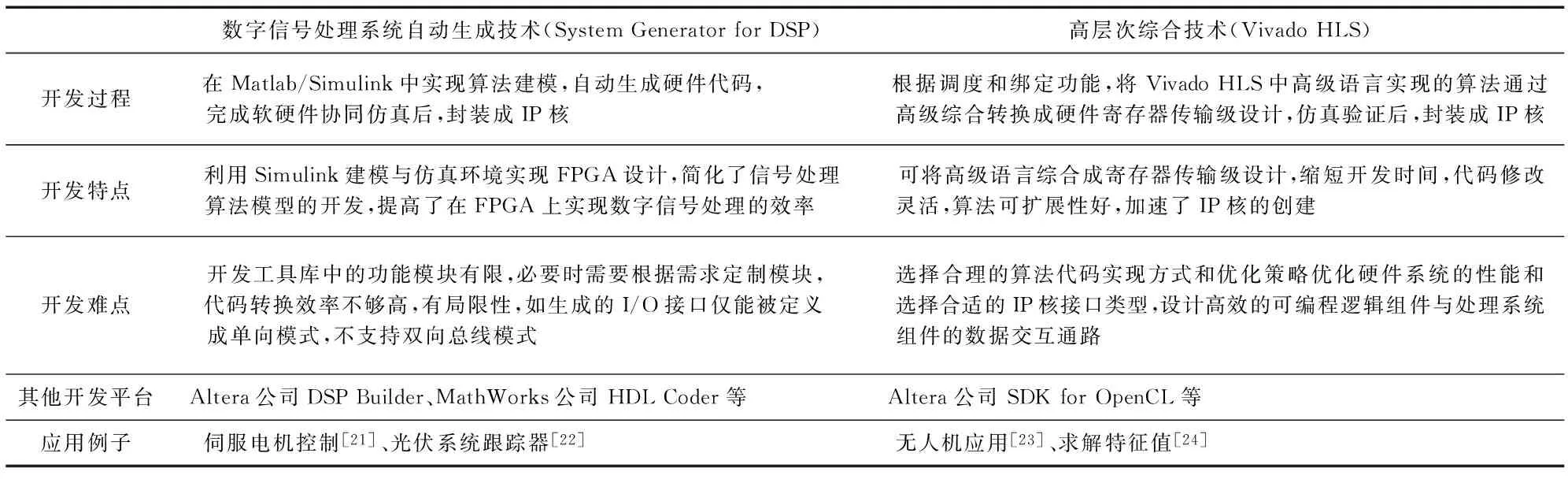

该过程需要开发人员同时具备算法、软件和硬件知识,开发周期长,对开发人员的要求高,无法将大量算法高效实现。针对上述情况,FPGA几大厂商纷纷开放了FPGA的开发平台,推出了基于数字信号处理系统自动生成技术和高层次综合技术的加速FPGA开发的工具。表2是针对两种快速开发方法的典型开发平台System Generator for DSP和Vivado HLS的比较,下面将就开发过程、开发特点及开发难点3个方面对这2种快速开发方法进行具体阐述。

图1 Xilinx Zynq®SoC开发过程框图

表2 2种快速开发方法典型开发平台比较

2.1 软件快速开发方法过程

数字信号处理系统自动生成技术(System Generator for DSP)将FPGA开发软件与目前最常用的信号处理软件Matlab相结合,应用该技术与Matlab中的Simulink实现无缝连接,在Matlab Simulink中快速算法建模,并自动生成硬件代码,将模型进行软硬件协同仿真验证后封装成IP核,以快速实现系统的原型设计。

目前有Altera公司DSP Builder,Xilinx公司的System Generator for DSP和Matlab环境下的HDL Coder三个开发平台。其中,Altera公司已经不再对DSP Builder进行更新支持,其应用逐渐减少。HDL Coder为通用开发平台,生成的代码独立于目标板,代码可读性好,但其硬件移植的匹配度较差。System Generator for DSP生成的代码是专门针对Xilinx器件,其专用性好,相应的应用也较多。

高层次综合技术的核心思想是从功能描述到电路描述的转换,即将高级语言实现的算法功能转换为寄存器传输级硬件电路的描述,实现从C,C++等高级语言到VHDL,Verilog HDL等硬件描述语言的转换。如在Xilinx公司推出的高级综合工具Vivado HLS开发环境中,首先针对功能需求实现C或C++代码,进而利用调度功能确定操作发生的时钟周期,利用绑定功能确定每个操作所使用的硬件库单元[25],这样就将代码映射成硬件逻辑资源,仿真验证后即可封装为IP核。Vivado HLS开发工具能够融合C语言等高级语言的算法库,加速IP核开发。

2.2 软件快速开发方法特点

快速开发软件System Generator for DSP应用最为广泛,利用Simulink建模与仿真环境来实现FPGA设计,降低开发设计人员对硬件描述语言和硬件底层结构的熟悉程度。此外,通过建立具有可执行规范的算法模型,消除设计的不确定性,降低算法开发时间,缩短整体设计周期,降低开发成本。同时,System Generator for DSP提供了数字信号处理的算法模型建立、仿真和实现的环境,简化并加速信号处理算法模型的开发,从多个角度提高了在FPGA上实现数字信号处理的效率[26~28]。

Vivado HLS工具可将符合C,C++和System C规范的代码直接引入Xilinx PSoC器件中,无需手动创建硬件寄存器传输级设计,大幅缩短了开发时间,并且代码修改灵活,可扩展性好,加速了IP核的创建。继而在Vivado软件中设计“系统级”建模,实现PSoC的软硬件协同设计。

2.3 软件快速开发方法难点

1)为了达到理想的系统性能,在使用System Generator for DSP时,需要考虑各个模块的属性和参数以进行综合优化;2)目前,开发工具库中的功能模块仍较为有限,许多算法需要根据需求定制模块;3)虽然这种开发方式可以自动生成硬件代码,但在FPGA开发板上实现时,由于需要与系统工程的剩余部分连接,所以还需要考虑其他方面,如时钟分布、外部储存、接收器等[29],增加了开发困难,且越复杂的硬件结构越困难;4)该技术不适用于需要复杂时钟控制的算法逻辑,如资源的时分复用操作和时钟的双倍数据速率工作模式,因此,生成的系统通常不是最优的,往往需要占用较多的硬件资源;5)该技术不支持双向总线,其设计生成的I/O接口仅能被定义成单向模式,无法将FPGA中的I/O接口配置为输入、输出和高阻模式[30]。高层次综合技术开发FPGA,最重要的是将高级语言代码转换为硬件描述语言的优化过程。对于高层次综合工具Vivado HLS,其数据类型包括标准C整数类型、任意精度类型和浮点类型三类,是将算法代码转换成硬件描述语言的基础;其次,Vivado HLS开发有多种优化策略,如展开、平坦化和合并循环、分割和重组数组、函数内联等,合理运用这些优化策略可以进一步改进硬件实现的性能,如时钟、吞吐量、延迟及消耗的逻辑资源等,同时,优化策略的组合亦具有多样性,所以算法的性能测试与验证尤为必要[31];另外,综合后自动生成的I/O接口会比较复杂,可能会产生并不需要的冗余信号[32];最后,与处理系统组件通信的IP核接口协议高级可扩展接口(Advanced eXtensible Interface,AXI)有3个接口标准,分别是AXI4,AXI-Lite和AXI-Stream,其中AXI4协议提供高速的系统内部互连通道,支持突发传输模式;AXI-Lite协议可以为外设提供单个数据传输;AXI-Stream协议能供主从设备直接连续读写数据,无须地址传输。合理设计IP核的接口方式关系到可编程逻辑组件与处理系统组件的数据交互通路,直接影响设计系统的性能,这是整个设计的重点也是难点[33]。

综上,利用上述2种快速开发技术均可以提升PSoC的开发速度,但两者各有优缺点。高层次综合技术将高级语言向硬件描述语言转换的效率比较高,运行速度快、调试更为容易。System Generator for DSP依托于Matlab开发环境,可利用的算法资源相对较多,但对开发人员的要求更高。目前,高层次综合技术在开发难度、效率与算法资源之间做出了较好的折衷,因而应用更为广泛,在建立高级语言算法库的基础上,是神经信息实时处理的有力工具。

3 基于PSoC的神经信息实时处理快速开发

神经信息实时处理的应用场合广泛,领域发展迅速,因而对算法的广泛性、更新性需求更为迫切。

3.1 更多软件平台的连接

随着神经科学的发展,透明大脑[34]、AlphaGo[35]、外骨骼[36]等神经科学相关产品不断涌现,神经信息处理的算法也越来越丰富,这就要求基于PSoC的神经信息实时处理平台能够与更多的信息处理平台相连,如Matlab,Python等,使其能调度这些软件平台中的库函数,实现算法的高效快速开发。

3.2 开发工具之间的高效转换

基于PSoC的神经信息实时处理的快速开发过程中,Vivado HLS或System Generator for DSP将高级语言或模型设计转换成硬件描述语言的效率仍需提高,并不能实现完全可靠的代码转换。

3.3 标准化信息处理库

为了实现神经信息处理的快速开发,需要建立规范化、标准化的IP核库,以达到快速和可靠实现系统功能的要求。从信息来源的角度,可以建立神经影像库、神经元信号库、脑电信号库等;从算法分类的角度,可以建立信息处理库、统计分析库、智能算法库等;从应用领域的角度,可以建立医学领域应用库、控制领域应用库、经济领域应用库等。

因而,基于PSoC的神经信息实时处理快速开发的关键包括多个软件平台之间的连接、优化开发工具之间的联系、建立标准化的信息处理库。

4 结束语

随着硬件技术和软件平台的发展,神经信息处理在处理速度、开发进程等方面都有很大提升,在各个领域也得到了广泛应用,如神经科学、自动控制、人工智能等。快速开发技术仍处于发展之中,各公司竞相采用新的制造工艺完善软件开发环境,如Xilinx公司推出的内置了Vivado HLS,Vivado和SDK 3个开发软件的集成开发环境SDSoC等。随着技术的进一步成熟,PSoC与快速开发工具的结合,可以大大降低开发难度、提升开发速度、拓展开发应用,实现神经信息处理的快速高效开发。

此外,人们对于神经信息处理算法的关注度也越来越多,如神经网络和深度学习等,为了适应新的需求,研发了人工智能芯片,如Intel推出的主要面向可穿戴设备的Curie芯片,我国研发的世界首个具备深度学习算法的神经网络处理器,寒武纪芯片等。PSoC与人工智能芯片的结合将进一步推动神经信息处理的发展和应用。基于PSoC的神经信息实时处理将进入快速发展阶段,其开发效率将进一步提升,应用范围将涵盖智能硬件、机器人工业、科学研究等多个领域。

[1] 曾志刚,黄廷文,廉 城.神经信息处理[J].国际学术动态,2013(5):28-30.

[2] Li G,Talebi V,Yoonessi A,et al.A FPGA real-time model of single and multiple visual cortex neurons[J].Journal of Neuroscience Methods,2010,193(1):62-66.

[3] Li W X,Cheung R C,Chan R H,et al.Real-time prediction of neuronal population spiking activity using FPGA[J].IEEE Transactions on Biomedical Circuits & Systems,2013,7(4):489-498.

[4] Carta N,Meloni P,Tuveri G,et al.A custom MPSoC architecture with integrated power management for real-time neural signal decoding[J].IEEE Journal on Emerging & Selected Topics in Circuits & Systems 2014,4(2):1-12.

[5] Pani D,Usai F,Citi L,et al.Real-time processing of TFLIFE neural signals on embedded DSP platforms: A case study[C]∥2011 the 5th International IEEE: EMBS Conference on Neural Engineering,2011:44-47.

[6] 郭 华,于胜文.基于物联网的滑坡自动远程监测预警系统设计[J].传感器与微系统,2015,34(4):75-77.

[7] Cui S G,Pan H L,Li J G.Application of self-tuning of PID control based on BP neural networks in the mobile robot target track-ing[C]∥International Conference on Instrumentation,Indonesia: Institut Teknologi Bandung,2013:1574-1577.

[8] 万健如,贾祖新,智渊.ACO-BP神经网络在电梯交通流预测中的应用[J].传感器与微系统,2015,34(11):153-156.

[9] 龚 静,陈向东,时子青.基于CS和神经网络的传感器网络模式识别研究[J].传感器与微系统,2011,30(12):62-64.

[10] Caicai Z,Pugh K R W,Einar M,et al.Functionally integrated neural processing of linguistic and talker information: An event-related fMRI and ERP study[J].Neuroimage,2016,124(part A):536-549.

[11] 杨 静,李丽宏.基于专家系统的汽车衡故障传感器判别[J].传感器与微系统,2014,33(11):34-36.

[12] 宋占魁,赵国强.优化改进传感器精度的自适应神经网络控制策略[J].传感器与微系统,2010,29(7):40-42.

[13] Birle S,Hussein M A,Becker T.On-line yeast propagation process monitoring and control using an intelligent automatic control system[J].Engineering in Life Sciences,2015,15(1):83-95.

[14] 张贯宇,田建艳,张维杰,等.基于模糊神经网络参数整定的仿人智能控制[J].传感器与微系统,2013,32(10):30-33.

[15] 杜春雷.ARM体系结构与编程[M].2版.北京:清华大学出版社,2015:1-11.

[16] 孙进平.DSP/FPGA嵌入式实时处理技术及应用[M].北京:北京航空航天大学出版社,2011:7-44.

[17] Zhang G,Wu J,Liu P,et al.Dynamic analysis and model-based feedforward control of a 2-DoF translational parallel manipulator driven by linear motors[J].Industrial Robot,2013,40(6):597-609.

[18] 于宗光,魏敬和,王国章.SoC和FPGA技术未来的发展趋势[J].电子与封装,2006,6(3):1-5.

[19] 徐 丽,师 卫,赵 梁.基于PSoC的汽车防盗报警系统设计[J].传感器与微系统,2013,32(2):119-121.

[20] 王晓璐.基于Zynq的LS-SVM算法加速器设计[D].哈尔滨:哈尔滨工业大学,2015.

[21] 程 龙,王卫兵,王挺峰,等.Xilinx FPGA system generator在伺服电机控制中的应用[J].电子测量技术,2015(10):68-71.

[22] Faraji R,Rouholamini A,Naji H R,et al.FPGA-based real time incremental conductance maximum power point tracking controller for photovoltaic systems[J].Let Power Electronics,2014,7(5):1294-1304.

[23] 张 展,崔晋伟,陆 炯.基于Xilinx Vivado HLS的小型无人机平衡仪设计[J].电子科技,2015,28(7):172-174.

[24] Bravo I,Vázquez C,Gardel A,et al.High level synthesis FPGA implementation of the jacobi algorithm to solve the eigen prob-lem[J].Mathematical Problems in Engineering,2015,2015:1-11.

[25] 何 宾.Xilinx All Programmable Zynq-7000 SoC设计指南[M].北京:清华大学出版社,2013:365-366.

[26] Meyer-Bäse U,Vera A,Meyer-Bäse A,et al.An undergraduate course and laboratory in digital signal processing with field programmable gate arrays[J].IEEE Transactions on Education,2010,53(4):638-645.

[27] 牛斌凯,雍少为,张 建,等.基于System Generator开发数字信号处理系统[J].舰船电子工程,2010,30(1):129-132.

[28] Aggarwal A,Satija A,Nagpal T.FIR filter designing using xilinx system generator[J].International Journal of Computer Applications,2013,68(11):37-41.

[29] Predki P,Heuer M,Butkowski L,et al.Rapid-X—An FPGA development toolset using a custom simulink library for MTCA.4 modules[J].IEEE Transactions on Nuclear Science,2015,62(3):1.

[30] 范秋香.FPGA高级开发技术的研究[D].北京:北京理工大学,2015.

[31] 何 宾.Xilinx FPGA权威设计指南: Vivado 2014集成开发环境[M].北京:电子工业出版社,2015:347-386.

[32] 符 晓,张国斌,朱洪顺.Xilinx ZYNQ—7000 SoC开发实战指南[M].北京:清华大学出版社,2015:244-257.

[33] 陆佳华,潘祖龙,彭竞宇.嵌入式系统软硬件协同设计实战指南[M].北京:机械工业出版社,2014:137-153.

[34] Chung K,Wallace J,Kim S Y,et al.Structural and molecular interrogation of intact biological systems[J].Nature,2013,497(7449):332-337.

[35] Silver D,Huang A,Maddison C J,et al.Mastering the game of Go with deep neural networks and tree search[J].Nature,2016,529(7587):484-489.

[36] Duong M K,Cheng H,Tran H T,et al.Minimizing human-exoskeleton interaction force using compensation for dynamic uncertainty error with adaptive RBF network[J].Journal of Intelligent & Robotic Systems,2015,82(3-4): 413-433.

Rapiddevelopmentofneuralinformationreal-timeprocessingplatform*

TANG Xue-jiao1, ZHANG Yun-peng2, LI Liang2, QIAN Ling1, WANG Shou-yan2

(1.SchoolofElectronicandOpticalEngineering,NanjingUniversityofScienceandTechnology,Nanjing210094,China;2.SuzhouInstituteofBiomedicalEngineering,ChineseAcademyofSciences,Suzhou215011,China)

Aiming at requirements of high speed,real time,rapid development,realization of multi-functional complex algorithms in neural information processing,several current mainstream hardware development platforms for real-time processing are reviewed.The development process of neural information real-time processing and rapid development method of IP cores are reviewed.It is further elaborated that the requirements of rapid development of neural information real-time processing platform based on programmable system on chip from multi-platform connectivity,efficient conversion between development tools and standardized information processing libraries,and provide a reference for the study of rapid development of neural information real-time processing.

neural information processing; programmable system on chip; rapid development

10.13873/J.1000—9787(2017)11—0001—05

R 319

A

1000—9787(2017)11—0001—05

2016—08—17

国家自然科学基金资助项目(81471745);苏州市神经工程技术重点实验室项目(SZS01414);苏州市医疗器械与新医药专项重点项目(ZXY201425)

汤雪娇(1991-),女,硕士研究生,主要研究方向为神经信息处理算法硬件实现,E—mail:tangxuejiaozb@126.com。

王守岩(1972-),男,通讯作者,博士生导师,主要研究方向为神经工程、神经信息处理、脑深部刺激神经调控,E—mail:swang@sibet.ac.cn。