基于Zynq的战术数据链端机设计

车萌萌,葛海波,王 凯

(1.西安邮电大学,西安 710061;2.西安电子科技大学,西安 710126)

基于Zynq的战术数据链端机设计

车萌萌1,葛海波1,王 凯2

(1.西安邮电大学,西安 710061;2.西安电子科技大学,西安 710126)

为了适应战术数据链向小型化、单兵化的发展趋势,提出了一种基于Zynq的高性能战术数据链端机的设计方案。给出了设计流程和硬件设计原理图。实现了端机的RS编译码、CCSK软扩频、CCSK解扩解调等子模块及PS、PL之间的通信。在vivado IDE、SDK环境下选择Zynq xc7z035 FPGA芯片进行系统级综合、仿真和验证。结果表明,与传统方法相比,该方案简化了端机的实现难度、提高了集成度、帧数据处理速度可达到ms级,硬件成品适合工作在高动态、多节点的场合。

战术数据链,FPGA,RS编码,软扩频

0 引言

数据链作为现代信息化战争的神经系统,从其登上军事舞台伊始,就引起了世界各国的高度关注。当今数据链系统面临着高性能、小体积、低功耗、低成本四大挑战。随着信息化战争的发展,数据链在未来战争中的作用日益深远,因此,对新型战术数据链的研究也尤为重要[1-3]。

目前,多数战术数据链端机是基于传统FPGA、ARM+传统FPGA、DSP+传统FPGA实现数据链通信算法及接口芯片控制[4]。而Xilinx的最新平台Zynq将处理器的软件可编程能力与FPGA的硬件可编程能力完美结合,以低功耗、低成本、高集成度等优势构建了一个更好的硬件平台,其外设接口丰富,包含以太网口、CAN 接口、DDR3、Flash、SPI、串口等,能够满足多数战术数据链在不同场合的需求,为整个嵌入式行业和FPGA行业打开了新篇章。因此,本文基于Zynq提出了一种数据链端机系统的设计方案并进行了方案验证。

1 端机设计

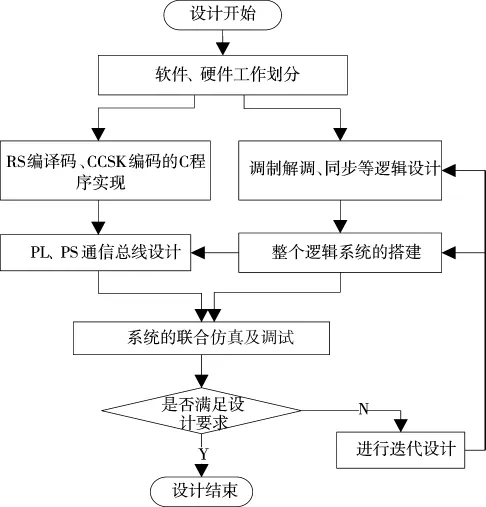

Zynq系列是PS+PL的架构,PS子系统是嵌入式ARM,PL子系统是传统意义上的FPGA[6],它具有异构多核的特点。基于Zynq的数据链端机采用数字信号处理方式,完成通讯信号的编码、解码、扩频和解扩,图1为其设计流程。该设计流程首先对各子功能模块进行合理的任务划分(哪些模块使用C语言在PS中完成,哪些模块使用逻辑语言在PL中完成),一个好的任务划分可以充分发挥系统的性能;然后完成PS和PL之间的通信接口设计;最后,软硬件联合仿真与调试,如果性能、所占资源不满足设计要求,需退到之前的步骤重新设计,直到满足系统的性能指标。

该设计用一片Zynq系列FPGA芯片代替ARM+传统FPGA架构或DSP+传统FPGA架构的两片芯片,减小了电路板的占用量,提高了数据链端机的硬件集成度;被划分到PL和PS的部分可进行同时设计、协调工作,缩短数据链端机的研发周期;该数据链端机还有丰富的外设接口,可以满足多数用户不同接入方式的需求。

图1 数据链端机的设计流程图

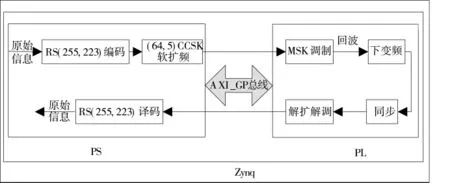

发射端机包括RS编码、软扩频等子模块;接收端机包括解扩解调、RS译码等子模块[7-9]。根据各子模块的性能和资源占用量进行任务划分。在PS中用C语言编程实现RS编码、RS译码、软扩频;在PL中用硬件编程语言实现解扩解调。图2为数据链端机的硬件设计原理图。

图2 数据链端机的硬件设计原理图

2 子模块及AXI总线设计

2.1 RS编码

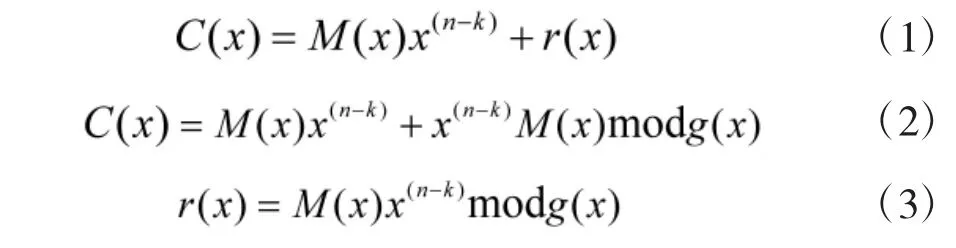

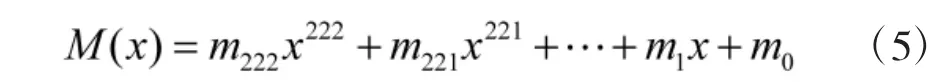

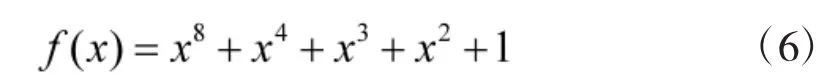

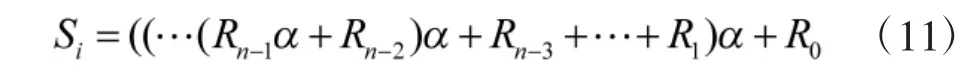

根据 RS 编码原理[10-11]知信息多项式 M(x)、系统码多项式C(x)、校验位多项式r(x)有如下关系:

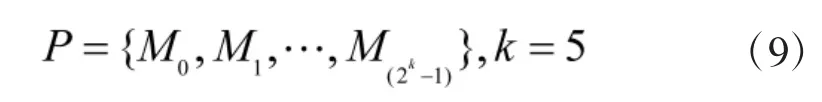

因此,在PS中,采用一个改进型的求多项式除法的算法解出 C(x),实现了 RS(255,223)编码。如图3所示,图中的加法和乘法运算是立在Galosi域上的,不同于数值域,因此,设计了两个域中运算法则之间的转换。当两个非零元素相乘时,只需将指数相加再对码长N取摸,即:

由于域中的每个元素都可用二进制位表示,所以在加法运算中需建立指数形式和二进制形式之间的映射表。查表得到αi和βj对应的二进制矢量a和b,a⊕b就是伽罗华域加法的结果。

准备工作:第 1 步,根据 RS(255,223)编码的基本特征,将信源以每8 bits为一个符号划分,并将信源写成信息多项式的形式,即

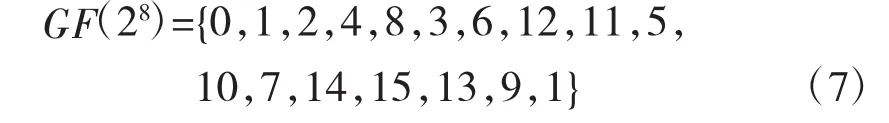

第 2 步,在 MATLAB 中用 rsgengoly(255,223)命令得到其伽罗华域特征方程

第3步,令f(x)=0,求其所有的根,则为GF(28)域的所有元素,即

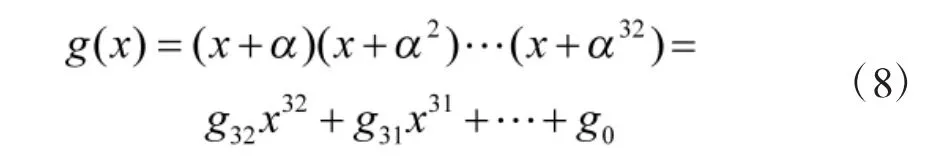

第4步,把域中的元素带入生成多项式:

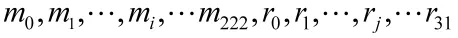

则 g0,g1,…,g32为 α18,α251,…,α11,1。求解 C(x)的过程是一个多次循环的过程。先将暂存器B0~B31的数据清零,以信息多项式的第1个系数作为图中数据输入,再与g0相乘,并将结果暂存到B0中,在下次循环之前,将上次B0到B31结果移位来参与到下一级运算。该过程依次循环k-1次后,B0~B31中的数据则为校验多项式的所有系数。最后编码的码字格式为:

其中mi为第i个数据符号,rj为第 j个校验符号。

图3 求解C(x)的原理图

这种在PS中用C语言实现RS编码的方法,可以用多个循环语句代替逻辑编程中的多个状态机,不需要大量的循环判断逻辑,简化了数据链端机的实现复杂度,减少了逻辑资源占用量,有利于后期算法改进和系列化的工程应用。

2.2 软扩频

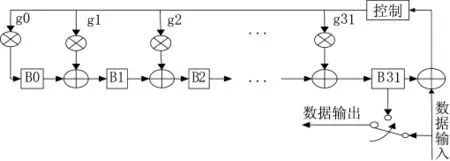

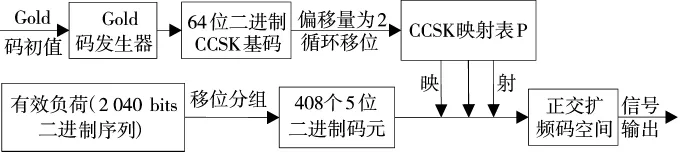

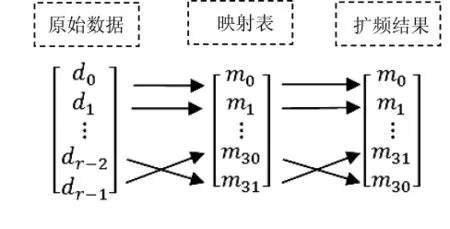

采用CCSK编码(cyclic code shift keying)的软扩频,实质是一种(N,K)编码,即用序列长度为N的伪码序列,与K bits的数据编码一一对应,是从信息空间向伪随机编码空间的映射。伪随机码空间的元素与信息空间的元素一一对应[12-13]。图4是在PS中采用(64,5)CCSK编码实现软扩频的原理图。Gold码发生器设置不同的初值,可得到不同的伪码M0。将M0基码并按偏移量t=2进行循环右移,生成映射表P,即

然后将r bits二进制的原始信息按每码元长度为5 bits分组,可得到(r/5)个码元;再将每个码元与P进行映射,其映射过程如图5所示;最后得到(rN/5)bits的二进制扩频序列。这种在PS中实现软扩频的方法,用C语言编程能够实时改变Gold码的初值以产生多个基码,进而形成多个映射表,增加了设计灵活性和可移植性,有利于数据链工作在多节点情况下。

图4 软扩频原理图

2.3 解扩解调

图5 原始信息与映射表的对应过程

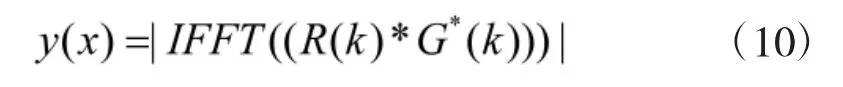

在PL中采用逻辑编程进行并行运算能够很大程度上提高数据处速度。图6为在PL中用循环相关检测法的频域分析法实现CCSK解扩解调[14-15]。其核心思想是:

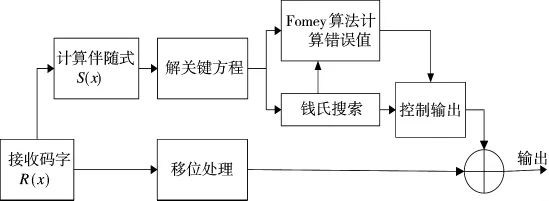

其中R(k)为1个消息帧的FFT变换,G*(k)为本地Gold码的FFT变换的共轭,y(k)则为最大相关峰的幅值。

若接收端机采用10倍码速率的采样率对回波信号进行A/D采样,则每640 bits的消息帧承载了1个信息符号。对每个信息帧进行式(10)运算,其中FFT作的是512点运算。最后把得到每一个消息帧的最大相关峰的幅值yi与基码自相关峰比较,两相关峰的间距值即为该消息帧所承载的信息符号,从而恢复出原始信息。实现该方法,很大程度上提高了接收端机帧处理数据速度,确保了数据处理的实时性,有利于数据链工作在高动态情况下。

图6 CCSK循环相关检测法原理图

2.4 RS译码

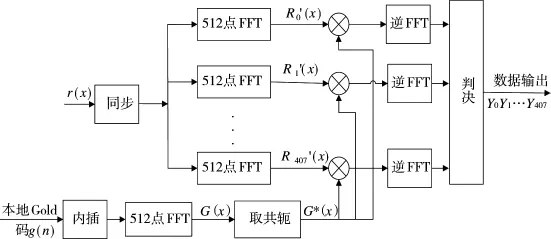

在PS中实现RS译码主要由4部分构成:计算伴随式,解关键方程(错误位置多项式Λ(x)和错误值多项式 Ω(x)),钱氏搜索和错误值修正[11,16,18],如图7所示,其中的加、乘等算术运算是基于伽罗华域的,在RS编码中已说明。

图7 RS译码流程图

采用嵌套的乘累加运算计算解扩解调后的二进制序列的伴随式S(x),即:

其中n=255,α为伽罗华域中的元素。采用传统欧几里德算法解关键方程,对错误位置多项式Λ(x)和错误值多项式Ω(x),其中:

钱氏搜索可求得误码位置。将伽罗华域中的元素带入Λ(x)=0,若等式成立,则在该位置出现误码,接收到的码值和错误值相加的结果就是真值,错误值得到纠正,无错误的数值原样输出,译码结束。

RS译码过程比RS编码复杂的多,仅关键方程的求解就比RS编码需要更多的多项式乘、除运算。因此,这种在PS中用C语言实现RS译码的方法,更大程度上简化了数据链端机的实现复杂度,减少了逻辑资源占用量,有利于后期算法的改进和系列化的工程应用。

2.5 AXI总线设计

在整个系统设计的过程中,影响结果正确性的主要因素还有PS和PL之间的通信。如图2所示,采用AXI_GP总线进行数据交互[19]。AXI_GP的数据总线宽度为32位,吞吐率可达600 MB/s,保证了PL、PS之间的高速数据传输。AXI_GP由PS中的DMAC控制器管理数据的传输。DMAC中的DMA管理器来初始化DMA通道线程。当一个DMA通道线程执行一个加载或者保存指令时,DMAC将指令添加到读或写队列中。在AXI总线上发布命令时,DMAC使用这些队列作为一个指令存储缓冲区。在一个DMA搬运数据过程中,每个通道都设计了一个FIFO集,用于保存读或者写数据。但FIFO的深度不能超过128(64位)字MFIFO。在PS中,先调用XGpio_SetDataDirection()函数设置GPIO指定通道的I/0方向,再通过XGpio_DiscreteWrite()函数将数据写入到设置好的通道中。该互联方式只需在PS中设计即可,不占用PL中的任何逻辑资源,简化了逻辑复杂度。

3 方案验证

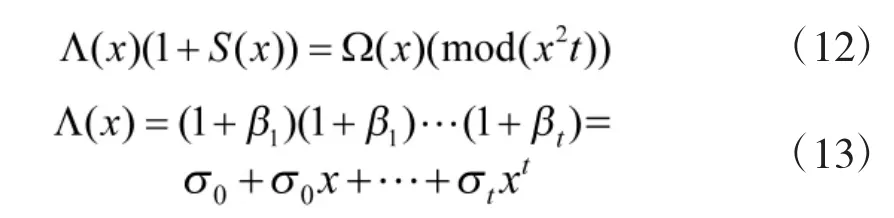

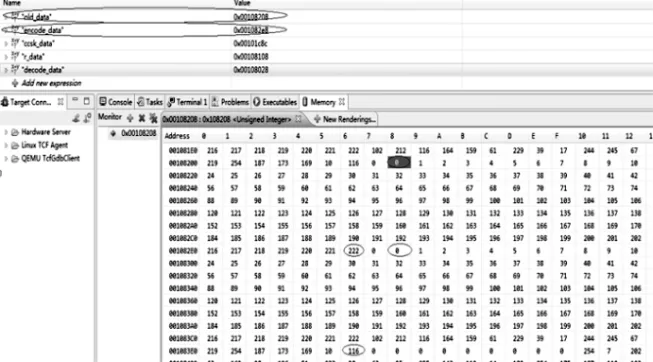

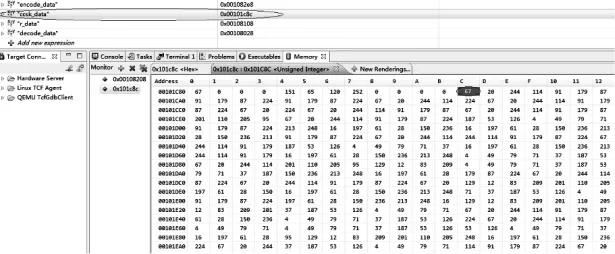

在Vivado IDE和SDK环境下选择Zynq的xc7z035 FPGA芯片实现了数据链收发端机。为了方便方案的验证,采用了自发自收的方式。

其验证过程如下:以 0,1,…,222共 223数据作为发射端机原始数据;选用编码效率不小于70%、编码增益不小于3 dB的(255,223)RS码进行信道纠错;以Gold码为基码,为了消除解扩时伪相关峰的干扰,对基码采用偏移量为2循环移位,进行了(64,5)的CCSK扩频编码;然后进行MSK调制形成调制信号。在接收端机,先进行信号快速捕获、伪码的码同步,之后采用频域的循环相关检测法进行CCSK解扩解调,最后RS译码,矫正错误码,恢复出原始数据。

图8 RS编码结果图

图9 CCSK扩频结果图

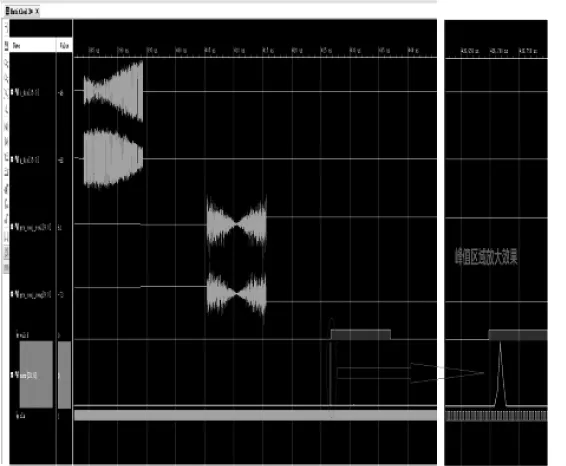

图10 CCSK扩频码与本地Gold码相关峰

图11 RS译码结果

图8是RS编码的结果,其中101~116为编码后的32个以十进制显示的校验位。图9是CCSK扩频后的二进制序列以十进制形式看到的结果。图10中Corr[31∶0]为解扩解调的结果,可以看到一个移位码和本地Gold码相关后的最大峰值,完成了对该码字的解扩解调。为了验证RS码的纠错能力,把CCSK解扩形成的码字第3~18全改为1,共16个数,也是其最大纠错能力。图11是RS译码结果图,经译码已将码字的第3~18共16个1纠正为原来的数据。以上结果与预期值是相符的,且端机系统只占用了25%左右的内存资源,功耗在3 W左右,帧数据处理速度在40 ms左右。

4 结论

本文基于Zynq平台提出并阐述了战术数据链端机的设计方案,最后进行了方案验证。结果表明,这种基于Zynq平台的PS+PL协同工作的方案简化了数据链端机的实现复杂度,提高了系统灵活性和可扩展性,降低了功耗,缩短了产品开发周期。由于设计集成度高,加上逻辑电路的高速数据处理和控制能力,系统的有效性和稳定性也得到了保证,硬件成品适合工作在高动态、多节点的场合。

[1]付继宗,侯磊,冯小琴,等.基于数据链的联合作战技术[J].火力与指挥控制,2014,38(4):12-15.

[2]李桂花.外军无人机数据链的发展现状与趋势[J].电讯技术,2014,54(4):851-856.

[3]钟瑜,陈颖,卢建川.新一代航空数据链端机的SCA架构设计[J].电讯技术,2012,50(4):447-451.

[4]宋家友,莫新康,牛强军.JTIDS消息字还原模块的FPGA设计[J].火力与指挥控制,2012,37(5):152-155.

[5]赵文俊,宋家友.JTIDS传输符号产生模块的FPGA设计[J].电讯技术,2010,50(12):43-47.

[6]邢艳芳,张延冬.基于Zynq的OLED驱动设计[J].液晶与显示,2014,29(02):224-228.

[7]刘翠海,王文清,刘中华.基于VC++的战术数据链通信仿真系统设计与实现 [J]. 电讯技术,2013,53(7):899-903.

[8]张宏欣,王永斌,刘宏波.衰落信道下JTIDS系统的误码性能研究及仿真[J]. 火力与指挥控制,2013,38(10):145-148.

[9]余格非,王振华,李颖,等.信道编码在无人机数据链中的应用研究[J].重庆邮电大学学报,2014,26(6):845-849.

[10]向良军,王梓斌,金国平,等.高速RS编译码器的设计及其 FPGA 实现[J].计算机工程与应用,2012,48(1):68-71.

[11]宋君,文磊,雷菁,等.RS码的实际应用及编译码器设计实现[J].通信技术,2013,46(1):14-17.

[12]唐大宇.结合RS纠错编码和Walsh变换的软扩频技术[J].电讯技术,2012,52(6):943-947.

[13]牟青,魏平.CCSK信号的扩频序列估计[J].电子科技大学学报,2011,40(4):501-504.

[14]黄海燕,张保龙,赵秀英.纠错纠删RS译码数据链系统性能研究[J].现代电子技术,2016,39(13):35-37.

[15]KAO C H,ROBERTSON C,KRAGH F,et al.Performance analysis and simulations of 32-ary cyclic code shift keying[J].International Journal of Communication Systems,2011,24(2):258-268.

[16]王鹏,涂友超,龚克.弹载数据链系统实时RS译码器设计[J].电讯技术,2015,55(5):65-70.

[17]SHEU T L,KUO Y H,CHOU Z T.A packet-interleaving scheme using RS code for burst errors in wireless sensor networks [J].Wireless Sensor Network,2015,7 (7):83-99.

[18]张天瑜.欧几里德算法的RS译码研究及FPGA仿真[J].武汉理工大学学报,2010,32(2):90-95.

[19]陆佳华,潘祖龙.嵌入式系统软硬件协同设计实战指南:基于 Xilinx ZYNQ[M].北京:机械工程出版社,2015:137-153.

Design of Tactical Data Link End Machine Based on Zynq

CHE Meng-meng1,GE Hai-bo1,WANG Kai2

(1.Xi’an University of Posts&Telecommunications,Xi’an 710061,China;2.Xidian University,Xi’an 710126,China)

In order to meet the development trend of the small,individual tactical data link,based on Zynq,a design of high-performance tactical data link terminals is proposed.Firstly,the total design flow and hardware design block diagram are given.The design of terminal mainly realizes the RS encoding and decoding,the CCSK soft spread spectrum,the CCSK dispreading and demodulating,and the communication between the Zynq's PL part and PS part.Finally,on the vivado IDE,SDK software platform,the Zynq series of FPGA xc7z035 chip is selected to accomplish system level integration,simulation and verification.The result shows that,compared with the traditional method,this design simplifies the realization of the data link system,improves the hardware integration,increases the processing speed of the frame data to the level of ms,and it makes the hardware product more suitable for working in high dynamic and multi-node occasions.

tactical data link,FPGA,RS coding,soft spreading

1002-0640(2017)10-0183-05

TN919.3;TN919.4

A

10.3969/j.issn.1002-0640.2017.10.038

2016-09-19

2016-10-09

陕西省自然科学基金资助项目(2111JM8083)

车萌萌(1986- ),女,内蒙古通辽人,硕士研究生。研究方向:电子与通信。