基于MXT2002和FPGA的高速数据采集系统设计与应用

王广君, 刘 刚

(中国地质大学(武汉) 自动化学院, 湖北 武汉 430074)

计算机技术应用

基于MXT2002和FPGA的高速数据采集系统设计与应用

王广君, 刘 刚

(中国地质大学(武汉) 自动化学院, 湖北 武汉 430074)

从整体方案设计和采集端、控制端、传输端、显示端的软硬件设计阐述了基于MXT2002和FPGA的高速数据采集系统的设计方法。采用高速AD芯片MXT2002作为模数转换器,通过FPGA的控制,在CY7C68013的高速USB2.0控制器下,实现480 Mbit/s的高速数据传输,最终在上位机端实现数据的实时显示。通过实验与测试表明:该系统的设计能完成高速数据的采集与处理,通用性较强且能满足一般工业生产中的数据采集需求。

数据采集; 大规模可编程逻辑器件; MXT2002

虚拟仪器技术中的关键技术是数据采集与处理,尤其是数据的高速采集和高速传输。通用的高速数据采集卡——PCI卡或ISA卡,存在价格较贵、扩展性差、安装麻烦的缺点[1]。很多文献提出了数据高速采集和传输的新方案,例如使用AD9226作为高速模数转换器[2-3],使用FPGA+USB或FPGA+ARM进行数据的高速采集与存储[4-5],多通道数据采集[6],使用LabVIEW和VB编程设计数据采集系统[7-8]等。根据对以上方案优缺点分析,笔者设计了由高速ADC芯片+FPGA+USB2.0+C#上位机组成的高速数据采集系统。通过系统设计与仪器研制,证明了该系统设计的可行性。

1 系统设计方案

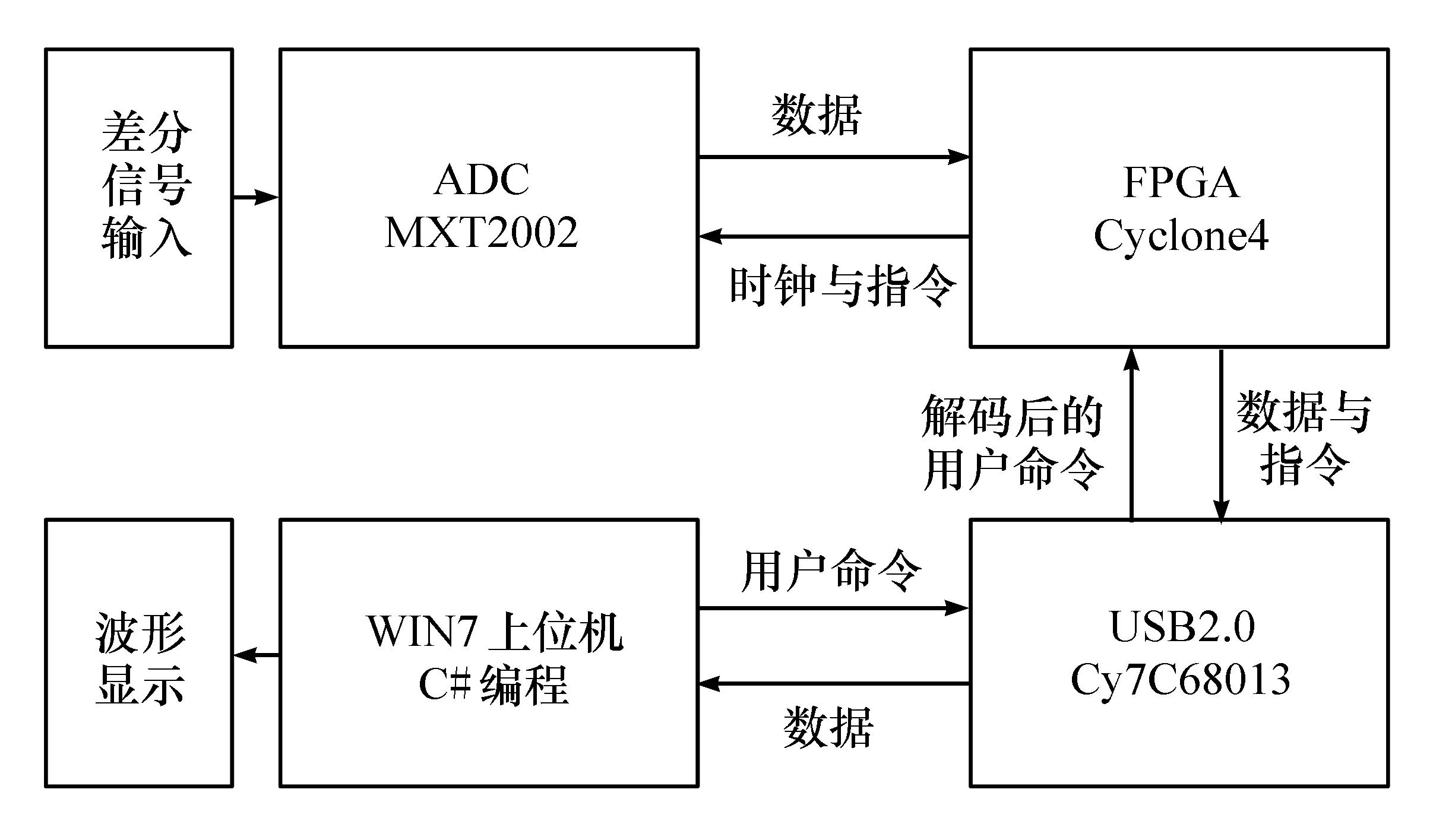

高速数据采集系统的设计方案如图1所示。

图1 高速数据采集系统的设计方案

图1中,MXT2002是精度为8位的高性能CMOS模数转换器,单通道能达到1 GSPS采样率,接收差分信号的输入。笔者从功能设计、引脚分配与价格因素等方面综合考虑,选择具有优越的并行处理能力的FPGA EP4CE40F23C8作为控制芯片。在高速数据采集中,数据传输的安全、可靠尤为关键。本文选择Cypress公司生产的USB芯片CY7C68013A作为上位机与下位机的数据传输芯片。

上位机是数据采集的显示端,利用VS2013编程平台和使用C#开发,具有界面美化、功能齐全和便于后期开发的优点。从图1可看出,差分信号经过模数转换,将数字信号传入FPGA控制芯片,FPGA对数据进行处理后通过USB2.0芯片传输到上位机端并显示。其中,ADC模数转换和USB2.0数据传输均受到FPGA的控制,且用户在上位机端发出的命令会回传到FPGA端,最终实现数据的稳定采集与显示。

2 系统软件、硬件设计

2.1 MXT2002芯片AD转换时序设计

信号采集的通常是单端信号,因此,在模数转换前需要将单端信号转化为差分信号,结合低噪声单端转差分电路[9]和输入限幅可增益放大电路[10]完成单端信号向差分信号的转换,再将经过放大的差分信号送入ADC芯片。由于MXT2002芯片具有高速采集特点,因而控制采集的时序设计对于数据采集至关重要。本文通过三段式时序设计完成MXT2002芯片的单通道采集,其三段式时序设计分别为:时钟复位时序、命令校准时序和数据采集时序。

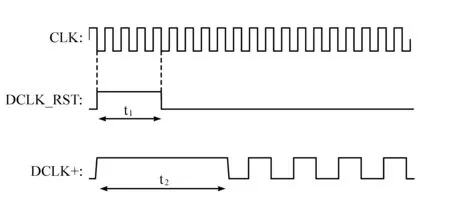

时钟复位时序如图2所示。

图2 时钟复位时序图

MXT2002芯片上电后需进行时钟复位操作,即在DCLK_RST引脚端输入一个脉冲,该脉冲时间大于3个时钟周期。若不进行复位操作,则上电后采集时钟DCLK将不会被触发,且一直保持高电平。复位后,DCLK引脚在短暂延迟后出现方波时钟信号,该DCLK以差分信号输出,将用于上升沿或下降沿的数据采集的时钟信号。

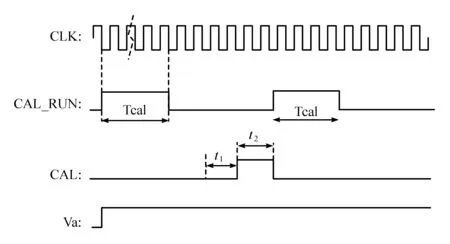

命令校准时序如图3所示。

图3 命令校准时序图

CAL_RUN为校准运行指示,高电平代表器件正在校准。CAL为校准模式启动信号,Va为上电信号,Va和CAL上升沿都会触发校准命令。为了校准的准确性和有效性,提高器件的整体性能,需在上电后进行一次命令校准,即在上电后延迟一段时间t1(t1=80时钟周期)后,CAL紧随80个时钟周期的逻辑高电平输入,将激发电路进入命令校准,在一段延时(Tcal>8 s)之后即可进入数据的采集阶段。

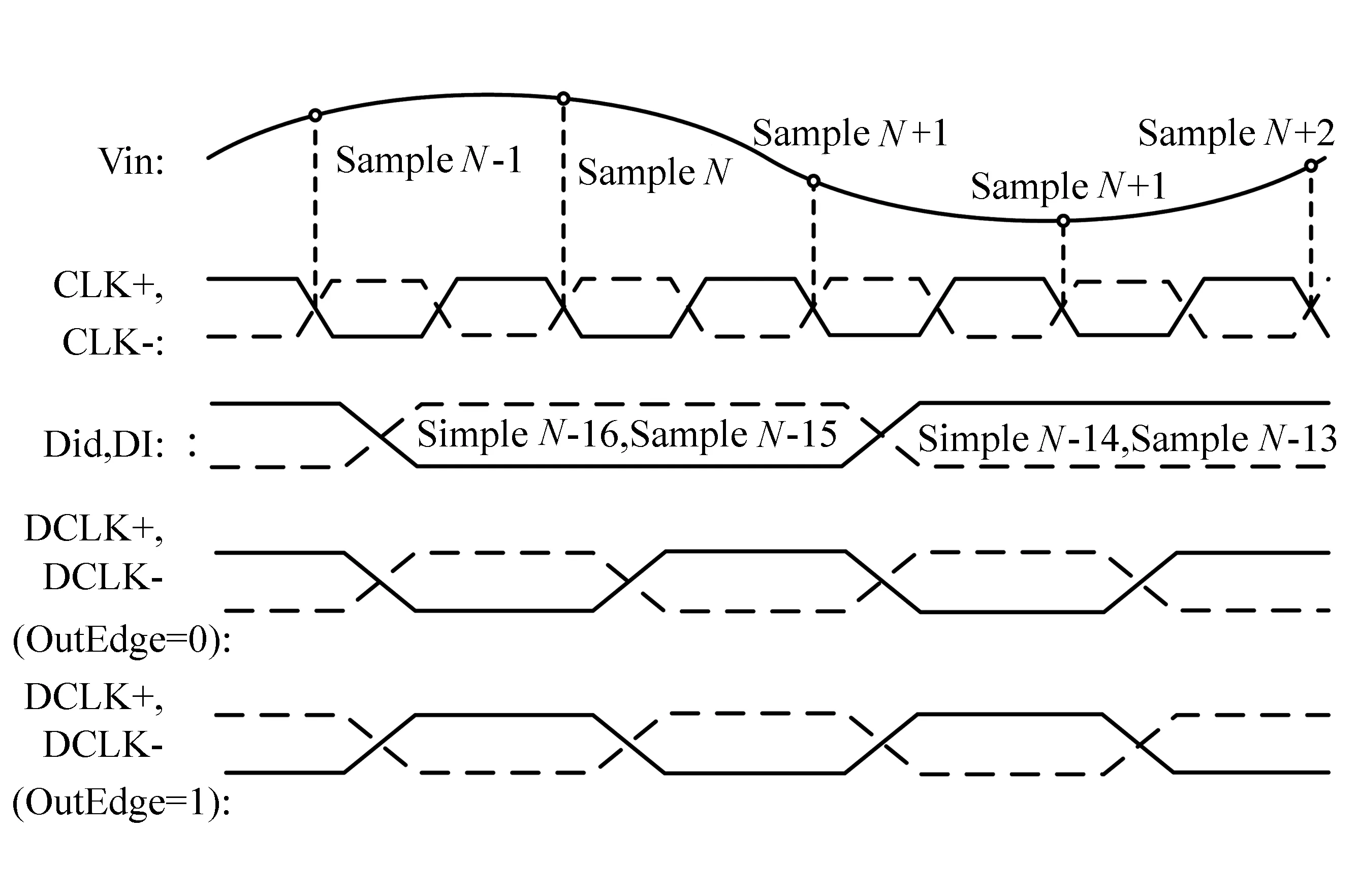

数据采集时序如图4所示。

图4 数据采集时序图

在数据采集时序中,CLK为差分时钟输入,Did和DI为I通道的差分输出,OutEdge为边缘选择信号,DCLK为差分时钟输出。图4中所有的差分信号均是LVDS电平标准,具有极低电压摆幅、高速数据传输的特点,符合本系统的设计要求。从图4还可看出,DCLK信号频率是差分时钟信号的一半,由于该芯片可以设置双边采样模式,即在DCLK的上升沿和下降沿分别采样,因此采集速率并没有降低。

2.2 FPGA采集与控制程序设计

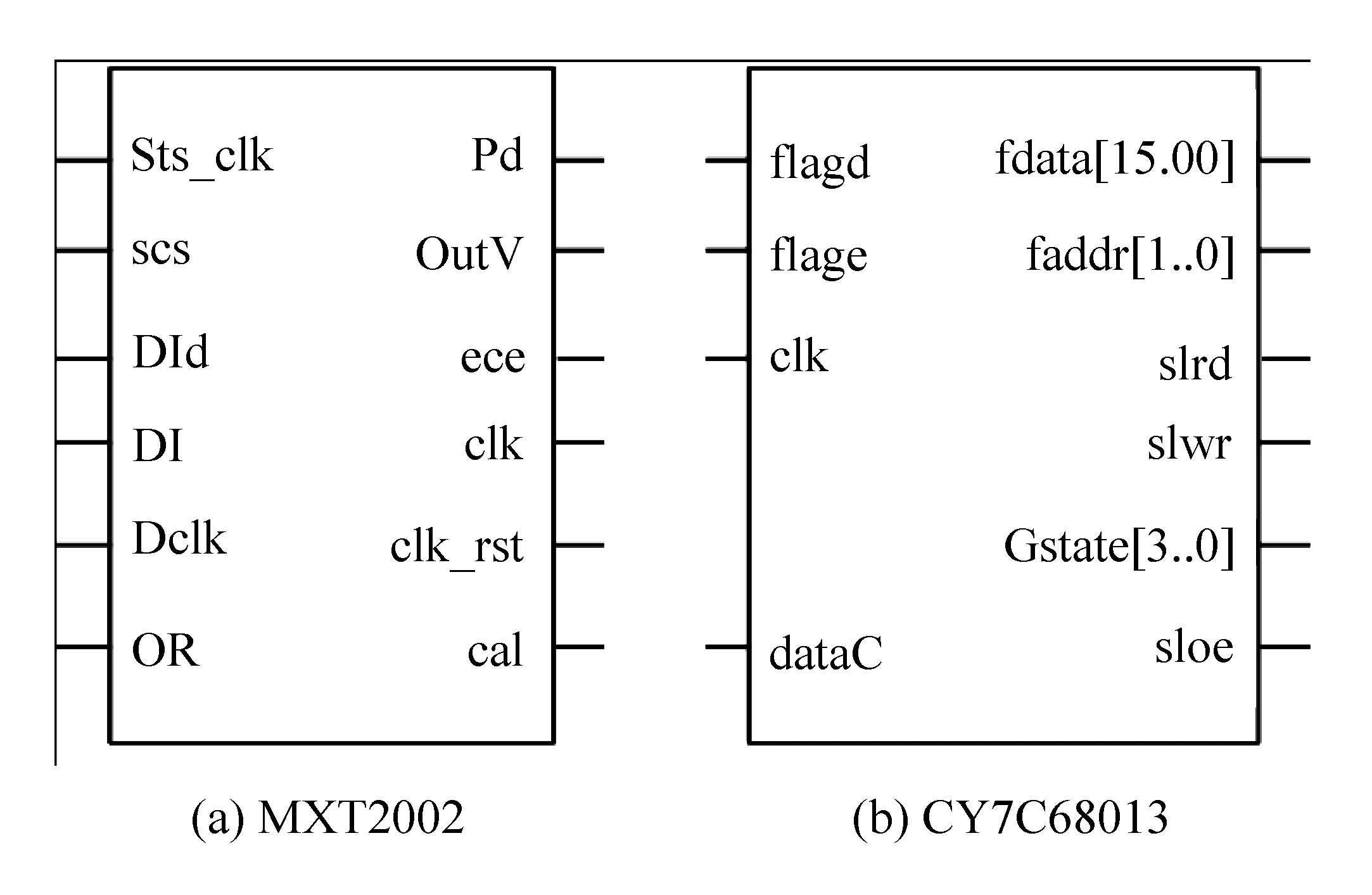

FPGA内的IP软核可重用、可修改,本文对于数据采集和传输控制采用软核设计,在程序设计中直接调用即可。图5(a)为MXT2002采集控制核,图5(b)为CY7C68013传输控制核。在FPGA程序设计中调用该核,并在核内按照控制时序编写硬件语言代码并对应接线,即可完成FPGA对相应器件的控制。

图5 FPGA内部数据控制软核

FPGA的程序设计除了上述两个模块外,还需增加内部PLL倍频模块和数据滤波模块。倍频模块是在FPGA内部产生高频时钟作为AD采集时钟,最高可达到200 MHz以上的频率;如果需要更高的采样率,可以加入外部高频时钟。数据滤波模块对采集的数据进行处理,使数据具有一定的抗干扰能力。当然,类似的数据处理也可以在上位机端进行。

2.3 USB2.0高速数据传输模块设计

2.3.1 Bulk数据传输

Bulk数据传输是指大量数据快速传输模式,此模式可达到53 MB/s的传输速率。为了达到高速传输的目的,CY7C68013依靠片内多个FIFO缓冲器来实现。该模式是在无CPU的干预下,依靠外部的逻辑电路进行的数据传输,保证了数据交互的快速性与稳定性。本文使用Bulk传输模式来传输FPGA端采集到的AD数据到上位机端;而上位机端的命令数据传输不使用该模式,而是使用小数据传输的控制传输模式。

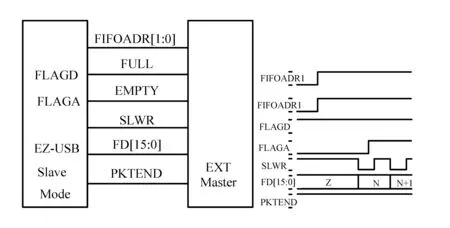

由于数据写入CY7C68013芯片的目的在于上传数据,因此要进行“写操作”。对于Bulk传输的写操作,要严格按照时序进行,其中异步Slave FIFO模式写接口与时序设计如图6所示。

图6 异步Slave FIFO写接口与时序图

图6中,FIFOADR为所选FIFO寄存器,即传输端口选择寄存器;FLAGD为FIFO空状态标志位;FLAGA为FIFO满状态标志位;SLWR为写引脚,有效时在时钟上升沿写入数据;FD为FIFO数据总线;PKTEND为强制传输一个数据包。完成上述的接线和时序要求,即可在上位机端接收到FPGA发送来的数据。

2.3.2 控制传输

有时需要完成数据的下传,如用户命令的传输,则上述使用FIFO的Bulk传输将不再适用。可以使用控制传输模式。

在CY7C68013芯片内,包含唯一一个控制端点——0端点。该端点具有双向数据通信功能,并包含一个64字节的缓冲区(EP0BUF),USB固件可以通过0端点进行控制传输,实现USB协议中的标准设备请求和用户自定义的请求[11]。本文使用0端点作为用户操作指令的回传,即将用户在上位机上的命令通过0端点发送到FPGA控制端,该控制由芯片内固化的增强型C51单片机完成,可实现快速控制,且优先级比Bulk传输模式高。

在CY7C68013固件中,函数TD_Poll()、TD_Init()和SetupCommand()对于控制传输最为关键。TD_Init()中对传输命令的引脚进行初始化;SetupCommand()获取上位机发送的指令;TD_Poll()可编写循环事件,将命令转化成引脚逻辑电平发送到FPGA端。因此,本文控制传输操作步骤如下:

初始化十位引脚TD_Init()

{OEC |= 0xFF;IOC |= 0x00;

OEA |= 0x03;IOA |= 0x00;}

获取用户命令SetupCommand()

匹配SETUPDAT[2]和SETUPDAT[3]寄存器

发送命令TD_Poll()

2.4 C#上位机程序设计

上位机软件采用模块化设计思想,实现数据的实时显示、数据存储、波形显示、数据打印与导出、对下位机控制等功能[12]。传统的LabVIEW设计方法固然简洁,且适合于数据的采集与显示,但界面单一且不利于后期其他功能的扩展。为此,本文在VS2013平台使用C#编程语言设计上位机软件,C#下的上位机设计具有功能多样、界面可变、后期扩展能力强等优点。

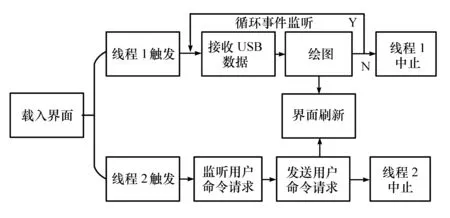

C#下的上位机设计主要包括图形显示和用户控制面板两部分。其中图形显示使用ZedGraph插件,该画图插件具有图形保存、图形任意缩放、坐标自更新、坐标移动等优点,非常适合波形的显示。该设计流程如图7所示。

图7 上位机图形界面设计流程

该设计中使用双线程独立的方式:线程1进行数据的接收与显示,线程2进行用户命令的监听。数据在不断刷新同时,用户可以在面板进行命令操作。

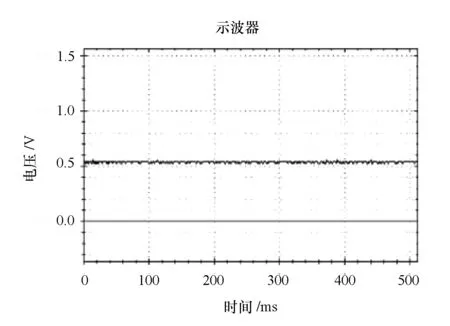

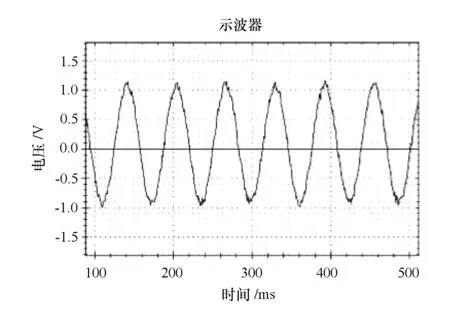

3 实验与测试结果

在设计的高速数据采集虚拟仪器及其上位机上进行了实验。将经过前置放大的输入信号输入本系统,在上位机端可观察到如图8和图9所示的实时显示波形。测试中,ADC的采集时钟是由FPGA内部PLL倍频后供给,达到300 MHz(也是采样率)。可以看出,所设计的高速数据采集系统可以达到虚拟仪器对信号采集的要求。虽然数据有少许波动,但属于正常波动范围,并且可以在后期进行处理,完全满足了工业生产需求。

图8 直流电压测试波形截图

图9 交流正弦电压测试波形截图

4 结语

数据的高速采集与传输是虚拟仪器的关键技术。基于MXT2002和FPGA的高速数据采集系统可通过更换AD芯片达到GHz采样率级别和精度低于1 mV的采集。通过实验测试结果可看出,该系统能满足高速采集与传输的要求,且方便进一步功能扩展,可供研制虚拟仪器时借鉴。

References)

[1] 杜秋姣.基于虚拟仪器的高速数据采集系统的研究[D].武汉:华中科技大学,2004.

[2] 张旭,陈昆明,李蕊,等.基于PCI总线的高速数据采集系统设计[J].船电技术,2008,28(1):9-11.

[3] 张晨亮,苏学军,王成刚,等.基于AD9226的高速数据采集系统的设计[J].实验技术与管理,2017,34(增刊1):63-65,69.

[4] 章勇勤,艾勇,邓德祥,等.基于FPGA的超高速数据采集与处理系统[J].数据采集与处理,2009,24(2):238-242.

[5] 王珏,谭辉,黄亮,等.工业CT用数据采集与传输系统设计及实现[J].仪器仪表学报,2009,30(4):722-727.

[6] 郝晓明,李杰,黄玉岗.基于ADS8568的八路数据采集系统设计[J].传感技术学报,2016,29(1):150-154.

[7] 陈敏,汤晓安.虚拟仪器软件LabVIEW与数据采集[J].小型微型计算机系统,2001,22(4):501-503.

[8] 师桂琴,刘绍中.用VB开发基于虚拟仪器的数据采集系统实例[J].计算机应用,2002,22(9):137-138.

[9] 何晓丰,莫太山,马成炎,等.带有低噪声单端转差分电路的射频增益可控放大器[J].电子与信息学报,2012(4):976-980.

[10] 李海松,刘佑宝.一种差分输入限幅放大电路的设计[J].武汉大学学报(工学版),2009(4):521-524.

[11] 肖远军,方勇,周安民,等.基于USB2.0接口的单向数据传输系统设计[J].计算机应用,2006,26(6):1490-1491.

[12] 徐志良,宋志强,吴晓蓓.基于OPC技术的上位机监控软件设计[J].仪器仪表学报,2003(增刊2):599-602.

Design and application of high-speed data acquisition system based on MXT2002 and FPGA

Wang Guangjun, Liu Gang

(School of Automation, China University of Geosciences, Wuhan 430074, China)

The design method of the high-speed data acquisition system based on MXT2002 and FPGA is described from the whole scheme design, and the hardware and software design of the acquisition terminal, the control terminal, the transmission terminal and the display terminal. By using the high-speed AD chip MXT2002 as the analog digital converter and through the FPGA control, the 480Mbps high-speed data transmission is realized under the high-speed USB2.0 controller of CY7C68013. Finally, the data real-time display is realized at the upper computer terminal. The experiments and tests show that the design of this system can complete the high-speed data acquisition and processing, and it has strong versatility and can meet the needs of data acquisition in general industrial production.

data acquisition; large-scale programmable logic device; MXT2002

TP274

A

1002-4956(2017)10-0125-04

10.16791/j.cnki.sjg.2017.10.031

2017-04-28

王广君(1964—),男,河南禹州,博士,教授,硕士生导师,主要研究方向为图像处理、模式识别、虚拟仪器和数字系统设计.

E-mail:gjwang@cug.edu.cnE-mail:850019690@qq.com