一种改进输入级结构的轨至轨运算放大器设计

宋明歆,关志强

一种改进输入级结构的轨至轨运算放大器设计

宋明歆,关志强

(哈尔滨理工大学 应用科学学院,黑龙江 哈尔滨 150080)

基于0.18 μm CMOS标准工艺设计了一种改进输入级结构的轨至轨运算放大器电路。该电路由输入级电路、共源共栅放大电路、共源输出电路及偏置电路组成。通过引入正反馈的MOS耦合对管将输入级电路改进为预放大电路,然后对其进行了详细分析,利用Cadence软件对电路进行仿真。仿真结果表明本文结构的低频直流开环增益可以达到80 dB,比相同参数下的普通结构高20 dB左右。相位裕度达到73º,共模输入电压范围满足全幅摆动,共模抑制比低频时可以达到107 dB。

轨至轨;正反馈;负阻抗;运算放大器;折叠式共源共栅结构;弥勒补偿

轨至轨运算放大器是一种特殊的运算放大器,其采用NMOS与PMOS互补差分对作为输入级,使得共模输入范围可以从正电源电压到负电源电压。近年来,随着便携式电子设备的蓬勃发展,电路的供电电压不断降低[1]。像轨对轨运算放大器这种输入输出信号范围大的运算放大器越来越受到人们的重视[2]。由于其独特的性能,轨至轨运算放大器被广泛应用于ADC驱动,电源设计等领域。同时,不断变化的应用环境对轨至轨运放的增益提出更高的要求,然而普通结构的轨至轨运放并不能保证运放性能不受影响情况下提高运放增益。

文献[3]中介绍的增益增强技术对共源共栅放大结构进行改进,虽然实现了高增益的目标,但同时引入了四个辅助运放,大大增加了电路的复杂程度,降低了稳定性及抗干扰能力,需要对其进行额外补偿。而文献[4]提出的改进循环结构运算放大器,增益提高明显,但是输入电压摆幅受限、循环结构使用过多,导致电路极其复杂,不利于运放的应用。文献[5]中作者采用三级放大器结构来提高增益,但是这种结构大大牺牲了稳定性,经过补偿后相位裕度才为56º,数值相对较低。

本文针对普通轨至轨运算放大器进行分析,在普通轨至轨运算放大器基础上对轨至轨运算放大器的输入级电路进行改进,在原有互补差分对基础上增加负电阻负载,使得输入级电路承担一部分增益任务,相对于为了增加增益而增加一级增益电路来说对系统的稳定性影响较小,同时满足了现代技术对轨至轨运放越来越高增益的要求。

1 轨至轨运算放大器实现

本文设计运算放大器由带有负电阻结构负载的输入级电路、共源共栅放大电路、共源放大电路和偏置电路组成。其中输入级电路将信号预放大,然后传送给共源共栅放大电路进行主要放大,输出结果从共源电路输出,偏置电路为整体电路提供偏置。

1.1 有负电阻结构负载的输入级电路设计

本文输入级电路采用互补差分对结构,同时分别为NMOS输入差分对与PMOS输入差分对接入耦合MOS对结构作为负载,如图1所示。MN9与MN10为NMOS输入差分对,MP9与MP10为PMOS输入差分对,两者共同搭配使用成为互补差分对。当共模输入较高时,NMOS差分对工作,当共模输入较低时,PMOS差分对工作,所以在很宽的共模输入范围之内,总能保证至少有一个差分对管处于工作状态,从而实现了轨至轨的输入特性。

图1 输入级电路结构图

同时在图1中可见,晶体管MN2与MN1,晶体管MP6与MP7组成了两对3:1电流镜。

与普通的轨至轨运算放大器不同,本文为两对输入对管添加负载电路。普通的轨至轨运算放大器中并不将输入对管的增益计算在内,本文将输入对管改进成可以实现对信号进行预放大的输入放大器,通过MOS耦合对管引入正反馈,从而引入负电阻[7]。使之功能可以实现。

以NMOS差分对及其负载为例进行分析,电路结构如图2所示。假设在晶体管MN9的漏端即A2点有一个小信号的电位上升,则晶体管MP3的栅端电位也上升,MP3相当于是一个共源放大器,所以MP3的漏端会有一个小信号的电位下降。这同样会使得晶体管MP2的栅端电位下降,晶体管MP2同样相当于一个共源放大器,所以输出方向,MP2的漏端产生了一个小信号的电位上升。而晶体管MP2与MN9的漏端相连,所以在MN9漏端产生的小信号电位上升最终会引起MN9漏端的小信号上升。所以可以证明,加入晶体管MP2,MP3耦合对管后,引入了正反馈。

图2 NMOS输入对管及引入负电阻的耦合电路结构

仍然以晶体管MN9的漏端即A2点有一个小信号的电位上升作为前提,则晶体管MP2的漏端电压上升,即MP2两端的漏源电压减小,即:

式中:ΔSD,MP2为MP2源漏端间电压变化量。同时晶体管MP2的栅端电压下降,这代表晶体管MP2的栅源电压绝对值变大,即:

(3)

式中:ΔSG,MP2为MP2源栅端间电压变化量。

根据漏源间电流公式:

式中:GS为MOS管栅源电压;DS为MOS管漏源电压;TH为MOS管阈值电压。可知GS与DS对于漏源电流都有影响,GS绝对值的增大会引起MOS管中电流的增大,而DS绝对值的减小同样会引起MOS管中电流的减小,但是相对来说GS的作用会更大一些,所以:

(5)

此时就可以得出晶体管MP2的小信号交流阻抗:

从式中可以看出由于引入了耦合MOS对管结构,使得晶体管MP2的交流阻抗为负电阻形式,同样MP2交流导纳也为负,晶体管MP4的导纳为正,两者并联,则导纳相加,总的导纳变小,则总的交流阻抗变大了。这个结论的前提是保证从图2中的A1和A2端口看进去的阻抗要保证为正,即MP2和MP3的宽长比要小于MP1和MP4的宽长比。

可以通过小信号模型对输入管结构进行分析,图3为求A2点输出阻抗时NMOS输入对管及引入负电阻的耦合电路小信号模型图,可以求出A2点输出阻抗值为:

图3 小信号模型

式中:o为相应下标MOS管的阻抗值;m为相应MOS管子跨导。这是只计算右半边的值,左半边与之相同,引入了负电阻的耦合MOS结构后相当于将输入级从单纯的输入级变为了低量级的放大电路,对于整体电路的增益提高起到推进作用,同时它比单独引入二极管连接负载的输出阻抗更大,也就是说其所形成的信号放大能力更强。

1.2 共源共栅放大电路及共源输出电路

本文为了获得较大的增益,所以选择共源共栅结构作为轨至轨运放中的主要放大作用承担者,同时折叠式共源共栅结构相比于套筒式共源共栅具有更大的输出摆幅[8]。可以达到:

式中:DD为电源电压;Dsat为过饱和驱动电压。两者的增益基本相同,所以本文选择折叠式共源共栅结构,如图4所示,其中共源共栅结构的增益为:

(9)

式中:mn,mp表示输入对管在切换工作时,共源共栅结构的跨导值。

图4 共源共栅放大电路及共源输出电路

本文同时采用PMOS共源放大器作为输出电路,进一步地放大信号,且其可以进一步扩大输出摆幅,实现轨至轨功能,其增益为:

为了保证整体系统的稳定性,在本文中使用弥勒补偿电路进行频率补偿[9]。

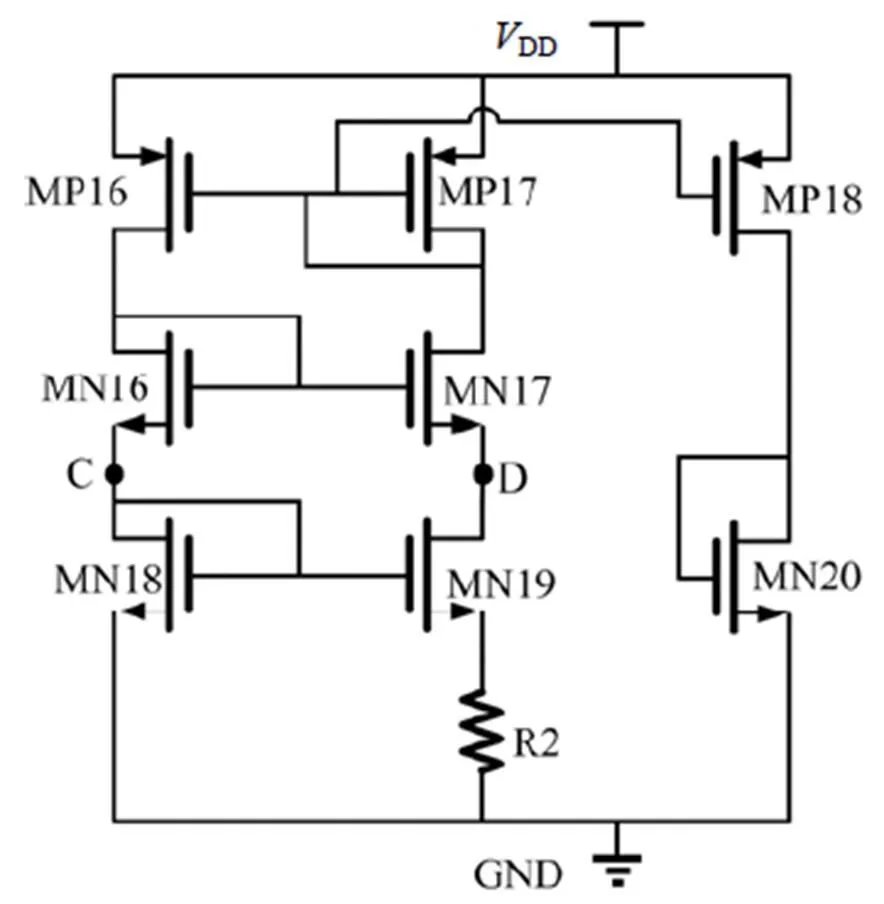

1.3 偏置电路设计

本文采用cascode电流镜结构的偏置电路为整体电路提供相应的电压偏置[10]。偏置电路如图5所示。在偏置电路中晶体管MP16与MP17尺寸相同,MN16与MN17尺寸相同,所以两根支路中的电流互相复制,但是电流大小不确定,所以引入电阻R2来确定电流,并且这四个晶体管使得电路中C点电位与D点电位箝位,即C=D,此时:

所以支路中的电流:

(12)

式中:2为R2的阻值。这样就可以得到固定电流,再通过外接晶体管MP18与MN20支路进行引出固定电压偏置。

图5 偏置电路

2 仿真结果与分析

本文采用0.18 μm CMOS工艺库,利用Cadence软件对电路进行仿真,为了凸显输入级电路改进作用,将普通轨至轨运放与本文运放的增益进行比较。

开环增益曲线如图6所示,上边的曲线为本文电路结构的仿真增益曲线,下边曲线的结构与本文所述结构只有输入级不同,其他部分结构与参数完全相同。从图中可以看出,本文所述的轨至轨结构增益为82 dB,相比另一条曲线高出接近20 dB,并且可以从曲线中看出输入级电路的改变并未引入新的零极点,对于电路其他的性能影响较小。

图6 开环增益曲线

图7为共模输入电压范围曲线。从图中可以看出,共模电压的输入范围非常接近地(GND)与电源电压(DD),证明本设计引入的负电阻输入管结构对于共模输入范围影响不大。

图7 共模输入电压范围曲线

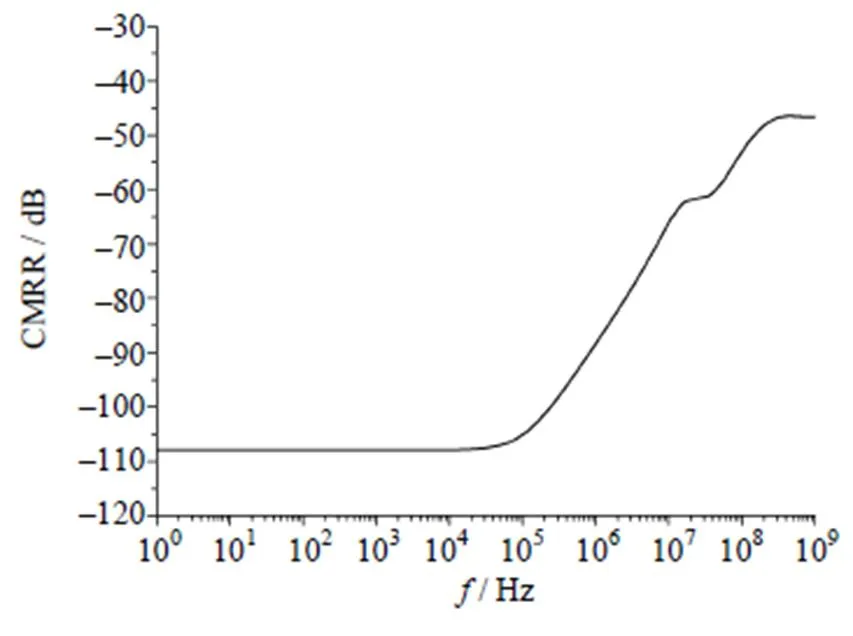

图8为本文设计的运放的共模抑制比,可以从图中看到低频时共模抑制比达到107 dB,数值很高。

图8 共模抑制比曲线

同时本文也对运放的相位裕度进行了仿真,本文设计的运放结构相位裕度为73º,满足稳定性60º的条件,达到稳定。

3 结论

本文在传统轨至轨运算放大器结构基础上,对输入级电路进行负载改进,将单纯输入管改为预放大管,在满足稳定性及轨至轨特性要求的前提下实现更高的直流开环增益,同时通过Cadence仿真软件对本文结构进行仿真,开环增益为82 dB,相位裕度为73º,共模输入电压范围满足全幅摆动,共模抑制比低频时可以达到107 dB。

[1] 拉扎维. 模拟CMOS集成电路设计[M]. 陈贵灿, 程军, 张瑞智, 等, 译. 西安: 西安交通大学出版社, 2003: 5-6.

[2] 桑森. 模拟集成电路设计精粹[M]. 陈莹梅, 译. 北京:清华大学出版社, 2008: 208-210.

[3] 史志峰, 王卫东. 一种全差分增益增强型运算放大器的设计[J]. 电子器件, 2015(1): 78-82.

[4] YAN Z, MAK P I, MARTINS R P. Double recycling technique for folded-cascode OTA [J]. Analog Integr Circuits Signal Process, 2012, 71(1): 137-141.

[5] 班博, 姜岩峰. 一种高增益多级运算放大器的设计[J]. 微电子学, 2015, 45(6): 706-709.

[6] 莫宝争. 基于CMOS恒跨导运算放大器的设计与研究[J]. 工业控制计算机, 2016, 29(5): 146-147.

[7] WANG R, HARJANI R. Partial positive feedback for gain enhancement of low-power CMOS OTAs [J]. Analog Integr Circuits Signal Process, 1995, 8(1): 21-35.

[8] ASSAAD R S, SILVA-MARTINEZ J. The recycling folded cascode: a general enhancement of the folded cascode amplifier [J]. IEEE J Solid-State Circuits, 2009, 44(9): 2535-2542.

[9] AQEEL S, DEVA P K, BABU C M, et al. Design of high gain two stage Op-Amp using 90 nm technology [J]. Int J Eng Res Technol, 2014, 3(5): 1966-1970.

[10] 艾伦. CMOS模拟集成电路设计[M]. 冯军, 李智群, 译. 第二版. 北京: 电子工业出版社, 2007: 103-111.

(编辑:张金平)

Design of a rail-to-rail operational amplifier with improved input stage structure

SONG Mingxin, GUAN Zhiqiang

(School of Applied Sciences, Harbin University of Science and Technology, Harbin 150080, China)

Based on 0.18 μm CMOS standard process, a rail-to-rail operational amplifier circuit which can improve the input stage structure was designed.The circuit was composed of the input stage circuit, the cascode amplifier circuit, the common source output circuit and the bias circuit. The input stage circuit was improved as a pre amplifier circuit by introducing the MOS coupling with positive feedback, a detailed analysis was carried out, and the circuit was simulated by using Cadence software. The simulation results indicate that the circuit has a DC open-loop gain of 80 dB, which is about 20 dB higher than the ordinary structure under the same parameters. The phase margin is 73°, the common-mode rejection ratio (CMRR) is 107 dB at low frequency, and the common-mode input voltage range also meets the full swing.

rail-to-rail; positive feedback; negative impedance; operational amplifier; folded cascode structure; Miller compensation

10.14106/j.cnki.1001-2028.2017.10.009

TN432

A

1001-2028(2017)10-0053-05

2017-07-18

关志强

宋明歆(1974-),男,黑龙江哈尔滨人,副教授,研究方向为模拟集成电路设计,E-mail: 361456176@qq.com ;关志强(1991-),男,黑龙江哈尔滨人,研究生,研究方向为模拟集成电路设计,E-mail: guanzhiqiang63342@163.com 。

2017-09-27 10:57

网络出版地址:http://kns.cnki.net/kcms/detail/51.1241.TN.20170927.1057.009.html