可靠UDP协议栈的FPGA实现

刘 源,张 刚

(太原理工大学信息工程学院,太原 030024)

可靠UDP协议栈的FPGA实现

刘 源,张 刚

(太原理工大学信息工程学院,太原 030024)

基于Xilinx公司的Virtex-5系列FPGA开发板,采用VHDL硬件描述语言,并运用模块化的设计理念,参考TCP_IP协议栈的工作机制,设计并实现了一个具有接收确认及漏发重发功能的可靠的UDP_IP网络通信协议栈。同时,设计并实现了一个以太网控制器,该控制器与UDP_IP协议一起构成一个完整的网络通信链路协议。经过上板测试验证,该通信协议栈能正确高效地完成网络数据的发送和接收等工作,且稳定性良好。

可靠UDP,通信协议,FPGA,VHDL

0 引言

传统的网络通信设备依赖操作系统本身内置的TCP_IP协议栈来实现网络设备之间的数据通信,此种方式需要消耗设备大量的CPU资源,在一定程度上束缚了CPU效能的发挥。为此,本设计提供了一种硬件方式实现的UDP_IP协议栈,采用此种硬件协议的网络设备,数据通信功能可以作为一个模块而单独存在,可以大大减少CPU资源的占用。由于UDP协议是不可靠的协议,其并不能保证数据传输的完整性,为此本设计对传统的UDP协议做了改进,使其具备接收确认及丢包重发等保证数据可靠性传输的基本特征。同时本设计还设计实现了一个以太网控制器,它与上层协议一起用于从物理链路介质发送和接收数据。经过仿真验证及上板调试验证,该UDP协议栈能正确、快速高效地完成网络数据的发送和接收等工作,较好地实现了网络数据通信功能,达到了本文设计的要求。

1 UDP_IP协议栈功能简介

UDP_IP协议栈是一系列具有特定结构的协议的总称,它是网络设备接入互联网的标准协议,网路上的设备只要支持该标准,就可以与其他设备进行数据通信[1]。

UDP_IP协议栈按照功能划分可以分为4个层次,自上而下分别为应用层、传输层、网络层、链路层。其中应用层中包含了大量的客户端普遍需要的协议,例如FTP、HTTP、SMTP等,这里其主要用来作为应用程序与外界进行数据交换的通道。传输层有两个不同服务类型的协议,即传输控制协议TCP和用户数据报协议UDP。TCP协议提供的是可靠的无差错的数据传输服务,在进行数据传输前要先与对方设备进行3次握手连接,且对发送的每段数据都要进行接收确认,因此,其控制机制比较复杂,传输速度相对来说比较慢,它适用于那些对数据传输的准确度要求较高但对传输速度不作太多要求的场合。UDP协议在进行数据传输时不用与对方设备提前建立连接,其不对发送的数据进行接收确认,所以其提供的是不可靠的数据传输。它适用于那些对数据传输的实时性要求比较高但对数据传输差错要求比较低的场合。因为UDP协议具有传输速度快效率高且控制机制简单等优点,并且它的可靠性可以加以改进,所以本设计的传输层采用改进的可靠UDP协议[2]。网路层主要负责添加及解析IP头并控制数据在网络上面的传输,是UDP_IP协议栈的重要组成部分,处在该层的有IP协议、ICMP协议等。链路层位于UDP_IP协议的最下层,它主要用来校验数据以及对发送或接收的数据进行帧格式的封装或拆封以便于在物理链路上进行传输,位于该层的协议有ARP协议、RARP协议等。

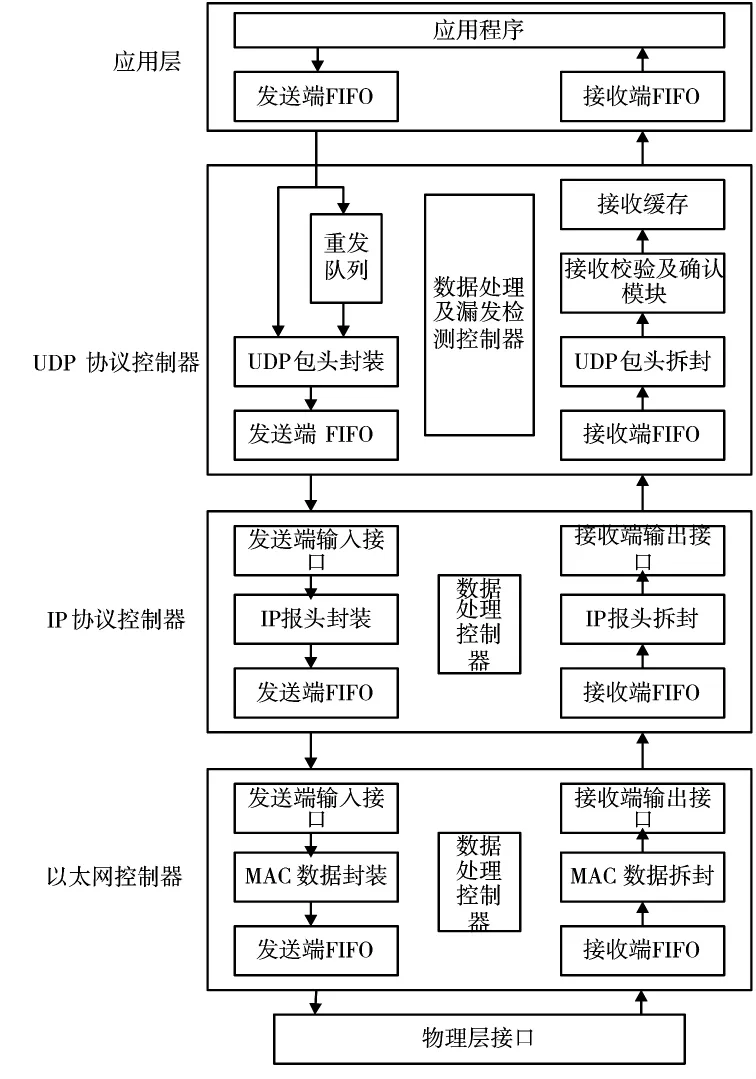

2 总体设计

本设计是以UDP_IP协议栈为基础,采用分层次模块化的设计方法,从上到下分为3个模块即UDP协议控制器模块、IP协议控制器模块和以太网控制器模块,其中每个模块内部都有相应的数据处理控制器来控制数据的处理,以此来模拟实现UDP_IP协议栈中的各层协议的功能。各个模块彼此处理各自的数据,模块之间通过先进先出FIFO队列来进行数据的接收和发送,以此来实现各个模块之间数据处理过程的相对独立,同时也便于优化结构设计以及出错查找。其原理结构如图1所示。发送数据时,在UDP协议控制器模块中,数据从应用层传输过来后先在重发队列里面复制一份用来作为重发的备份数据,接下来再进行UDP数据头的封装。封装好的数据再依次传入IP协议控制器和以太网控制器,以完成数据帧格式的封装然后再发送到物理链路上。接收数据时,数据从物理链路上下来后要依次经过以太网控制器和IP协议控制器,在这期间完成数据包的拆封最终取出UDP格式的数据传递到UDP协议控制器里面。接下来,漏发检测控制模块用来完成对接收数据的校验及数据完整性的检验,并决定数据是否需要进行重新发送,如需重发,则向数据发送端发送一个重发请求,发送端接到该请求后再依次重新发送相应的数据包。如不需要重发,则取出数据传递给应用层。其中,数据处理控制器利用状态机的状态转换来控制数据传输模块内部数据的封装、拆封、校验等一系列处理动作。

图1 UDP协议栈总的原理结构

2.1 UDP协议的可靠性机制原理及UDP协议控制模块的设计

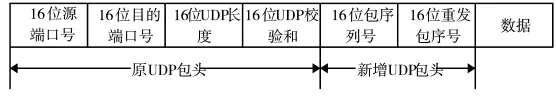

UDP协议控制器模块主要用来对发送数据进行包头的封装和对接收数据进行包头的拆封,以及对接收到的数据包进行校验确认和漏发检测等工作。为了增强UDP数据传输的可靠性,需要对原有的UDP协议的格式稍作修改,在UDP原有包头的后面新增加了2字节的包序列号字段和2字节的重发包序号字段,修改后的UDP报文格式如图2所示。

图2 UDP报文格式

其中,包序列号用来标记所发送的UDP数据序列,该序列号与重发队列中的数据段序号一致,系统初始化时都置为0x”0001”;重发包序号在UDP发送端正常发送数据时置为零,当接收端检测到有漏发的UDP包或UDP校验出错而需要发送端重新发送该包数据时,则该字段填入需要重发的包序列号。UDP校验和与UDP包序列号一起来对接收到的数据包的正确性和完整性进行检验。

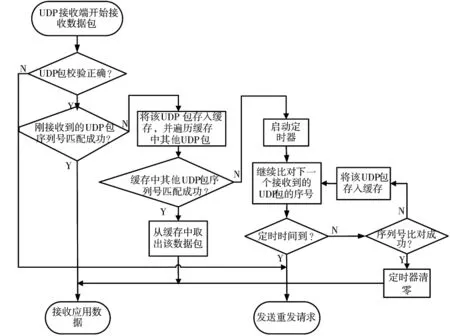

检错重发和漏发重发机制的具体原理流程如图3所示。在UDP接收端有一个UDP包序号寄存器,该寄存器用来寄存最近一次成功接收到的UDP数据包的包序列号,该寄存器初始化值为1。当UDP接收端接收到UDP包后,进行UDP校验,校验采用二进制反码求和算法,如果校验和出错,则取出该包序列号,然后向发送端发送一个包含本序列号的重发请求,同时丢弃该包数据。如果校验和没有错误,则进入下一环节,即进行UDP包序列完整性的检验。

在完整性检验环节,如果该UDP包的16位包序列号的值等于包序号寄存器的值,即序列号匹配成功,则说明该UDP包与接收到的上一UDP包是连续的,可以取出该包中的应用层数据,同时包序号寄存器值自动加1,来指向下一个想要接收的包;否则如果不相等,则将该UDP包存入接收缓存队列中,同时遍历缓存队列中其他的UDP包。如果缓存队列中有UDP包的序列号等于包序号寄存器的值,即匹配成功,则从缓存当中移出该UDP包,提取出包中的应用数据后丢弃该包,同时包序号寄存器的值加1;如果缓存队列当中没有UDP包匹配成功,则启动一个定时器,在定时时刻到来之前包序号寄存器持续的与后面收到的UDP包相匹配,匹配成功则关闭定时器同时取出应用数据并更新包序号寄存器的值,不成功则把该UDP包存入缓存队列,然后继续匹配下一个UDP包。如果定时时间到了,还没有匹配成功,则向发送端发送一个包含缺省包序号的重发请求。发送端收到重发请求后从该请求中取出需要重发的包序号,然后从重发队列中找到该包对应的数据,后再从该数据处重新依次发送后面的数据。

图3 重发机制流程

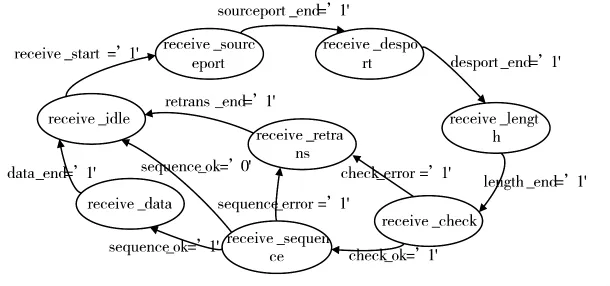

下面以数据的接收过程为例来说明数据的处理流程,其状态流程如下页图4所示。接收端的数据处理及漏发检测控制器的控制状态可以划分为8个状态,系统启动后先进行复位,复位完成后状态机处于receive_idle状态,复位时数据进行初始化,初始化包序号寄存器的值为‘1’同时初始化校验缓存的值为‘0’,当receive_start为高电平时说明数据开始进行接收,接下来依次进入receive_sourceport和receive_destport状态,分别接收数据的源端口号和目的端口号,再接下来进入receive_length状态,接收数据包长度,该长度包含UDP包头和用户数据两部分。数据包长度接收完成后进入receive_check状态,该状态下完成接收到的数据的校验和检验,UDP校验和的具体算法为:校验缓存的初始字段设为0,然后把8字节的UDP包头和12字节的UDP伪包头分别拆分为2字节进行32位的累加,得到32位的累积和之后再把该累加和的高16位与低16位累加取反,即得到校验和[3]。发送时把校验和添加到UDP包头即可,接收时再重新做一遍相同的计算,如果校验计算结果中的各位数字全为1,则说明校验正确,状态机接下来进入receive_sequence状态,否则进入receive_retrans状态。状态机处于receive_sequence状态时接收端需要对接收到的数据是否有漏包的情况进行检验,具体检验过程为:状态机跳转到receive_sequence状态后就马上提取出包序号的值并与包序号寄存器里面存储的值相比较,如果接收到的16位包序号的值等于包序号寄存器的值,则进入receive_data状态接收用户数据同时包序号寄存器的值加1,否则如果接收到的包序号与包序号寄存器的值不一致,则暂存该UDP包到接收缓存队列里面,同时比对缓存队列中其他的UDP包的序号是否与包序号寄存器当中的值相等。缓存中如有UDP包与包序号寄存器的值匹配成功,则从缓存当中移出该包,接着状态机进入receive_data状态接收该包的应用数据,并同时更新包序列寄存器的值。如果没匹配成功,则启动一个定时器,同时状态跳转到receive_idle状态,开始接收下一个UDP包。在该定时器的时间段内,如果后续接收到的UDP包的序列号与包序号寄存器里的值一致,则定时器清零,与此同时状态机进入receive_data状态接收数据,并且更新包序号寄存器的值;不一致则把UDP包存入缓存队列中,然后状态机跳转到receive_idle状态,继续接收下一个包,并继续比对下一个UDP包的序号。如果定时时间到了,还没接收到所要的数据包,则进入receive_retrans状态。在receive_retrans状态,需要把校验出错的包序号或漏发的包序号的值发送给本地的数据发送端,让发送端重新发送相应的数据包[4]。待receive_data状态结束后,即一个UDP包的应用数据已经接收完成,则进入receive_idle状态开始准备下一个UDP包的接收。

2.2 IP协议控制器的设计

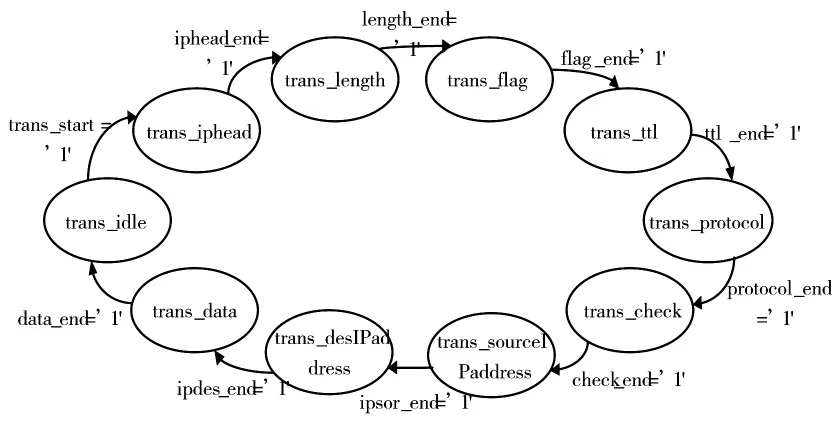

IP协议控制器主要用来完成IP报头信息的添加以及IP报头的拆封解析等工作。其中报头的封装和解封都由状态机来控制执行,通过字节计数器的计数值作为判定条件,从而实现状态的跳转来执行各状态的相应的操作。以数据发送端为例,其状态机的状态跳转过程如图5所示。

图4 UDP接收端状态流程图

图5 IP协议控制器发送端状态流程

trans_idle为等待状态;trans_iphead状态时设置IP的版本号、首部长度及服务类型;trans_length状态时统计数据总长度,并把结果存放在IP头里面;trans_flag状态时在IP头相应位置填入IP的标识、标志、片偏移等数值;trans_ttl状态时设置8位生存时间;trans_protocol状态设置传输层的协议类型,此处设置为0X11,表示UDP协议;trans_check状态时设置16位的首部校验和,其计算方法与UDP协议里面的校验方法类似,都采用二进制反码累加求和的方法;trans_sourceIPaddress状态时添加源IP地址;trans_desIPaddress状态时添加目的IP地址;trans_data状态时开始填充上层数据。

2.3 以太网控制器的设计

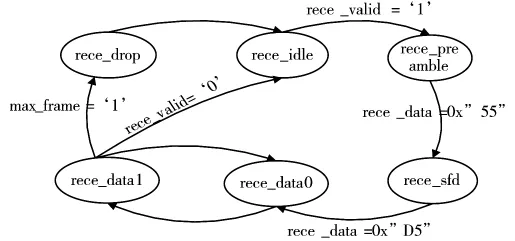

以太网控制器主要用来控制数据在信道上的传输以及把网络层传输过来的数据进行帧格式的封装,并进行半字节数据的拆分,从而与物理层芯片接口相适配以便于在物理通道上进行传输[5]。同样地当接收到来自物理层芯片的数据时,它需要把半字节数据重新合并成一个字节并进行帧头拆封以及数据校验等工作,校验无误后再把链路层以上的数据传递给上层去做进一步的处理。在以太网控制器里面还有一个ARP协议,它要实现IP地址与物理地址的映射,当本地缓存中所存储的映射键值对当中没有所要的IP地址所对应的物理地址时,它需要发送一个包含目的IP地址的ARP请求,ARP应答当中包含目的IP地址所对应的物理地址,收到ARP应答后就可以向所要发送的以太网帧头中添加对应的物理地址了。在本设计中,以太网控制器接收端的工作流程如图6所示。

图6 以太网控制器接收端的状态流程

3 设计验证

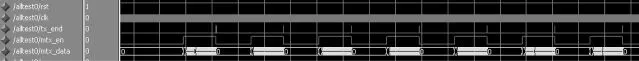

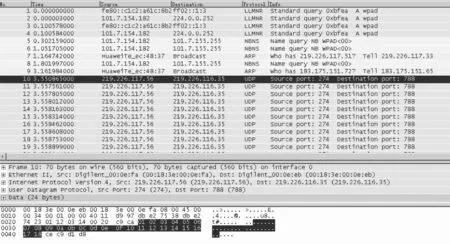

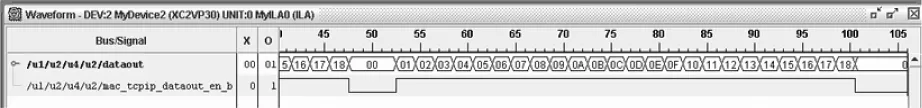

本设计的验证分为仿真验证和上板联网验证。设计阶段采用Xilinx公司的ISE开发软件进行编码设计,设计完成后采用modelsim仿真工具进行仿真,仿真结果表明该协议栈的设计程序能正确完成数据的发送和接收等工作,图7是该协议栈发送端输出的仿真数据。上板联网验证采用Xilinx公司的Virtex-5 FPGA开发板,两块V5板子通过网线同时连接到校内网当中,通过实现两个板子间的相互通信,来验证复杂网络环境下的该可靠UDP协议栈的可靠性。上板联网验证如图8所示。程序在板子上面加载完成后,其中的一块板子A通过网线经由校内网向另一块板子B所在的IP地址发送数据,同时在PC机上面通过wireshark抓包工具来抓取板子A所发送的数据包,抓包结果如图9所示。为了测试FPGA接收端接收到的数据,采用chipscope工具来抓取板子B中的FPGA芯片内部接收到的网络数据,图10为用chipscope抓取到的接收端的数据。抓包结果表明B能正确地接收到A所发送的数据,且没有出现丢包的情况,说明该协议栈能在较复杂的网络环境下正确完整地接收数据,达到了设计要求。

图7 发送端modelsim仿真数据

图8 上板联网验证

图9 发送端wireshark抓包数据

图10 接收端chipscope抓包数据

4 结论

传统的UDP协议不能保证数据在传输过程当中的可靠性,为此本文设计并实现了一个可靠的硬件UDP_IP协议,同时还设计了一个以太网控制器,它与UDP_IP协议一起构成一个完整的通信链路,实验验证结果表明该硬件协议能正确完整地完成网络数据的接收和发送工作,达到了设计的要求。

[1]徐俊.基于FPGA的嵌入式TCP/IP协议栈的实现[D].上海:华东师范大学,2008.

[2]王珏,何秋燕,王露凯.基于UDP改进的可靠传输协议设计[J].电脑知识与技术,2015,11(3):71-73.

[3]ZHANG J F,ZHAN P F,ZHANG G.Ethernet controller and serial interface conversion technology based on FPGA[J].Applied Mechanics and Materials, 2013 (423):2671-2674.

[4]靳海力.具有补发机制的增强型可靠UDP的实现[J].小型微型计算机系统,2010,31(5):904-907.

[5]程鹏,张刚.基于FPGA的10M/100M以太网控制器的设计[J].太原理工大学学报,2008,39(5):27-29.

FPGA Implementation of a Reliable UDP Protocol Stack

LIU Yuan,ZHANG Gang

(School of Information Engineering,Taiyuan University of Technology,Taiyuan 030024,China)

The paper design is based on Xilinx’s development board family of Virtex-5,and it uses hardware description language VHDL as the design language as well as using the concept of modular design,implemented a reliable UDP_IP network communication protocol stack with the function of receipt confirmation and retransmit the missed data which reference TCP_IP stack mechanism.At the same time,an Ethernet controller is designed and implemented,together with UDP_IP protocol,it forms a complete network communication link protocol.After download to the board,it has identified that the communication protocol stack can receive and transmit network data correctly,efficiently and stably.

reliable UDP,communication protocol,FPGA,VHDL

TP302.1

A

10.3969/j.issn.1002-0640.2017.07.030

1002-0640(2017)07-0139-05

2016-05-12

2016-06-29

刘 源(1989- ),男,河南南阳人,硕士研究生。研究方向:Soc集成电路设计。