基于内嵌Cortex-M3内核FPGA的等精度频率计设计

王立华,周松江,2a,高世皓,2b,张 恒

(1.山东科技大学 电子通信与物理学院, 山东 青岛 266590;2.北京邮电大学 a.信息光子学与光通信研究院, b.泛网无线通信教育部重点实验室, 北京 100876)

基于内嵌Cortex-M3内核FPGA的等精度频率计设计

王立华1,周松江1,2a,高世皓1,2b,张 恒1

(1.山东科技大学 电子通信与物理学院, 山东 青岛 266590;2.北京邮电大学 a.信息光子学与光通信研究院, b.泛网无线通信教育部重点实验室, 北京 100876)

为了提高频率计的测量精度和系统性能,解决在传统的频率计中无法实现高低频率等精度测量的情况,采用京微雅格公司的M7系列FPGA,设计了一种基于SOPC技术的等精度多功能频率计。该频率计以内嵌Cortex-M3内核的FPGA芯片为控制核心,通过对FPGA模块和Cortex-M3内核部分的设计,并借助AHB接口的FIFO实现FPGA与Cortex-M3内核之间的数据通信,完成了1Hz~50MHz范围内等精度频率计的设计。通过ModelSim软件仿真和硬件实测表明,该频率计可以完成等精度频率和占空比的测量功能,具有精度高、实时性好等特点。

频率计; 等精度; 可编程片上系统; 现场可编程门阵列; 高性能总线; Cortex-M3

0 引 言

频率是电子领域中最基本的参数,传统的测频方法有直接测量法、周期测量法和分频测量法等,这些方法往往只适用于测量一段频率,而无法实现高低频率等精度的要求。在技术上,传统的频率计大都采用单元电路或单片机进行设计,使频率计存在结构复杂、稳定性差且测量范围小等缺点[1-4]。基于此,本文以京微雅格公司的M7系列FPGA为设计载体,利用SOPC技术和等精度测量原理,在一片内嵌Cortex-M3内核的FPGA芯片上完成频率计的设计。系统充分发挥FPGA的高速数据处理能力,完成对待测信号的测量计数;利用Cortex-M3的数据运算与人机交互能力,完成对测量数据的计算与显示工作。该系统可以实现频率测量和占空比测量功能,具有测量精确、稳定性高、调试方便等特点[5-7]。

1 系统工作原理与结构

1.1等精度测量原理

等精度测量法的测量原理如图1所示,其最大的特点是实际闸门时间并不是一个固定值,而是一个与被测信号有关的值,且刚好为被测信号周期的整数倍。在启动测量之后,首先给出一个预置闸门时间,然后等待被测信号下一个上升沿的到来。当被测信号的上升沿到达后,将预置闸门时间信号与被测信号进行同步,同时用两个计数器分别对被测信号和标准信号进行计数。当预置闸门时间结束后,被测信号的下一个上升沿到达时两个计数器停止计数。此时会得到两个计数值,然后结合标准信号的频率值,即可得到被测信号的频率[8-10]。

图1 等精度测频法测频原理图

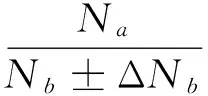

假设在一次测量中,实际闸门时间为T,被测信号计数器和标准信号计数器的计数值分别为Na和Nb,标准信号的频率为f0,根据测量原理可计算出被测信号的频率为:

f=(Na/Nb)f0

(1)

式中:f为被测信号频率的测量值,若信号的实际频率为f′,则测量误差为:

(2)

若忽略标准信号的频率误差,并根据式(1),可得被测信号实际频率的表达式为:

(3)

联立式(1)~(3)可得:

(4)

由此可知,采用等精度测量法测量频率时,所选择的闸门时间越长,标准信号的频率越高,频率测量的误差就会越小[11-14]。假设标准信号的频率为100 MHz,闸门时间为1 s,那么其精度可达到10-8。

另外,占空比的测量方式描述如下:在对闸门时间内标准信号进行计数的同时,还需要对在闸门时间内被测信号高电平时间段的标准信号进行计数[15]。设两个计数器的计数值分别为Nb和Nc,那么可得到被测信号的占空比为[16]:

D=(Nc/Nb)×100%

(5)

1.2系统总体结构

频率计系统的总体结构图如图2所示。本系统选用京微雅格公司M7系列的FPGA芯片CME-M7A12N0F484C7,该芯片集成了主流的ARM Cortex-M3内核和高性能FPGA逻辑单元,FPGA逻辑性能高达200 MHz,而ARM Cortex-M3内核最大频率可达300 MHz。利用AHB(Advanced High performance Bus)总线连接FPGA、ARM Cortex-M3内核和各个外设,实现了高速数据传输。

图2 系统总体结构图

在图2所示的系统中,锁相环IP核部分用来产生各类时钟信号,AHB接口的FIFO IP核作为FPGA与Cortex-M3内核之间通信的中介。而具有人机交互优势的Cortex-M3内核通过GPIO来输入外部信号以及控制LCD12864进行显示。同时数据通过UART传输至电脑端的上位机软件,用于系统设计与调试。

哪有天天不舒服的?这分明是在找借口逃课嘛!可是,看着妍妍紧皱的眉头、苍白的嘴唇和痛苦不堪的表情,又确实不像装的。

1.3系统工作原理

在图2所示系统中,时钟信号(clk)进入锁相环电路后产生多个高频时钟信号用于各个FPGA模块和Cortex-M3内核工作。被测信号(signal)输入至频率占空比一体化测量模块中进行测量并产生测量数据(Na、Nb和Nc)和数据有效信号(valid),然后利用FPGA写FIFO控制模块将测量数据按照时序要求写入到AHB接口的FIFO中,在每次写完数据之后产生一个写完成信号(w_done_f),并通过一个IO口输出。系统的Cortex-M3内核中有一个32位的GPIO,其中有一位与写完成信号(w_done_f)相连。当Cortex-M3检测到写完成信号后,利用AHB系统总线读取FIFO中的数据,然后对读取的数据进行运算得到被测信号的频率值和占空比值,利用UART将数据传输至电脑端的上位机,并通过GPIO来控制外部LCD12864显示器进行显示。

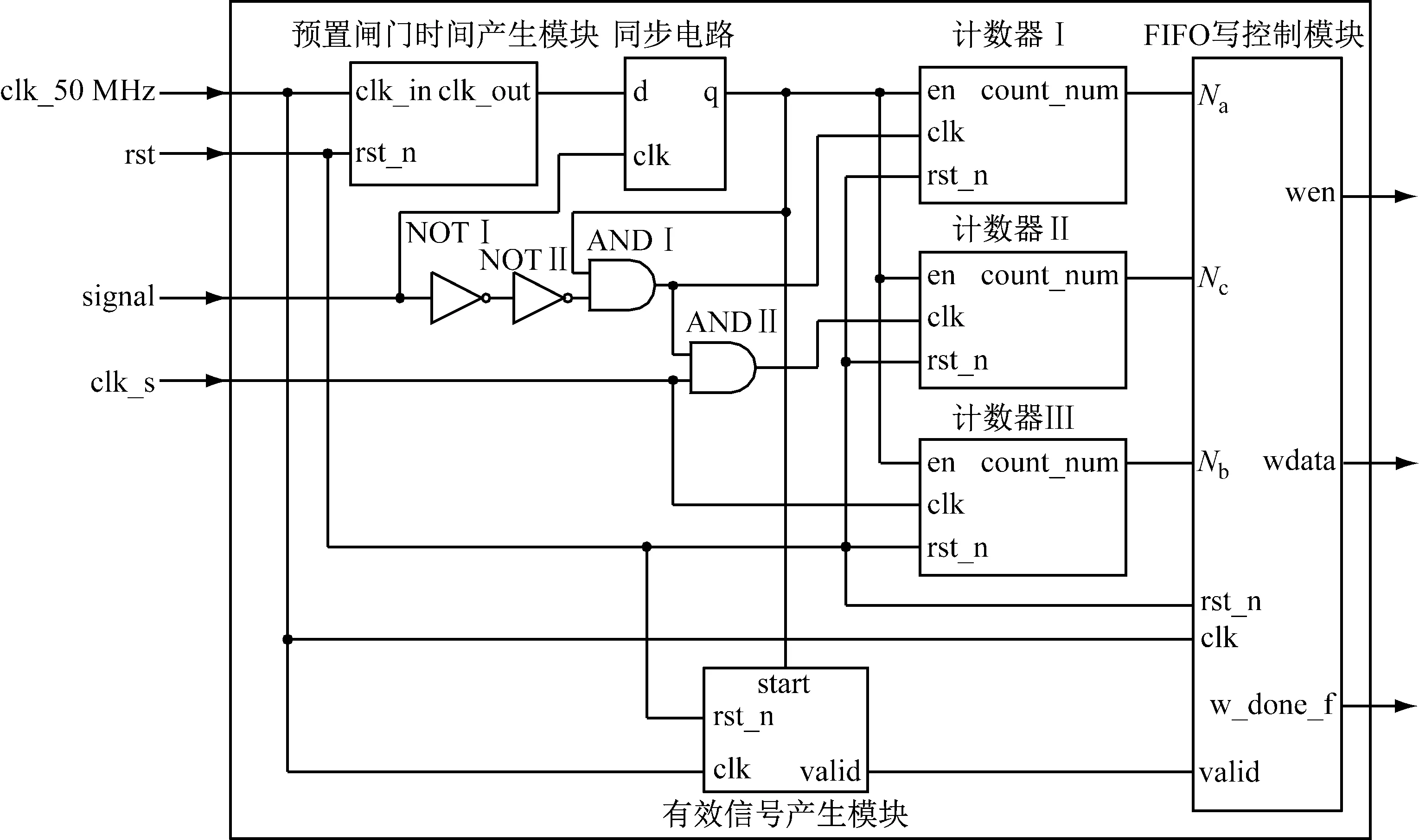

2 FPGA模块设计

图2所示系统中的FPGA部分主要用于完成频率和占空比的测量工作,其一体化设计结构图如图3所示,主要由5个部分构成,分别是预置闸门时间产生模块、同步电路、计数器模块、有效信号产生模块和FIFO写控制模块。在图3中,clk_50MHz为时钟信号输入端,rst为复位信号输入端,signal为被测信号输入端,clk_S为标准信号输入端,Na、Nb和Nc为3个计数器的计数值,valid为数据有效信号,wen为FIFO写使能信号输出端,wdata为FIFO写数据输出端,w_done_f为写完成信号输出端。

图3 测频、测占空比一体化设计结构图

2.1预置闸门时间产生模块

预置闸门时间产生模块内部是一个分频电路,将输入的时钟信号(clk_in)分频产生频率为2 Hz的时钟信号,通过时钟输出端(clk_out)输出,并将其高电平时间段作为预置闸门时间,其时间长度正好为1 s。

2.2同步电路

图3中的同步电路是一个D触发器。在该系统中,为了测量的准确性,需要保证实际闸门时间为被测信号周期的整数倍,因此本系统利用D触发器的同步功能,将被测信号作为同步电路的时钟输入端,预置闸门时间信号作为同步电路的D输入端,这样其输出即为与被测信号同步的实际闸门时间。

另外,为了能够测量信号的占空比,系统采用门电路的方式,将实际闸门时间信号与被测信号相“与”(AND I),其输出作为被测信号的计数信号,同时将其与标准时钟信号相“与”(AND II),得到闸门时间内被测信号高电平时间段标准信号的计数信号。系统中两个非门(NOT I与NOT II)起到微延时的作用,使系统工作更加稳定,测量更加准确,其本身对信号的逻辑关系没有任何影响。

2.3计数器模块

图3系统中有3个计数器模块,其工作原理描述如下:当计数使能端(en)上升沿到达时,计数器开始对由clk端输入的信号进行计数,而计数使能端(en)下降沿到达后停止计数,同时将计数值锁存并通过count_num端输出,然后将计数器内部计数值清零,以用于下一次计数。

在该系统中,需要对闸门时间内各个信号的个数进行计数,所以将实际闸门时间信号(同步电路的输出信号)作为3个计数器的计数使能信号。3个计数器中,计数器I用于对被测信号进行计数,计数器II用于对被测信号高电平时间段的标准信号进行计数,计数器III用于对标准信号进行计数。根据测量原理,假设闸门时间内3个计数器的计数值分别为Na、Nc和Nb,标准信号的频率为f0,那么可得被测信号的频率为:

f=(Na/Nb)f0

(6)

D=(Nc/Nb)×100%

(7)

2.4有效信号产生模块

图3中,有效信号产生模块是在每次测量完成产生新的数据之后,将其输出端(valid)置高。该模块利用实际闸门时间信号来产生输出信号,若实际闸门时间信号为高,此时正处于测量过程中,该模块的输出(valid)为低;当实际闸门时间信号变为低之后,数据测量完成,此时将模块的输出(valid)置为高电平。利用该信号可以控制FIFO写控制模块每次将有效的数据写进FIFO。

2.5FIFO写控制模块

FIFO写控制模块的输入信号有时钟信号(clk)、复位信号(rst_n)、3个测量数据(Na、Nb和Nc)和数据有效信号(valid),模块的输出信号为FIFO写使能信号(wen)、FIFO写数据信号(wdata)和写完成信号(w_done_f)。该模块就是根据FIFO写数据的时序,在数据有效(valid为高)之后将测量所得的数据依次写进FIFO中进行缓存,在写完之后将写完成信号(w_done_f)置高。如果检测到数据有效信号(valid)为低,则将写完成信号(w_done_f)置低。

3 系统软件设计

本文所设计的频率计是利用FPGA内嵌的Cortex-M3内核完成数据的接收、处理和显示工作,在Keil开发平台下利用C语言对系统软件进行设计。系统软件的程序流程图如图4所示。

系统开始运行后,首先进行系统初始化,包括初始化串口、初始化GPIO和初始化LCD12864等。之后系统就进入了主循环,首先检测写完成信号是否有效,如果无效则一直循环检测,当写完成信号有效之后则停止检测,按照顺序依次读取FIFO地址下的3个数据,然后按照公式计算出被测信号的频率值和占空比值。接下来系统控制串口将数据传输至电脑,并利用GPIO控制外部LCD12864对测量结果进行显示。当上述工作全部完成之后,再次检测写完成信号,如果其仍然有效,则一直循环检测此信号,直到其无效为止,然后回到主循环开始处,执行下一次循环。

图4 系统软件程序流程图

4 实验结果

4.1FPGA模块仿真

根据等精度测量的原理和FPGA模块结构设计,利用Verilog硬件描述语言对测频、测占空比一体化设计结构进行设计,并利用ModelSim软件对其整体进行功能仿真。如图5、6所示为频率计的整体仿真结果,其中测试信号的频率是5 Hz,占空比为80%。由图5可见,预置闸门时间、被测信号和实际闸门时间等信号的时序与等精度测量原理图相一致,同时测量所得的3个计数值准确,与测试信号的频率、占空比相符。从图6中可以看出,FIFO写控制模块按照时序要求将测量所得的3个数据依次输出至FIFO中,同时在写完成之后将写完成标志置高。

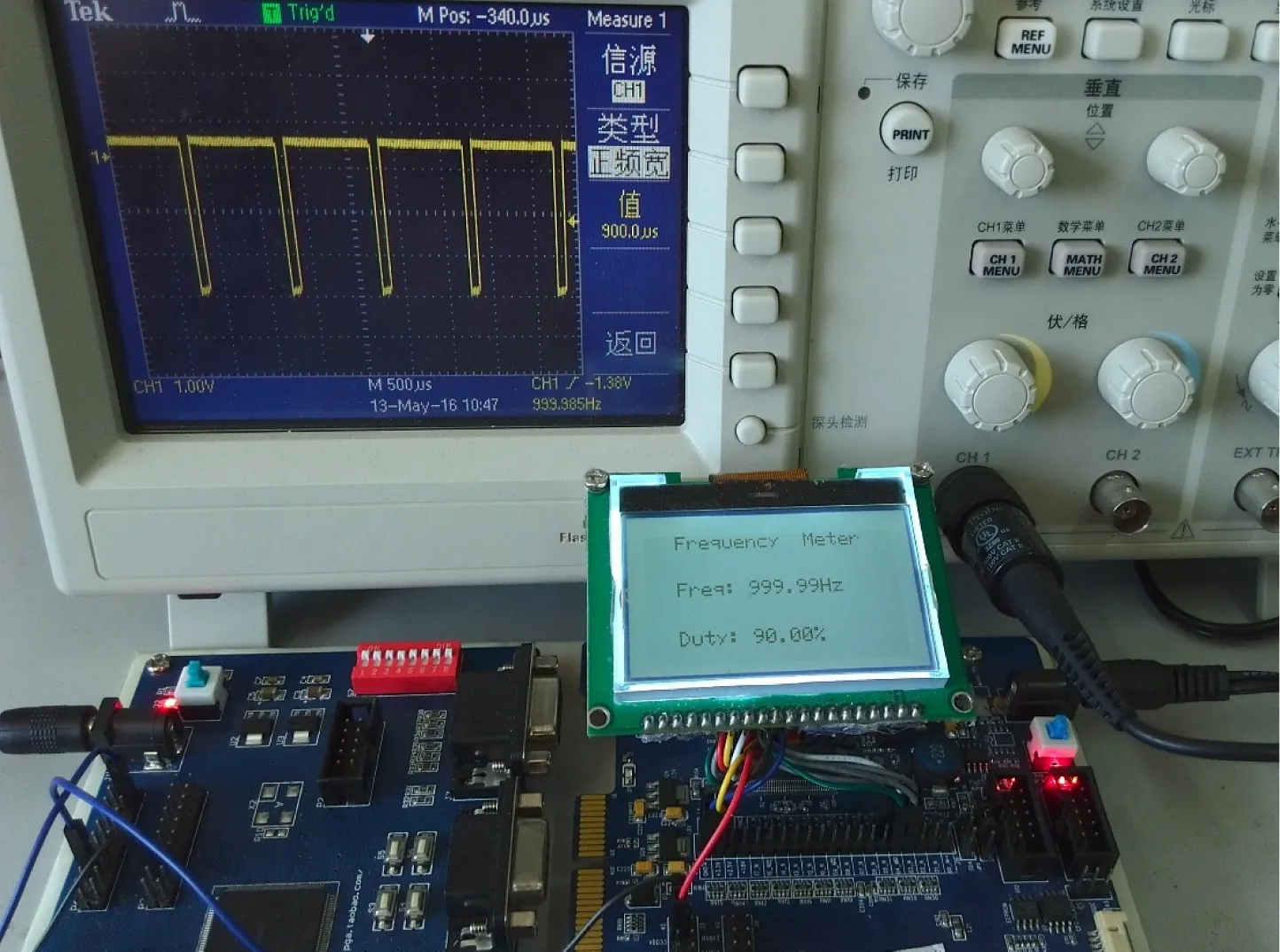

4.2硬件实现与测试

利用Keil软件完成Cortex-M3内核软件的设计工作,并将其产生的HEX文件导入京微雅格的EDA设计工具Primace中,与所设计的FPGA模块一并生成比特流数据,并将其下载至M7开发板中,按照设计结构将外部引脚进行连接,即完成了频率计系统的硬件实现。该频率计利用LCD12864对测试结果进行显示,采用自动量程的方式,无需人工调整。

利用本文所设计的频率计对测试信号的频率和占空比进行测试,然后对结果进行分析,图7所示为系统测试图。

图5 频率计整体仿真结果

图6 FIFO写控制模块仿真结果

图7 系统测试图

表1是本频率计的一组测试数据,通过对被测信号的频率、占空比和测试所得的频率值和占空比值相比较可知,在所给的测量范围之内,频率测量误差均小于10-4,占空比测量误差的绝对值均小于10-2。测量结果的误差分布在同一个数量级,并没有因为频率值的变化而变化,从而达到了等精度测量的目的。

表1 频率计系统实验测试数据

5 结 语

本文以京微雅格公司的M7系列FPGA为设计载体,利用SOPC技术和等精度测量原理,在一片内嵌Cortex-M3内核的FPGA芯片上完成了频率计的设计,可以实现频率测量和占空比测量功能。利用Verilog硬件描述语言完成FPGA模块的设计,并利用ModelSim软件对其进行仿真验证。通过Keil软件完成Cortex-M3内核的软件设计,利用Primace工具进行分析、综合,并最终下载到芯片中,完成系统的硬件实现。通过实际测试,系统可以很好地完成频率测量与占空比测量功能,并达到了等精度测量的目的。

[1] 张 博,曹学沿,房 亮.基于VHDL的简易数字频率计的设计[J].传感器世界,2013(5):29-34.

[2] 陈尚志,胡荣强,胡合松.基于FPGA自适应数字频率计的设计[J].中国测试技术,2007,33(2):141-144.

[3] 曹浩彤,刘 艳.基于430单片机的简易频率计设计[J].微型机与应用,2014,33(21):92-94.

[4] 谢尚港,王佳豪,黄继业.基于FPGA移相倍频方式的频率计设计与实现[J].自动化与仪器仪表,2016(4):29-31.

[5] NING Zehong,XU Dawang,DONG Zhanyong.Frequency measurement technique based on frequency conversion[J].Journal of Measurement Science and Instrumentation,2013,4(2): 146-149.

[6] 郝统关,程 明.基于FPGA Nios II的等精度频率计设计[J].电测与仪表,2009,46(2):56-58.

[7] 黎山峰,杨 雷,孙建军.基于NiosⅡ的FPGA频率计设计与实现[J].仪表技术与传感器,2016(8):105-108,112.

[8] 黄 俊,余水宝.基于STC12C5A60S2的高频高精度频率计的设计[J].微型机与应用,2012,31(17):22-24.

[9] 曹作宝,包晓敏,彭 霄.基于NIOS II的多功能数字频率计的设计[J].工业控制计算机,2009(10):74-75.

[10] DU Baoqiang,WANG Yanfeng,CUI Guangzhao,etal.High-precision time and frequency measurement method combining time-space conversion and different frequency phase detection[J].Science China(Physics,Mechanics & Astronomy),2013,56(11): 2110-2115.

[11] Fang Yiyuan,Chen Xuejun.Design of equal precision frequency meter based on FPGA[J].Engineering,2012,4 (10): 696-700.

[12] 王 慧.基于FPGA高速高精度频率测量系统的实现[J].传感器世界,2006(1):27-29.

[13] 李鑫彪,王笑怡.基于FPGA的频率测量仪设计[J].微处理机,2014(10):5-7.

[14] 井新宇.基于SOPC的FPGA Nios II嵌入式等精度频率计设计[J].实验室研究与探索,2012,31(6):217-220.

[15] 许可行,刘延飞,羊 帆.基于多周期同步测量的频率计设计[J].国外电子测量技术,2016(9):76-80.

[16] 谢尚港,王佳豪,黄继业.基于FPGA移相倍频方式的频率计设计与实现 [J].自动化与仪器仪表,2016(4): 29-31.

Design of Equal Precision Frequency Meter Based on FPGA with Embedded Cortex-M3 Core

WANGLihua1,ZHOUSongjiang1,2a,GAOShihao1,2b,ZHANGHeng1

(1.School of Electronic Communication & Physics,Shandong University of Science & Technology,Qingdao 266590,Shandong,China; 2a.Institute of Information Photonics and Optical Communication,2b.Key Laboratory of Universal Wireless Communications,Ministry of Education,Beijing University of Posts and Telecommunications,Beijing 100876,China)

In order to solve the problem that the traditional frequency meter cannot achieve equal precision in high or low frequency measurement,improve the precision and performance of frequency meter,an equal precision frequency meter based on SOPC is designed in this paper.An FPGA chip that is embedded with Cortex-M3 as the system’s controlling core,through the design of FPGA module and Cortex-M3 module,data communication between FPGA and Cortex-M3 is achieved by FIFO with AHB interface.The device completes the design of equal precision frequency meter in 1Hz~50MHz range.By ModelSim software simulation and hardware testing,the frequency meter can complete equal precision frequency and has duty ratio measuring function,and has the characteristics of high precision and good real-time.

frequency meter; equal precision; system-on-a-programmable chip (SOPC); field-programmable gate array (FPGA); advanced high performance bus (AHB); Cortex-M3

2016-11-10

王立华(1971-),男,山东潍坊人,副教授,硕士生导师,主要从事嵌入式应用、光伏发电技术和通信技术的教学与研究。

Tel.:13730917192;E-mail:wanglihua7141@126.com

TM 935.13

:A

1006-7167(2017)07-0139-05