一种触发型ESD电源钳位电路

李若飞

(中国电子科技集团公司第四十七研究所,沈阳110032)

一种触发型ESD电源钳位电路

李若飞

(中国电子科技集团公司第四十七研究所,沈阳110032)

ESD电源钳位的应用始于20世纪90年代中期,到现在它已经成为半导体芯片设计及ESD设计综合的典型应用。将ESD电源钳位综合应用到半导体芯片结构中的发展已经成为ESD设计规则的组成部分,同时也是ESD设计艺术的基本组成部分。在CMOS工艺中,MOSFET型ESD电源钳位在芯片设计中已经成为一种标准的ESD设计实现。触发型MOSFET ESD电源钳位电路能够弥补栅极接地的NMOS(GGNMOS)在经受二次击穿时的ESD保护缺陷。

MOSFET工艺;ESD电源钳位;RC触发ESD电源钳位;ESD电源钳位频率;电压触发ESD电源钳位;主/从ESD系统

1 引言

在IC(集成电路)工业中,ESD(Electro-Static Discharge,静电放电)是影响IC芯片可靠性的主要因素之一[1]。电源轨之间的ESD电源钳位是静电放电的研究领域之一。ESD电源钳位在20世纪90年代广泛流行,并在半导体芯片方面取得了很好的ESD成果[2]。从1995年至2005年,ESD MOSFET电源钳位的研究重点已转移到生产性能较好的ESD电源钳位、集成设计、物理布局和低泄漏电流方面。ESD电源钳位达到了功能上和ESD相类似的优势。

2 ESD电源钳位设计

ESD电源钳位是通过建立在半导体芯片上为ESD电流建立的额外电流环路,使得电流从ESD元件向芯片的电源轨和地面流动。ESD电源钳位的存在可以减少通过电流回路的阻抗,这样既提高轨到轨的ESD保护也改善引脚到轨的ESD效果。为防止ESD钳位单元在达到防护功能之前就出现失效,ESD电源钳位单元的钳位元件必须确保工作在该元件最大绝对电压值和最大绝对电流值之下。

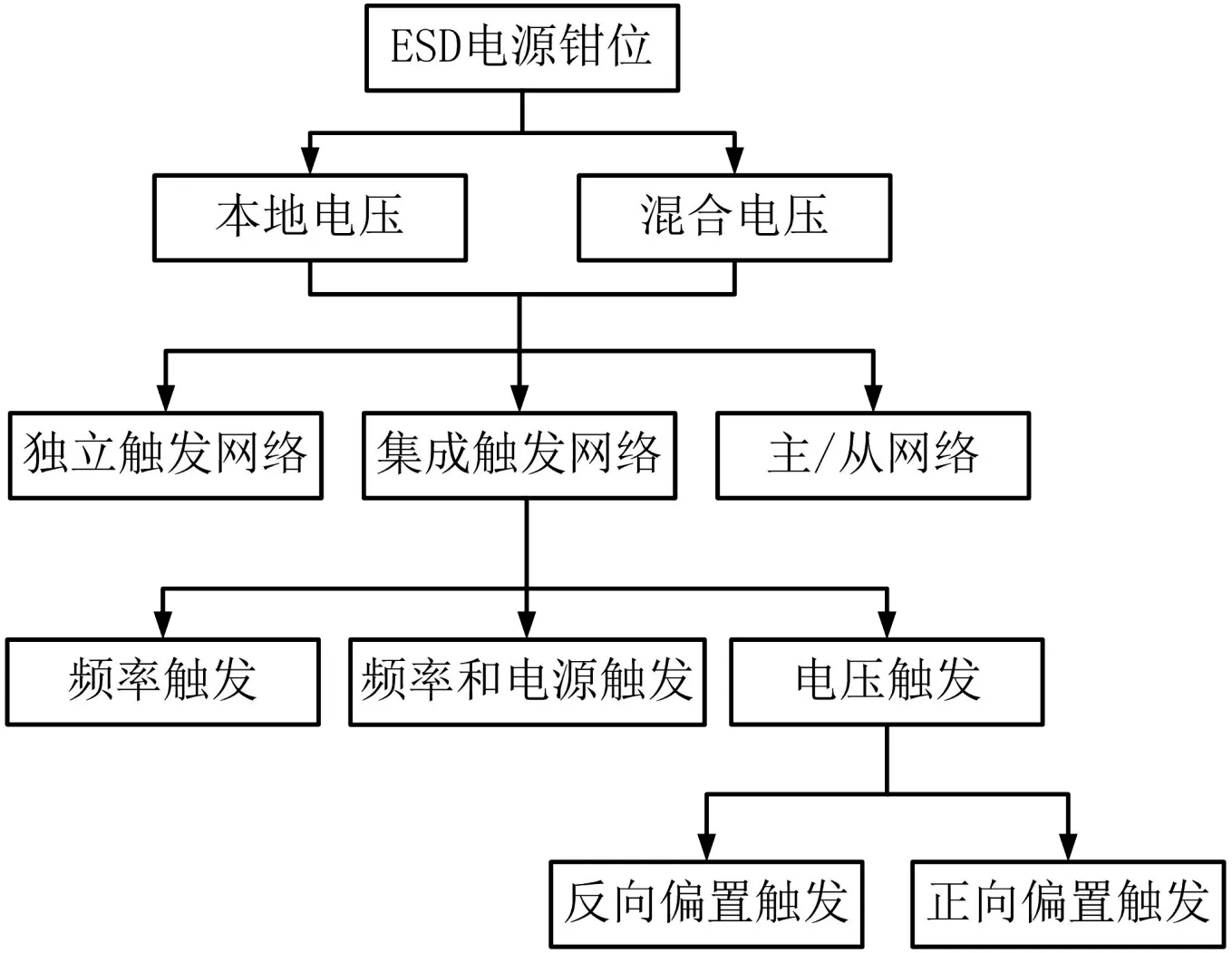

ESD电源钳位有多种不同类型,从概念上来说可以被分为几个不同的种类。如图1所示为一个ESD电源钳位分类图。

ESD电源钳位包含两个基本特征:①ESD电流从电源网络的一部分传送到电源网络的另一部分;②ESD电源钳位的开启,一般称之为“触发”状态。ESD电源钳位可以是一个简单的物理器件,或者是一个复杂电路,也可以是一个系统[3]。现有的ESD电源钳位中,具有针对ESD脉冲而响应的触发特性,该触发特征既可以通过瞬态响应也可以通过电压的电平响应。

图1 ESD电源钳位的分类

3 R C触发ESD钳位

在ESD电源钳位中,瞬时响应频率触发是为响应ESD事件而设计的触发元件。该触发元件可以是一个频率触发网络也可以是一个瞬时响应触发元件,此类触发网络称为“频率触发”。频率触发网络的优点是它们不依赖于开启电压。电源触发ESD电源钳位在达到一定直流电压之前会有一定的延时。频率触发ESD电源钳位是交流响应的,而不是直流电压水平。

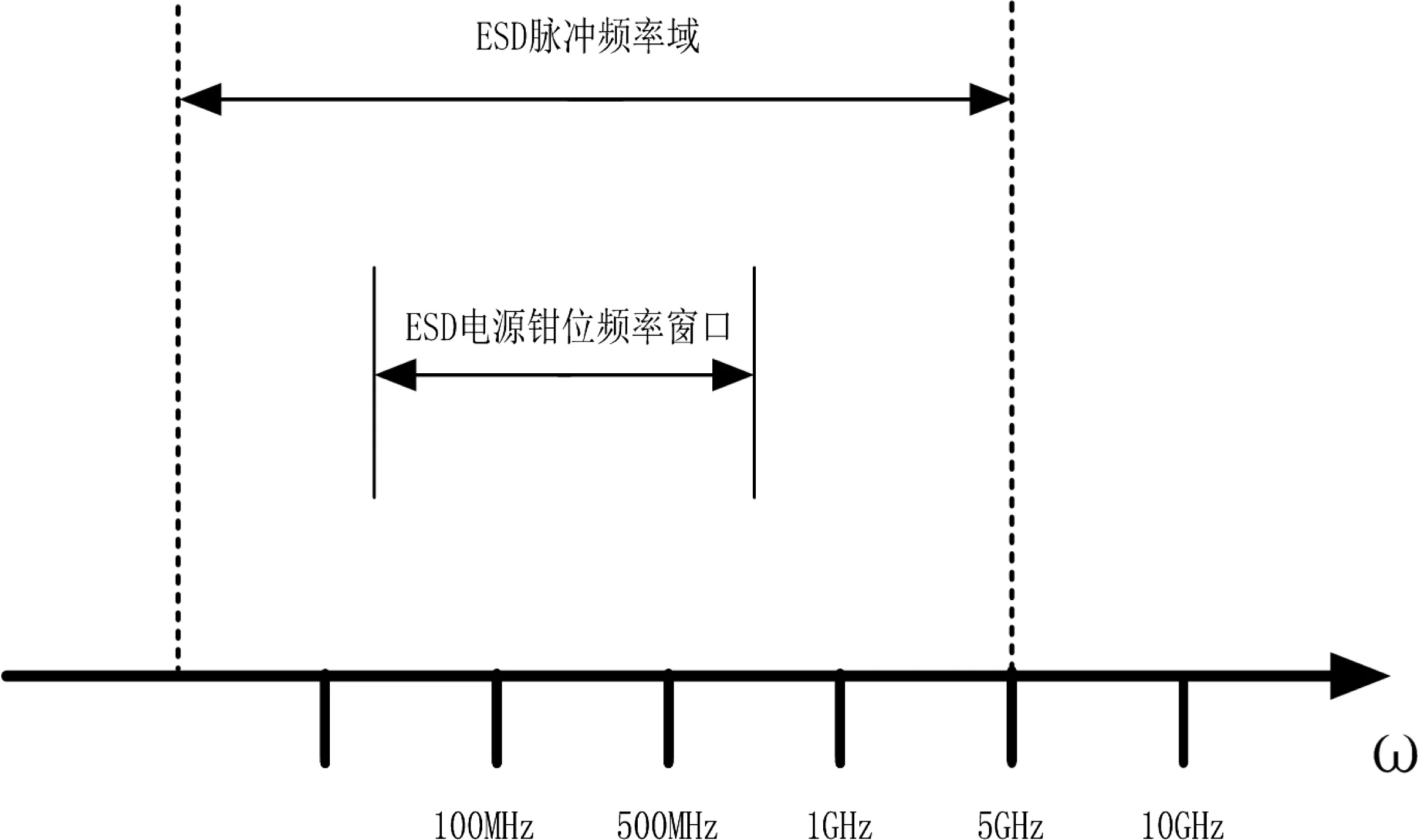

一般来说,ESD电源钳位是针对HBM事件和MM事件的响应而设计,而不是针对CDM事件的响应而设计。ESD电源钳位一般不会因为半导体芯片或系统中电源的上电和断电而开启,使得ESD电源钳位不会因系统事件触发而导致“误触发”[4],。另外,对于RF电路,ESD触发元件将不会对RF应用频率进行响应[5]。因此,需要定义一个频率窗口以适应ESD电源钳位及这些网络的频率范围,如图2所示为ESD电源钳位频率窗口。

RC触发MOSFET基本的元件缩小与每一代工艺技术成比例,并与数字COMS电路兼容。有了这种按比例缩小的ESD解决方案,技术工艺上的设计迁移或设计上的“缩小”都十分简便。

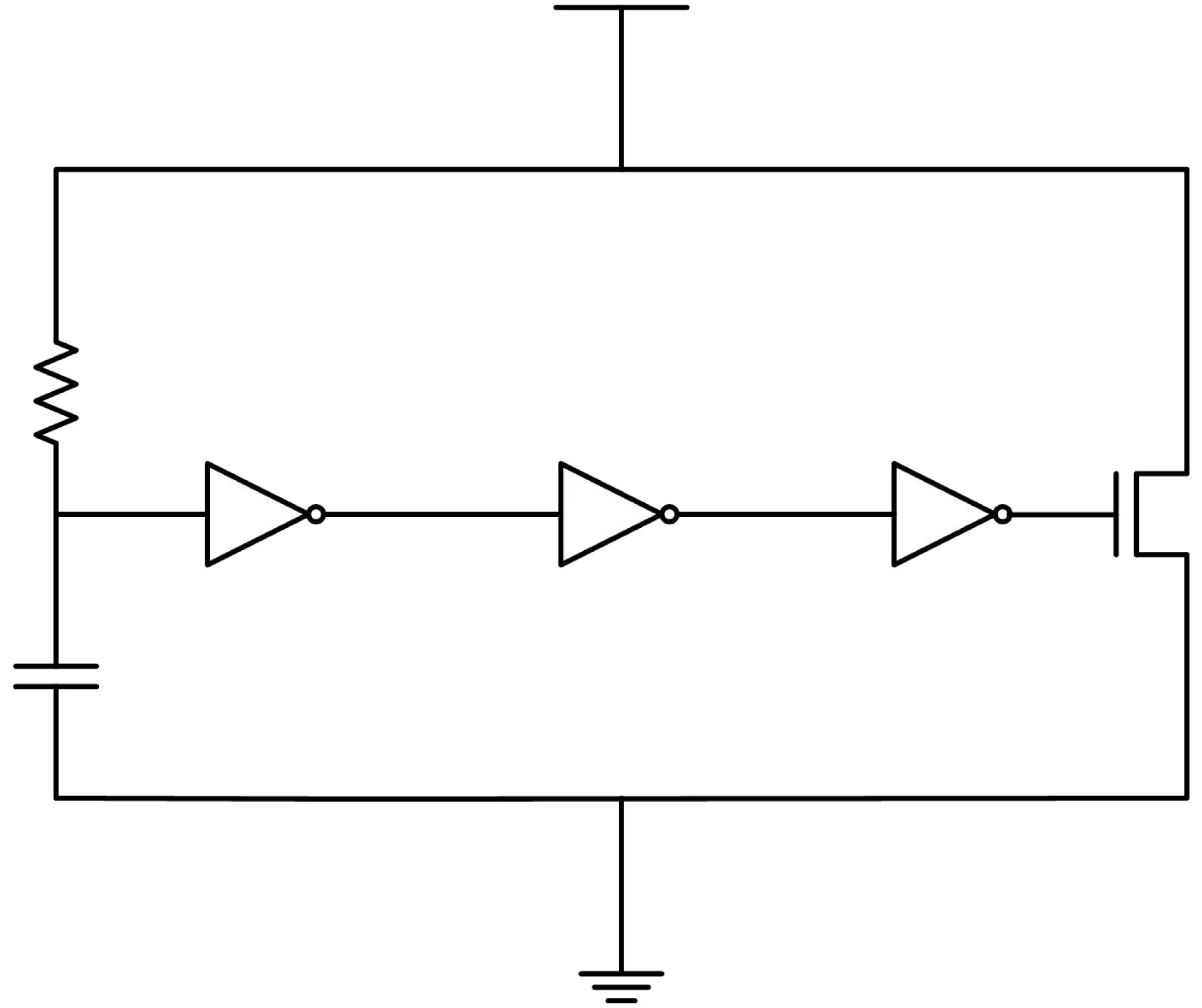

RC触发ESD电源钳位包含三部分:RC频率辨别电路、反相器驱动电路、MOSFET输出钳位元件。

在RC频率辨别电路中,需要电阻和电容元件来形成RC鉴别网络。反相器驱动电路是在RC鉴别器网络电路和MOSFET输出钳位单元间用一系列的反相元件组成的。其作用是输出钳位分离出频率辨别电路和驱动输出钳位MOSFET栅电压[6]。如无反相器驱动级,则MOSFET钳位的输出电容将与电容元件并联,使得MOSFET输出钳位的电容影响响应频率。

图2 ESD电源钳位频率窗口

如图3所示为一个RC触发MOSFET电源钳位电路。一个MOSFET和电容元件作为RC鉴别电路。ESD脉冲激活RC鉴别装置,这一信号传送给反相级以驱动MOSFET泄放ESD电流。在这种设计中调整反相器尺寸是为了避免RC误触发而设计的。

图3RC触发MOSFET ESD电源钳位模块

4 改进型R C触发电源钳位电路

在普通的RC触发型电源钳位电路中电阻和电容既要负责做为电路的ESD冲击检测元件,又要做为泄放晶体管开启足够时间的延迟,所以单独的RC电路需要的面积相对较大。在保证泄放晶体管开始时间的同时也保证在正常上电时其关闭的足够好,以避免不必要的漏电。

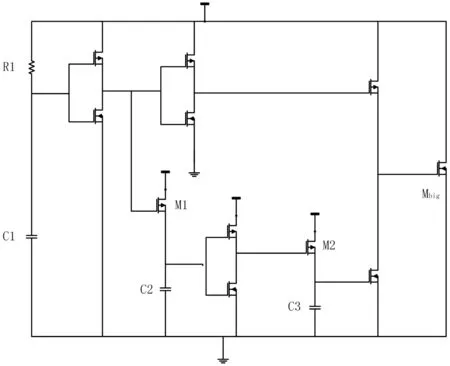

如图4所示为一种RC触发型电源钳位ESD保护电路,采用把泄放晶体管的开启和关断通路进行分开设计的方法[7]。该设计中,泄放晶体管的开启时间主要由泄放晶体管的关断通路延迟时间决定,这样就可以使得探测ESD冲击作用的电容(C1)和电阻(R1)在设计时有所减小,同时电路版图的面积也得到了相应减小。在防止电路快速上电时被误触发的能力上也得到了增强,即便泄放晶体管被一个快速上电电压误触发,保护电路也会在关断通路一定的延迟时间之后脱离误触发状态,从而有效避免 了闩锁问题[8]。

图4 RC触发型电源钳位ESD保护电路

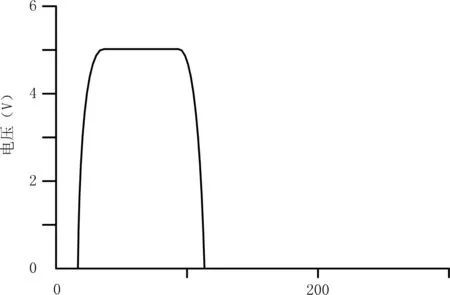

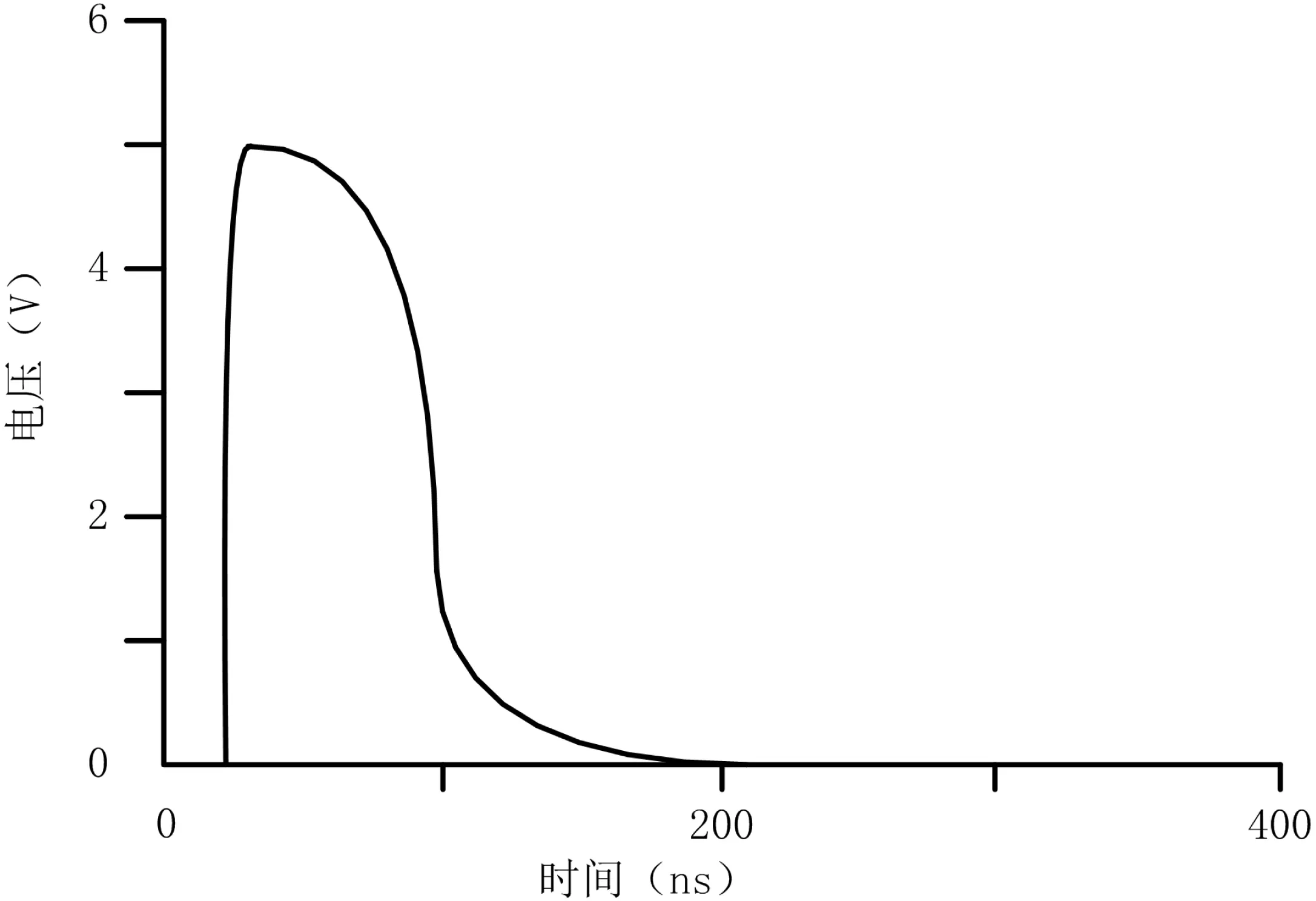

在该设计中,泄放晶体管的开启时间是由其关断通路的等效RC延迟来决定的。当ESD冲击来临时,泄放晶体管开启时间越长,对保护电路自身的可靠性越好。通过调节M1、C2及M2、C3所构成的两级RC结构达到与ESD冲击探测电阻电容结构同样大小的等效时间常数。如图5为泄放晶体管(Mbig)栅电压随时间变化波形图、如图6为电路输出电压随时间变化波形图。

图5 泄放晶体管栅电压随时间变化波形图

图6 电路输出电压随时间变化波形图

5 结束语

集成电路芯片的ESD防护设计是保证芯片能够正常工作的必备条件之一,芯片设计者需要为芯片设计一个有效的防静电冲击机制,在ESD事件发生时能够把冲击带来的静电电荷放掉。而既要保证内部功能电路的正常工作,又要让钳位电路占据恰当的芯片面积,从而在防护性能和防护成本之间找到一个最好的折中点一直是芯片设计者努力的方向。

[1]EA Amerasekera,C Duvvury.ESD in Silicon Integrated Circuits[J].J Wiley,1995,9(5):208.

[2]WD Mack,RG Meyer.NewESD protection schemes for BiCMOS Processes with application to cellular radio designs[J]. IEEE International Symposium on Circuits and Systems, 1992(6):2699-2702.

[3]JC Bernier,GD Croft,WR Young.A process independent ESD design methodology[J].IEEE International Symposium on Circuits&Systems,1999(1):218-221.

[4]SH.Voldman.ESD:RF Technology,and Circuits[M].Chichester,UK:John Wileyand Sons,Ltd,2006-10.

[5]VA Vashchenko,A Shibkov.ESD Design for Analog Circuits [M].NewYork:Springer,2010.

[6]Steven H Voldman.ESD:physics and Devices[M].Chichester,UK:John Wileyand Sons,Ltd,2004.

[7]M Stockinger,JW Miller.Advanced ESD rail clamp network design for high voltage CMOS applications[J].Proceedings of the Electrical Overstress/Electrostatic Discharge(EOS/ESD) Symposium,2004:1-9.

[8]PCF Tong,W Chen,RHC Jiang,J Hui.Active ESD shunt with transistor feedback to reduce latchup susceptibility or false triggering[J].Proceedings ofthe IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits(IPFA),2004(2):89-92.

A Trigger Circuit of ESD Power Clamp

Li Ruofei

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

ESD power clamp is used in the middle of 1990s,and it has become a typical application in the design of semiconductor chip and ESD.The ESD power clamp applied to the semiconductor structure has become the components of ESD design rules and ESD design art.In CMOS technology,ESD power clamp using MOSFET becomes a standard ESD realization.ESD power clamp using MOSFET trigger can help GGNMOS perform circuit protect against the second breakdown shock.

MOSFET technology;ESD(Electro-Static Discharge)power clamp;RC trigger ESD power clamp;ESD power clamp frequency;Voltage triggering ESD power clamp;Master-slave ESD system

10.3969/j.issn.1002-2279.2017.02.005

TN402

A

1002-2279-(2017)02-0019-03

李若飞(1984-),男,辽宁省沈阳市人,工程师,主研方向:集成电路设计。

2016-06-15