基于Zynq—7000的多种以太网实现方案

刘佳+钱瑞杰+李洋

摘 要:Zynq是Xilinx公司推出的第一个可扩展处理平台,将双核ARMCortex A9處理器与可编程逻辑架构结合,充分体现软硬件协同设计。以太网是当今通信领域广泛应用的接口,在Zynq中提供了两路千兆以太网控制器,结合MIO、EMIO、AXI、PL等资源,可提供多种以太网实现方案。

关键词:Zynq可扩展处理平台;软硬件协同设计;以太网

中图分类号:TP391.41 文献标识码:A 文章编号:1671-2064(2017)09-0040-02

1 引言

随着技术的发展,SOC受到了更多人的关注和推行,Xilinx公司的Zynq作为该领域的领跑者,已被运用到许多场合。Zynq-7000 系列基于 Xilinx 的可扩展处理平台结构,在单芯片内集成了具有丰富特点的双核 ARM Cortex A9处理器系统(Processing System,PS)和 Xilinx可编程逻辑(Programmable Logic,PL)。其中,Cortex A9 双核处理器是整个架构的核心,外部存储器接口、及丰富的外设资源都挂载在 ARM上,PL可看做完全可编程的外设。

本文基于以太网接口的大量使用,充分考虑到不同应用场景接口形态的差异,如光口以太网、电口以太网。结合Zynq所具备的丰富设计资源,提出了基于Zynq-7000的多种以太网实现方案。

2 方案原理

Zynq-7000内部有很多常见的I/O外设和存储器接口,是PS的重要组成部分。这些外设包括GPIO、USB控制器、SPI控制器、UART控制器、千兆以太网控制器等。这些外设除具备通用功能外,还针对Zynq-7000做了改动。使其能很好的支持PS+PL的架构,灵活使用PL。

Zynq-7000中还提出了两个新概念,MIO(Multiuse I/O)和EMIO(Extendable Multiplexed I/O)。MIO是PS的IO接口,共有54个引脚,这些引脚可用在GPIO、USB、SPI、Ethernet等功能上。EMIO主要是将MIO上放不下,而又想使用的IO接口连接到PL上,再从PL的引脚连接到芯片外。

常用的以太网接口通常是MAC+物理PHY的形式,外接RJ45插头,实现GE_T模式的电口应用。也有MAC+Serdes PHY的形式,外连光纤,实现GE_BX模式的光口应用。

Zynq-7000 PS部分包含了两个千兆以太网MAC层硬核,因此还需要一个以太网物理层传输芯片或光模块实现千兆以太网接口。MAC层硬核所对应的接口引脚,既可以从PS端的MIO连出,也可以通过EMIO从PL连出。综合以上,本文提出了多种以太网实现方案。

3 具体实现

3.1 双电口以太网(MIO)

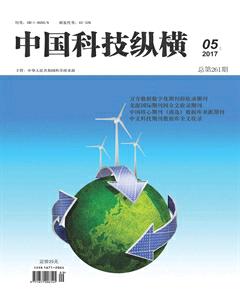

两个千兆以太网控制器,都使用MIO,共用MDC和MDIO管脚,从PS端出。分别外接Marvell 88e1518物理PHY。如图1所示。

此种方式,两个控制器必须共用MDC和MDIO,MD Bus上最多可以挂在32个物理PHY,通过PHY地址的不同进行识别。图中选用Ethernet Controller 0的MD Bus,也可以选择Ethernet Controller 1的MD Bus。

3.2 双电口以太网(MIO+EMIO)

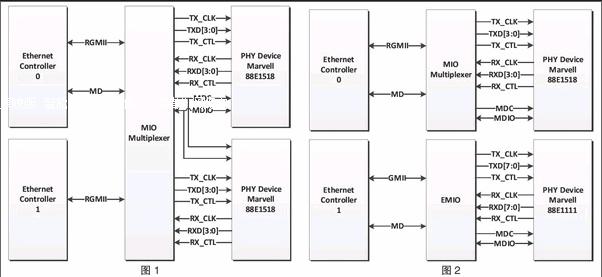

千兆以太网控制器0使用MIO,从PS端出,外接Marvell 88e1518物理PHY。千兆以太网控制器1使用EMIO,从PL端出,外接Marvell 88e1111物理PHY。如图2所示。

此种方式下,从EMIO出的PHY要注意电平标准,要根据PL管脚电平选择相匹配的PHY。并且,从EMIO出时,只支持GMII模式。

3.3 电口以太网+光口以太网

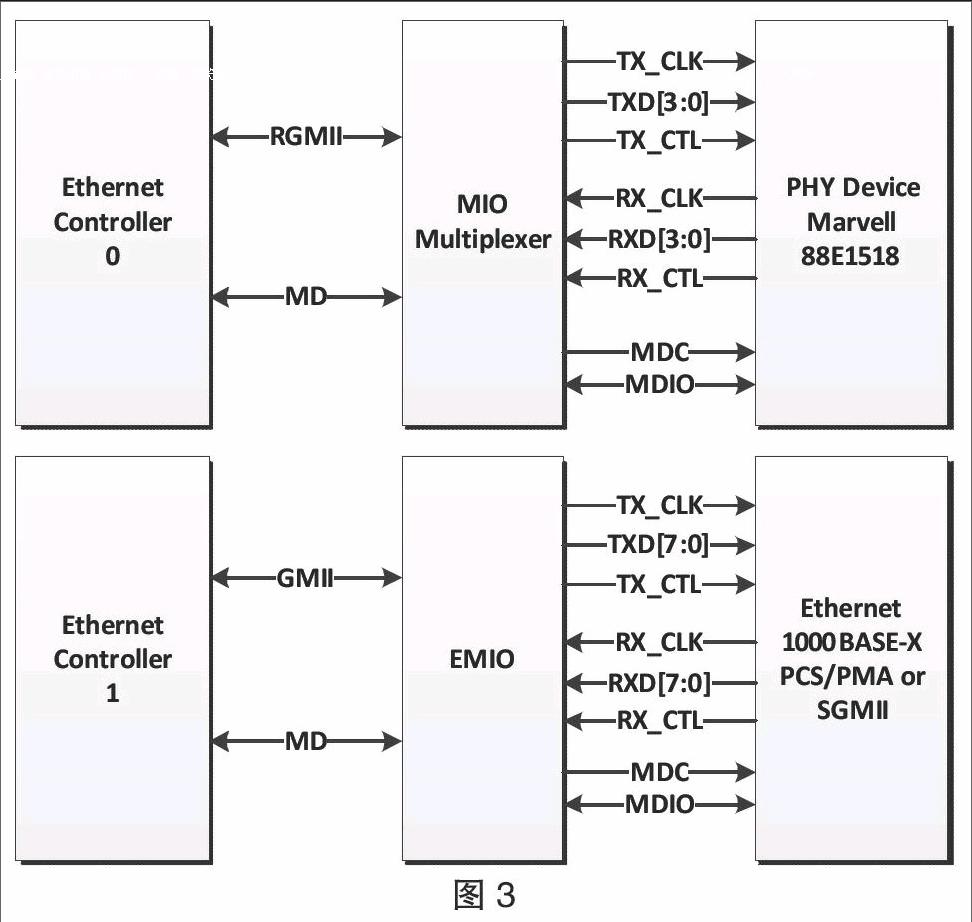

千兆以太网控制器0使用MIO,从PS端出,外接Marvell 88e1518物理PHY。千兆以太网控制器1使用EMIO,从PL端出,在PL中使用IP核Ethernet 1000BASE-X PCS/PMA or SGMII,实现SerDes PHY。如图3所示。

4 结语

基于软硬件协同设计的Zynq SOC平台,巧妙利用PS和PL设计资源,实现了多种形态的以太网接口。且该设计集成度高、通用性良好。助力不同场景下,更灵活的应用Zynq,实现资源效能最大化。

参考文献

[1]陆佳华,江舟,马岷.嵌入式系统软硬件协同设计实战指南基于Xilinx Zynq[J].2013.

[2]何宾. Xilinx All Programmable Zynq-7000 SoC设计指南[M].清华大学出版社,2013.

[3]Xilinx Inc. Zynq-7000 All Programmable SoC Technical Reference Manual(v1.10),2015.