基于Aurora V8.3与PCI协议的高速数字图像传输

肖儿良,李文辉,简献忠

(上海理工大学 光电信息与计算机工程学院,上海 200093)

基于Aurora V8.3与PCI协议的高速数字图像传输

肖儿良,李文辉,简献忠

(上海理工大学 光电信息与计算机工程学院,上海 200093)

针对Virtex-5 FPGA Aurora V5.3协议使用复杂和芯片成本高的问题,文中提出了一种采用Artix-7 Aurora V8.3协议进行高速图像传输设计的新方法。系统使用该协议,以AXI4-Stream作为内部链路进行高速数字图像的传输;利用PCI接口通过DMA技术实现了数据交互。用双路光纤传输图像数据进行测试,实验结果表明,传输速率为131 Mbit·s-1,且稳定、可靠,为高速图像传输设计提供了一种思路。

FPGA; Aurora V8.3协议; AXI4-Stream; PCI

高速数据传输采取并行或串行两种方式,并行传输方式由于走线多、信号间串扰大等缺陷,无法突破自身的速度瓶颈。而串行传输拥有更高的传输速率且只需少量的信号线,降低了背板开发成本和复杂度,满足高频率远距离的数据通信需求,被广泛应用于高速数据通信系统设计中,因此对高速串行传输技术的研究具有一定的理论和实践意义[1]。

Aurora协议是由Xilinx公司提出的开放、免费、轻量级的可配置数据链路层协议,主要用于在多个高速串行通道之间进行点对点的数据传输,由于具有高速数据传输和简单易用的特点而得到了系统设计者的关注[2-3]。基于Virtex-5系列FPGA- XC5VLX50T芯片,文献[2]实现了基于PCI-Express及Aurora协议的高速光纤通信板卡的设计;文献[3]基于FPGA的高速光纤数据传输板卡设计。两者均使用的是基于单个单链路Aurora IP核的设计,且只使用一个GTP。

针对文献[2]和文献[3]中所使用的Aurora V5.3 IP[4]在同时使用同一GTP_BANK内的两个GTP作为两个单链路Aurora物理传输层时对IP修改工作量大和芯片成本高的问题,提出采用Aurora V8.3协议[5]进行高速图像传输设计的新方法。该方法降低了设计成本,缩短了研发周期,在系统内部容易实现LocalLink端口和AXI4-Stream端口之间的相互转换,便于程序模块的移植。同时使用国外开放IP组织Open Cores免费提供的PCI桥核[6],达到了进行实时图像采集的高速数据传输和实时显示的目的[7-8]。

1 Aurora IP协议

Aurora协议可为私有上层协议或标准上层协议提供透明接口的串行互联协议,允许任何数据分组通过Aurora协议封装,并在芯片间、电路板间,甚至机箱之间传输。Aurora协议提供了CHANNEL_UP、FRAME_ERR、SOFT_ERR和HARD_ERR等表示IP状态的信号,用户可以通过这些状态信号监视光纤通道,并在出现错误时,可以方便排查错误原因。

1.1 Aurora 8B/10B V5.3协议。

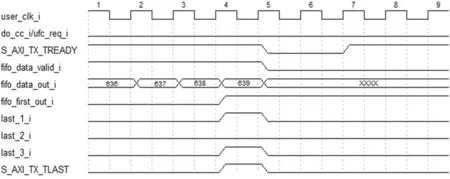

目前国内设计使用较多的是Xilinx公司Virtex-5系列的XC5VLX50T FF665 FPGA,该型号FPGA芯片包含4个GTP_DUAL,每个GTP_DUAL包含两个GTP,共8个GTP,每个GTP可构成单个通道,单个通道速率范围为0.5~3.2 Gbit·s-1。芯片使用的Aurora协议为5.3版本,其用户端口为LocalLink端口,在Framing模式下其基本发送时序如图1所示。其中TX_SOF_N有效表示一帧传输开始,TX_EOF_N有效表示一帧传输结束,TX_SRC_DRY_N有效表示传输数据有效,TX_DST_RDY_N有效表示可发送数据[9]。

图1 Aurora V5.3基本发送时序

在ISE14.1中定制生成Aurora V5.3 IP核,选择单链路全双工模式。生成IP后,可以查看GTP封装模块代码,可知其例化的一个GTP_DUAL模块包含了两个GTP硬核,但是只使用了其中一个GTP,另一个GTP引脚悬空或者接地。实际使用时,如果要同时使用同一个GTP_DUAL内的两个GTP各自成为单链路Aurora通道,不仅需要将另一个GTP引脚引出,配置相关参数的参数值,而且需要再例化一次RX_LL、LANE_LOGIC、GLOBAL_LOGIC和TX_LL模块,其工作量大,相对的延长了研发周期。

1.2 Aurora 8B/10B V8.3协议

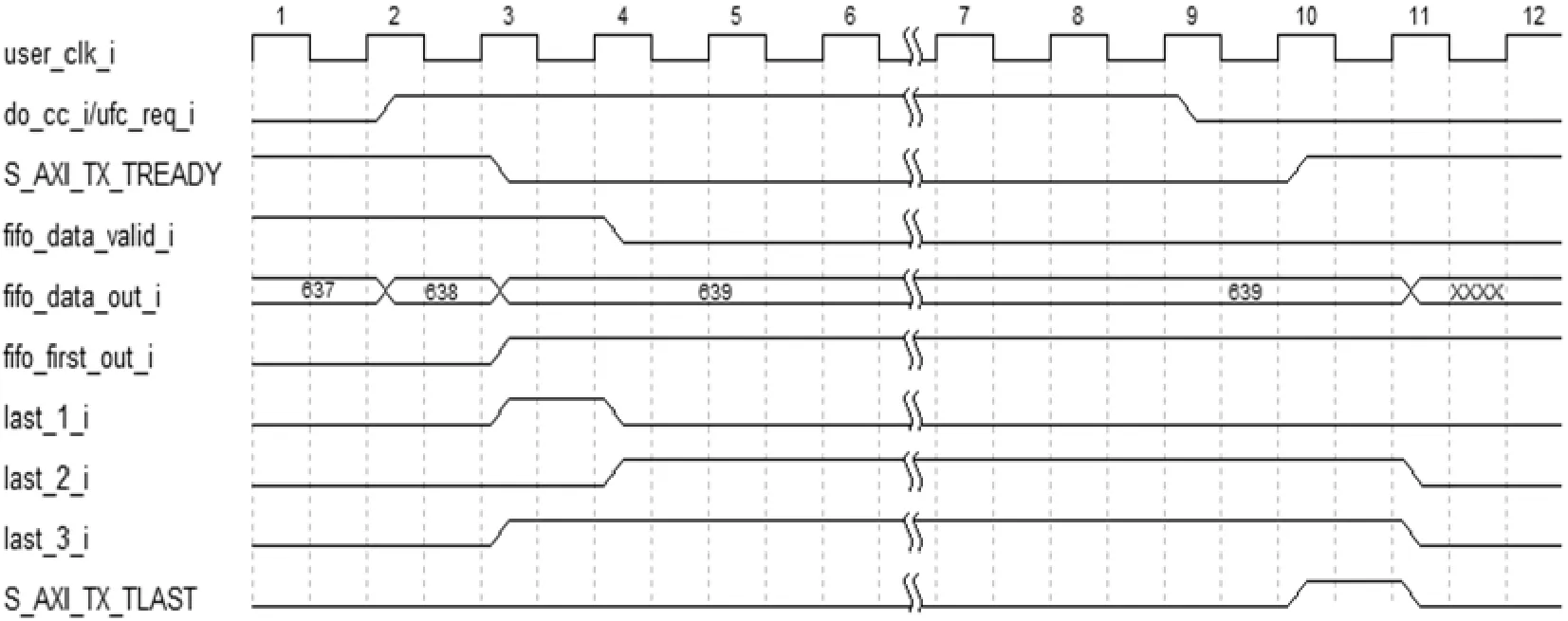

设计采用Xilinx公司的Artix-7系列XC7A200T FFG1156 FPGA芯片,该芯片包含4个GTP_Quads,每个Quad内含4个GTP,芯片共有16个GTP资源。Aurora IP可以使用其中任意的8个GTP,每个GTP可构成单个链路,每个链路传输速率范围是0.5~6.6 Gbit·s-1。该芯片使用的Aurora协议为8.3版本,用户端口(USERER INTERFACE)为AXI4-Stream端口,在Framing模式下其基本发送时序如图2所示。其中S_AXI_TX_TVALID有效表示传输数据有效,S_AXI_TX_TREADY有效表示可以发送数据,S_AXI_TX_TLAST表示一帧传输结束。

在ISE14.4中定制生成Aurora V8.3 IP核,选择单链路全双工模式。查看底层GTP_Wrapper代码可知,GTP封装中例化了1个GTPE2_COMMON(为GTP提供时钟的PLL)模块和1个GTPE2_CHANNEL(即GTP收发器)模块。

图2 Aurora V8.3基本发送时序

在FFG1156封装中,1个GTP_QUAD中包含1个GTPE2_COMMON模块和4个GTPE2_CHANNEL模块,其中前者为后者提供4个时钟输入。如果同时使用同一个GTP_QUAD内的多个GTP作单链路使用时,只需要生成两次Aurora IP,并对源代码稍作修改,即可实现多个单链路Aurora IP。

综上所述,对比Aurora协议的这两个版本可以得到以下结论:

5a 1H NMR(CDCl3) δ:7.79-7.76(m,1 H),7.76-7.75(m,2 H),7.55-7.53(m,3 H),7.33-7.31(m,3 H),3.82(s,3 H)

(1) AXI4-Stream端口相比LocalLink端口,取消了帧起始信号,降低了用户设计发送逻辑的难度;

(2) 使用同一个GTP_BANK内的GTP实现多个单链路通道时,对Aurora V8.3 IP源代码的修改相对简单的多,缩短了研发周期;

(3) Aurora V8.3协议相较于Aurora V5.3协议,其内部提供了LL_TO_AXI和AXI_TO_LL两种模块,用户可以直接例化使用,用于实现LocalLink端口和AXI4-Stream端口之间的转换,便于用户模块的移植;

(4) Artix-7系列的该型芯片成本比Virtex-5系列的这款芯片低的同时,单链路Aurora的最大传输速率更高。

2 Aurora V8.3传输设计

在Xilinx的ISE14.4中生成Aurora IP V8.3核,则相应的目录下生成了VHDL描述的相关文件以及例程。在设计中,对Xilinx提供的Aurora IP核相关的外围功能模块的使用如下:

(1) 时钟模块。该模块用于生成Aurora所需的时钟,该模块保持不变,直接使用;

(2) 标准时钟补偿模块。对整个Aurora模块提供时钟补偿。接收端根据接收数据流内嵌的时钟补偿信息对自身参考时钟进行修正,以降低误码率[10]。该模块直接使用,不做修改;

(3) Aurora复位模块。该模块提供了对Aurora核内部逻辑的复位和对GTP的复位。在本设计中,因为需要保证拔、插光纤后,PC机收到的PCI发送的中断数能够继续累加,故对该模块做部分修改,使得当拔掉光纤后,Aurora IP能够一直保持在复位状态。

图3 DO_CC间隔显示图

但是,在通过Aurora向外传输数据过程中,如果插入时钟补偿或者传输UFC信息,都会导致传输数据中断,如果不做处理,接收端接收的数据就会丢数。为解决此问题,本文设计了发送FIFO控制模块,待发送的数据先暂存在FIFO中,等存到设定个数后读取并通过Aurora传出[12-13]。如果插入时钟补偿或者需要传输UFC信息时,暂停读取FIFO中数据,待传完后,继续读取FIFO直到读空。该模块设计的重点在于对S_AXI_TX_TLAST帧结束信号的设计,其主要解决的是如果恰好在读出FIFO中最后一个数据时插入时钟补偿或者发送UFC信息,接收端会丢失这一行的最后两个数据的问题。

对S_AXI_TX_TLAST发送信号的逻辑设计如下:在读出FIFO中最后一个数据时,未插入时钟补偿或者发送UFC数据,所设计逻辑时序如图4所示;读出FIFO中最后一个数据时,插入时钟补偿或者发送UFC数据,所设计逻辑时序如图5所示,在两种情况下,S_AXI_TX_TLAST帧结束信号总是在一帧的最后一个数据有效一个时钟周期,符合AXI4-Stream端口的发送时序。

图4 读FIFO中最后一个数据时序1

图5 读FIFO中最后一个数据时序2

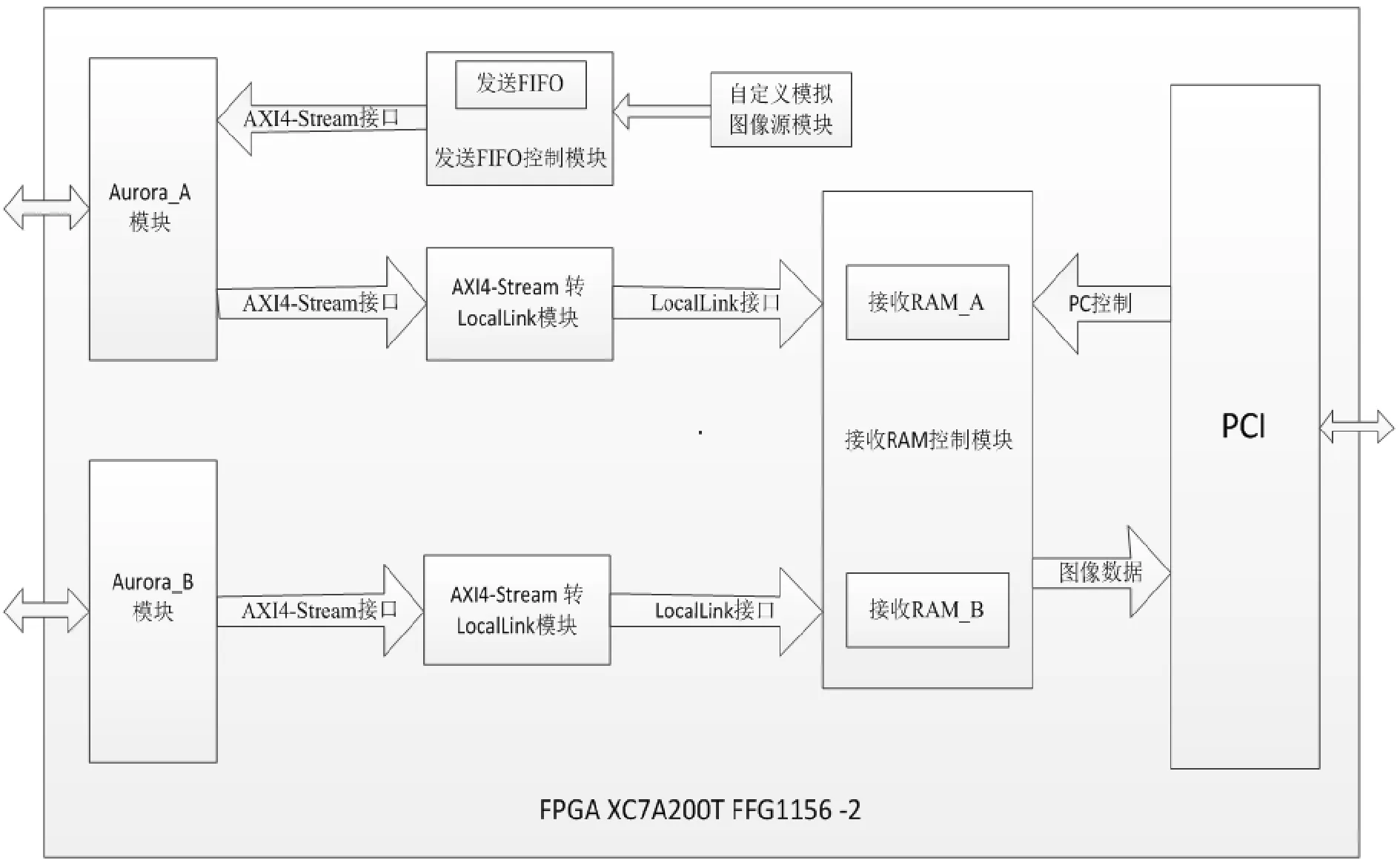

3 高速图像传输系统设计

3.1 系统设计

在硬件方面,单模光纤用于接收每秒200帧640×513×16 bit的数字图像图像数据,双模光纤接收每秒200帧640×513×8 bit的数字图像数据。Aurora所使用的USER_CLK时钟频率为62.5 MHz,PCI总线时钟频率设置为66 MHz,保证FPGA内部数据传输速率达到要求。

图6 高速图像采集卡硬件图

设计的顶层原理图框图如图7所示,其中单模光纤连接的GTP为BANK MGTP116中的GTPE2_CHANNEL_X1Y6,双模光纤连接的GTP为GTPE2_CHANNEL_X1Y7[14]。

图7 顶层原理图

3.2 连接光纤测试

实际测试时,图像采集卡使用的是Artix-7型号的FPGA,图像源来自Virtex-5 型号的FPGA。Xilinx 公司的Aurora IP可以向后兼容,也就是Artix-7器件中的Aurora可以和Virtex-5器件中的Aurora对话。但是如果保持默认的GTP参数值,在使用光纤连接两块板卡时,会出现光纤连接不稳定的现象,即Aurora的CHANNEL_UP指示信号一直处于通道建立、断开的循环状态。经排查,对Artix-7型号的FPGA中GTP的时钟纠正电路参数进行修正(时钟纠正电路实时监测待匹配的数据序列),即RX接收端的弹性缓冲区限制参数CLK_COR_MIN_LAT(最小延迟)由10改为28和CLK_COR_MIN_MAX(最大延迟)由14改为32,使其同Virtex-5型号的FPGA中GTP参数一致[15]。经多次调整测试,当两个参数值在一定范围内时,光纤连接都能长时间稳定不断开,通过Aurora传输数据稳定、正确。本设计采用的值同Virtex-5中的GTP时钟纠正电路参数值一致。

为验证Aurora复位模块功能,在数据传输过程中拔掉光纤后重新连接,PC显示的收到的PCI发出的中断数会在上一次值的基础上继续累加,经多次拔插光纤验证,功能正确。

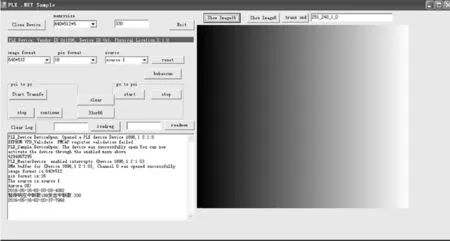

3.3 系统测试

光纤1(单模)接收的图像数据规格为每秒200帧640×513×16 bit(数据源的产生速率为131 MB·s-1)的图像数据,并通过PCI传给PC机。此图像数据前512行数据为图像每个像素点的像素信息,在第512行后,新一帧图像传输前加入第513 行,该行信息为整个系统的辅助状态信息。数字图像在PC机端显示如图8中的右侧所示,每一行的灰度从左到右排列均为从低到高。

图8 PC端接收光纤1图像显示

光纤2(双模)接收的图像数据规格为每秒200帧640×513×8 bit的图像数据,第一行为辅助状态信息行,后512行数据为图像每个像素点的像素信息。接收的数字图像在PC机端显示如图9中的右侧所示,从左到右的灰度排列为由高到低。

图9 PC端接收光纤2图像显示

经长时间测试,两路Aurora接收数据都正确无误,没有出现丢帧、错帧现象。

4 结束语

本文采用单片高性能FPGA实现了基于PCI接口的双路光纤信号接入,实现了计算机与外部设备之间的高速、连续、稳定、可靠的数据传输。测试证明,该板卡的逻辑设计思想正确、可靠,传输速率完全达到要求。并且本文所设计的Aurora的发送FIFO模块,为PC机向FPGA传输数据并通过光纤传出做了准备。该光纤通信卡在高速数据远程采集、远程实时控制、高速数据交换和高速光纤网络通信等领域,有着广阔的应用前景。

[1] 杜旭,于洋,黄建.基于FPGA 的高速串行传输接口的设计与实现[J].计算机工程与应用,2007,43(12):94-96.

[2] 王长清,冀映辉,王维,等. 基于PCI-Express和Aurora协议高速光纤通信板卡的实现[J].微计算机应用,2010,31(1):64-68.

[3] 成平,杨建,王炬城.基于FPGA的高速光纤数据传输板卡设计[J].信息通信,2015(1):79-80.

[4] Xilinx Inc.LogiCORETM IP aurora 8B/10B v5.3 [M].USA:Xilinx Inc,2012.

[5] Xilinx Inc.LogiCORE IP aurora 8B/10B v8.3 [M].USA:Xilinx Inc,2012.

[6] 徐江丰,李松,张涌.基于Wishbone片上总线的PCI Bridge核的研究和应用[J].电子设计工程,2005(4):23-26.

[7] 孙高俊,刘志英.基于FPGA的雷达IQ光纤数据采集及传输系统[J].电子技术,2016,29(4):169-172.

[8] 王立娜,闫大伟.基于FPGA的PCI数据采集卡设计[J].电子科技,2013,26(7):85-86.

[9] 王宇,汤心溢,刘鹏,等.拼接型长线列红外双波段图像实时传输系统[J].红外技术,2013,35(2):69-73.

[10] 岳振,吕波,张涌,等. 基于Aurora协议的高速图像传输和通信平台设计[J].电子技术应用,2014,40(8):7-9.

[11] 肖儿良,韦荣明,颜文超,等.基于Aurora及CameraLink的高速数字图像传输[J].信息技术,2015(4):94-97.

[12] 陈雪,李佩玥,章明朝,等.基于PCI Express总线的高速光纤接口卡的设计与实现[J].电子技术应用,2011,37(5):64-67.

[13] 武荣伟,苏涛,梁中英.RocketIO在高速数据通信中的应用[J].通信技术,2010,43(11):9-11.

[14] Xilinx Inc.7 series FPGAs GTP transceivers user guide [M].USA:Xilinx Inc,2014.

[15] Xilinx Inc.Virtex-5 FPGA RocketIO GTP transceiver user guide [M].USA:Xilinx Inc, 2009.

High-speed Transmission for Digital Image Based on Aurora V8.3 and PCI Protocol

XIAO Erliang,LI Wenhui,JIAN Xianzhong

(School of Optical-electrical and Computer Engineering, University of Shanghai for Science and Technology, Shanghai 200093, China)

To address the complexity in using the Aurora V5.3 protocol IP and the high cost of Virtex-5 FPGA chip, this paper introduces a new method of design of high-speed image transmission based on Artix-7 Aurora V8.3 protocol. The system uses the Aurora V8.3 protocol and takes AXI4-Stream as the internal link interface to design high-speed image transmission, realizing data interaction by the DMA control of PCI interface. Test of image transmission system with dual optical fiber shows that this method achieves stable transmission of correct data at a speed of 131 Mbit·s-1.

FPGA; Aurora V8.3 protocol; AXI4-Stream; PCI

2016- 07- 06

中国科学院基金(30133020001)

肖儿良(1969-),男,博士,硕士生导师。研究方向:嵌入式系统等。李文辉(1990-),男,硕士研究生。研究方向:嵌入式系统。简献忠(1969-),男,博士,硕士生导师。研究方向:新能源等。

10.16180/j.cnki.issn1007-7820.2017.06.001

TN919.8

A

1007-7820(2017)06-001-04