基于FPGA的以太网和串口数据传输系统设计分析

翟永宁++张翼飞

DOI:10.16660/j.cnki.1674-098X.2017.11.155

摘 要:随着社会不断进步,网络技术飞速发展,“高效、稳定”等是以太网的显著特征,已被广泛应用到多个领域中,通信、传输等,顺利实现了信息数据传输。因此,笔者站在客观角度,客观阐述了以太网、串口数据传输以及FPGA,探讨了基于FPGA的以太网以及串口数据传输系统设计。

关键词:FPGA 以太网 串口 数据 传输系统 设计

中图分类号:TN273 文献标识码:A 文章编号:1674-098X(2017)04(b)-0155-02

1 以太网数据传输、串口数据传输、FPGA

1.1 以太网数据传输

1973年,Xerox公司提出了以太网技术,和过去相比,其信息数据传输速率明显提高。以太网主要经过了3个发展阶段,站在应用时间角度来说,传统10 Mbps已退出历史舞台,快速以太网、千兆以太网正处于核心位置,但在电力事业发展道路上,终将被万兆或者更高速率的以太网取代。以“百兆以太网”为例,在普通双绞线作用下,最大传输距离可达到100 m,在光纤作用下,其传输距离超过1 000 km,千兆以太网、万兆以太网的传输距离远远超过百兆以太网。

1.2 串口数据传输与FPGA

简单来说,串口便是传输数据中采用的串行式逐位传输形式,被简称为串行接口。串行通信接口是指计算机上九针COM端口,以通信方式为基点,可以将其划分为不同的类型,即同步串行通信、异步串行通信。以“异步串行通信”为例,单一帧中各位间时间间隔是固定的,但相邻帧的时间间隔并不相同,其一个帧并不是由单一元素组成,比如,起始位、校验位,115 200 bps是异步串行通信最大传输波特率。此外,FPGA出现于1984年,随着半导体工艺日渐发展,单位面积硅片中可以生成大批晶体管,FPGA成本大幅度降低,其性能日渐提高。研究者还借助SOPC Builder软件工具,构建出全新的NiosII软核处理器,具有多样化的优势,比如较高的控制性能,FPGA应用领域进一步扩展。

2 基于FPGA的以太网数据传输系统设计

2.1 基于FPGA的以太网数据传输硬件系统设计

在设计基于FPGA的以太网数据硬件系统中,设计者必须准确把握以太网数据传输客观目标要求,综合分析主客观影响因素,科学设计其硬件电路,需要选择适宜的数字平台核心FPGA芯片,科学设计存储电路、以太网电路等。在此基础上,设计者需要利用SOPC Builder工具,搭建合理化的NiosII处理器硬件,优化设计其总体架构的基础上,科学设计以太网组件MAC、控制组件PIO等。在设计硬件电路过程中,设计者需要科学选取核心FPGA,充分发挥其核心作用,要具有较强的控制能力、引脚资源丰富,科学处理信号,动态控制系统,比如,采集控制、以太网信息数据传输控制。在设计存储电路的时候,设计者需要根据以太网数据传输系统设计客观要求,选取适宜的存储器件,即非易失性存储器件、易失性存储器件,前者可以用来存储FPGA配置文件,即使断电后存储的一系列数据也不会丢失,后者可以存储NiosII处理器运行过程中产生的一系列信息数据等,具有多样化的特点,容量特别大,读取的速度也非常快,但断电后存储的信息数据会丢失。此外,设计者需要根据相关规定,优化设计以太网电路,要具有较高安全性、稳定性、较快运行速度等,合理设计以太网物理层以及物理层收发器,确保数据信息传输速度不小于25.6 Mbps,进一步提高网络系统利用效率。图1便是基于FPGA的以太网数据传输硬件结构示意图。

2.2 基于FPGA的以太網数据传输软件系统设计

在设计过程中,设计者还要科学设计以FPGA为基点的以太网数据传输软件系统,充分发挥C/C++语言编程多样化作用,根据NiosII软件开发环境特点、性质等,顺利实现NiosII处理器一系列操作,以Lab Windows/CVI编程环境为切入点,优化设计软件系统显控功能。在设计NiosII程序的时候,设计者必须准确把握该程序具体功能需求,将其处理器当作基于FPGA的以太网数据传输系统的重要服务端,科学采集一系列信息数据,将其传输到对应的客户端——显控软件,构建适宜的网络连接,动态控制一系列信息数据。设计者还要准确把握该程序工作流程,构建程序模块,设计网络连接程序、数据接收发送程序、控制数据发送暂停程序,顺利传输与接收多样化的网络信息数据。此外,设计者还要显控软件功能需求,将显控软件作为对应的客户端,接收、存储一系列信息数据,顺利连接、断开网络等。

3 基于FPGA的串口数据传输系统软件设计

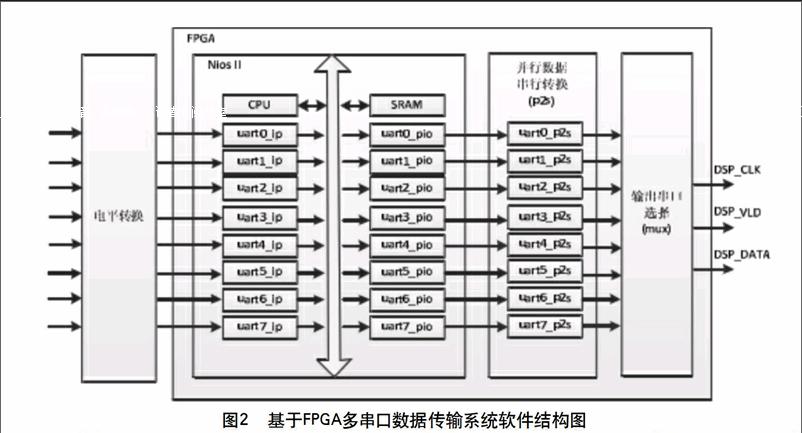

在设计基于FPGA的串口数据传输系统中,设计者要围绕其总体设计要求,制定合理化的设计方案,充分利用FPGA UART IP多样化作用,顺利接收各串口信息数据,优化调整对应的传输波特率,串行各路信息数据,将其传输到DSP中,借助超短基线定位系统作用下的FPGA,实现以DSP为基点的多串口扩展,最大化降低串口数据传输硬件系统难度,使其更加简单化,易于操作,进而最大化降低基于FPGA的串口数据传输系统整体成本,有效提高系统整体运营效益。在此基础上,设计者需要科学设计多个模块,串口数据接收模块、串口输出选择模块、数据并串转换模块等,使其各具特点,展现多样化功能。在设计串口数据接收模块中,设计人员先要设计电平转换电路,确保串口信息数据没接入FPGA引脚前转换电平,根据UART IP特征,以寄存器为切入点,改变海量信息数据传输过程中的波特率。在设计数据并串转换电路中,设计者要添加适宜的通道标志,在并串转换的基础上,进行ModelSim时序仿真。在设计串口输出选择模块的时候,设计者必须全方位、客观地分析输出特定通道串口信息数据所呈现的原理,ModelSim时序仿真设计也被包含其中,进而充分展现FPGA作用下串口数据传输系统多样化功能,优化调整串口波特率。图2便是以FPGA为基点,多种模块作用下,多串口数据传输系统软件结构示意图。

4 结语

总而言之,在设计基于FPGA的以太网和串口数据传输系统中,设计者需要以社会市场为导向,坚持一系列设计原则,严格按照相关规定,准确把握FPGA的特点、性质,多层次优化设计以太网数据传输系统硬件以及软件、串口数据传输系统,多角度合理测试对应的系统数据,在优化完善的基础上,进一步提高基于FPGA的以太网和串口数据传输系统安全性、稳定性。以此降低故障发生率,降低系统运行成本,实现最大化的经济效益。

参考文献

[1] 杨新华,王用玺,刘欣.基于FPGA的以太网高速数据传输系统的设计[J].仪表技术与传感器,2013(12):80-83.

[2] 李正军,周志权,赵占锋.基于FPGA的高速数据传输系统设计与实现[J].计算机测量与控制,2016(9):188-190,194.

[3] 俞鹏炜,任勇,冯鹏,等.基于FPGA的千兆以太网CMOS图像数据传输系统设计[J].国外电子测量技术,2016(11):76-

81.

[4] 史鹏腾.基于千兆以太网的FPGA双向数据传输系统设计[D].西安电子科技大学,2014.