基于单片机的数字抢答器设计

朱枫+彭森

摘 要:数字抢答器由主体电路与扩展电路组成。优先编码电路、锁存器、译码电路将参赛队的输入信号在显示器上输出;用控制电路和主持人开关启动报警电路,以上两部分组成主体电路。通过定时电路和译码电路将秒脉冲产生的信号在显示器上输出实现计时功能,构成扩展电路。

关键词:单片机;抢答;LCD显示;锁存

1 引言

应单片机的发展史单片机诞生于20世纪70年代末,经历了SCM、MCU、SoC三大阶段。第一阶段:SCM即单片微型计算机(Single Chip Microcomputer)阶段,主要是寻求最佳的单片形态嵌入式系统的最佳体系结构。第二阶段:MCU即微控制器(Micro Controller Unit)阶段,主要的技术发展方向是:不断扩展满足嵌入式应用时,对象系统要求的各种外围电路与接口电路,突显其对象的智能化控制能力。第三阶段:单片机是嵌入式系统的独立发展之路,向MCU阶段发展的重要因素,就是寻求应用系统在芯片上的最大化解决;因此,专用单片机的发展自然形成了SoC化趋势。随着微电子技术、IC设计、EDA工具的发展,基于SoC的单片机应用系统设计会有较大的发展。

2 抢答器的工作原理

为了更有效的描述该设计的原理,报告中有相同和相似工作原理的讲诉都只描述一次。同时在讲述一模块的原理时,忽略另一模块的影响。同时各芯片还有不涉及到本设计的功能,都做无效化处理。

八路带限时抢答器功能实现的最直接证明就是三个数码管的正常显示,第一个数码管用来显示编号,二三数码管用来显示秒倒计时。在本设计中编号为1~8(非0~7),秒倒计时可从0~99秒预置。

首先是编号的显示,设计中采用七段共阴数码管,另由74LS48驱动,编码电路采用74LS1488-3线优先编码器完成,锁存由四R-S触发器集成电路74LS279完成。现在从编码电路讲起,在没有任何按键按下时,74LS148的输出端(默认为A0、A1、A2)全为高电平,而输出端分别接至R-S触发器的置1端(低电平有效),编码器的GS输出端接在第四个R-S触发器的置1端(R-S触发器初始状态都为Q输出低电平),输出Q端分别接至驱动器的BCD码输入端,第四个R-S触发器的Q端则接至数码管驱动器的消隐端(低电平有效),所以初始态是数码管消隐无显示。在编码器有触发时,输出端输出相应的二进制电平,同时GS端输出低电平,驱动器的消隐端无效,数码管显示相应的编码。这里特别说明一下如何把0编码成8,该电路中如果触发D0端的话R-S触发器的输出是0001,而驱动器74LS48的BCD码输入端是X000,有且只有在低三位输入为0时,D端才能为高电平,这里就用到了两个或门,或门是只要有一个输入端为1输出为1,有且在输入端都为0时输出0,所以只有在D0触发的情况下低三位都为0使之显示8。

3 方案设计

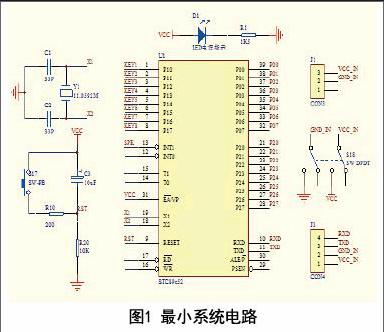

该系统采用51系列单片机STC89C52作为控制核心,该系统可以完成运算控制、信号识别以及显示功能的实现。由于用了单片机,使其技术比较成熟,应用起来方便、简单并且单片机周围的辅助电路也比较少,便于控制和实现。整个系统具有极其灵活的可编程性,能方便地对系统进行功能的扩张和更改。

4 结论

由555定时器秒脉冲产生电路,十进制同步加减计数器74LS192减法计数电路,74LS48译码电路和2个7段数码管及相关电路组成。具体电路如图1所示。两块74LS192实现减法计数,通过译码电路74LS48显示到数码管上,其时钟信号由时钟产生电路提供。74LS192的预置数控制端实现预置数,由节目主持人根据抢答题的难易程度,设定一次抢答的时间。预置时间电路对计数器进行预置,计数器的时钟脉冲由秒脉冲电路提供。按键弹起后,计数器自动开始减法计数工作,并将时间显示在共阴极七段数码显示管上。当有人抢答时,停止计数并显示此时的倒计时时间;如果没有人抢答,且倒计

时时间到时,2输出低电平到时序控制电路,控制报警电路报警,且使以后抢答选手抢答无效。

参考文献

[1] 李小堅. Protel DXP电路设计与制版使用教程[M].北京:人民邮电出版社,2001

[2] 徐进强. 单片机技术任务驱动式教程[M].天津:天津大学出版社,2002

[3] 李海滨. 单片机技术课程设计与项目实例[M].北京:中国电力出版社,2005

[4] 刘瑞新. 单片机原理与应用教程[M].北京:机械工业出版社,2007

[5] 李广弟等. 单片机基础[M].北京:冶金工业出版社,2004

[6] 李全利. 基于Proteus的单片机可视软硬件仿真[M].北京:机械工业出版社,2010

作者简介

朱枫,邵阳学院信息工程系电子科学与技术专业学生

通讯作者(指导老师)

彭森,邵阳学院信息工程系教师