基于计数器原理的调频信号解调方法*

唐 波,黄文玲,张静远

(海军工程大学 兵器工程系,湖北 武汉 430033)

基于计数器原理的调频信号解调方法*

唐 波,黄文玲,张静远

(海军工程大学 兵器工程系,湖北 武汉 430033)

提出了一种基于计数器原理的调频信号解调方法,该方法以FPGA为核心,结合放大整形电路、高频振荡器电路以及DAC,完成对超声以及以下频率的调频信号解调。该方法通过对信号周期计数,然后用计数值检索存储有信号幅度值的存储器,最后经过DAC得到调制信号。

计数器;调频信号;解调;FPGA

0 引言

对调频信号的解调常采用变容二极管等模拟元件组成的解调电路来实现,然而模拟电路存在诸多缺陷[1]。随着电子技术的不断发展,FPGA以其强大的功能和丰富的资源迅速占领了信号处理领域。基于计数器原理的调频信号解调方法就是以FPGA为核心,采用数字的方式来实现调频信号的解调。

1 基本原理

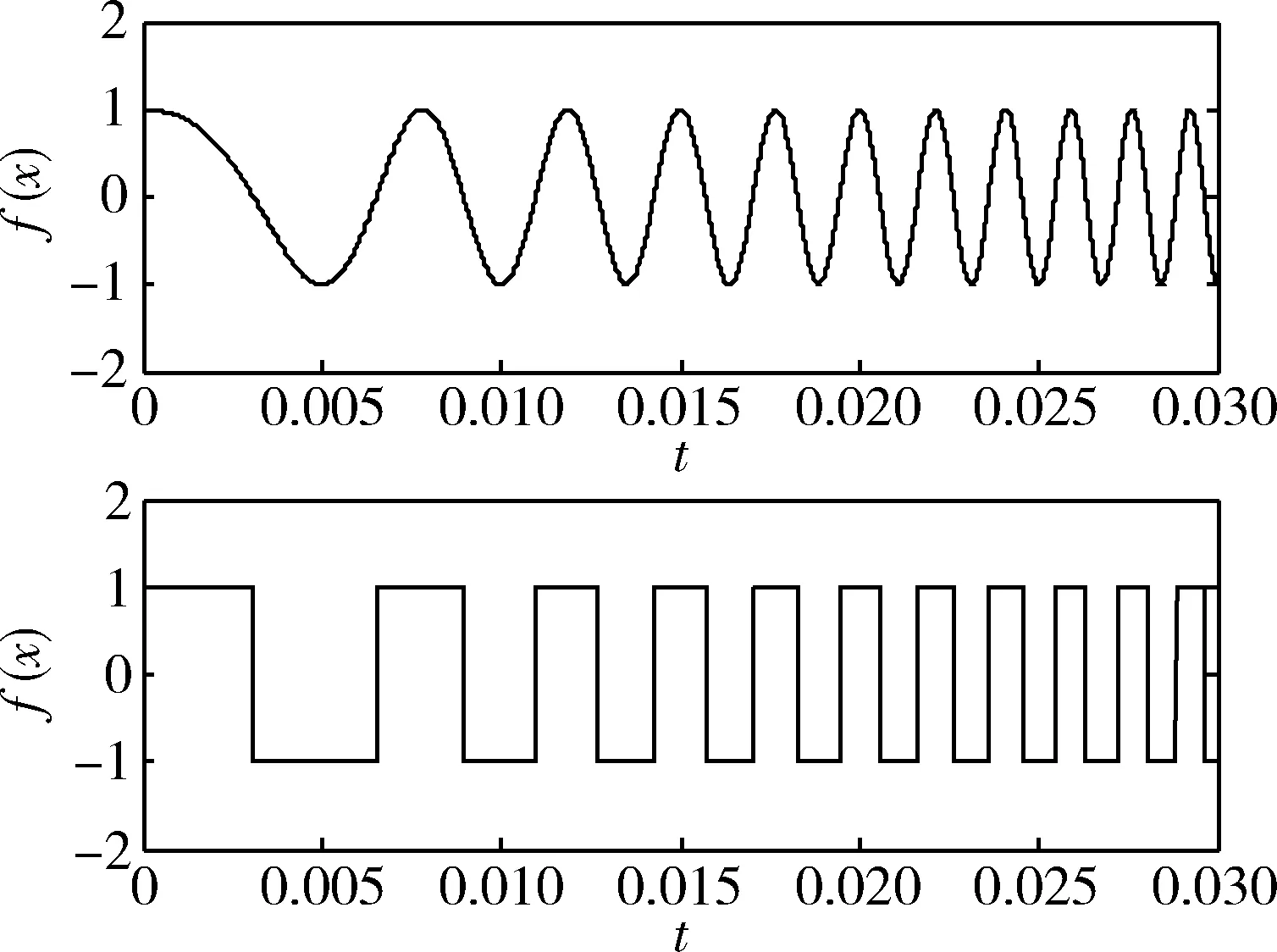

假设一调频信号f(x),对其进行整形放大,便可得到与调频信号同频的方波信号[2],如图1所示。

图1 调频信号与放大整形后的方波信号

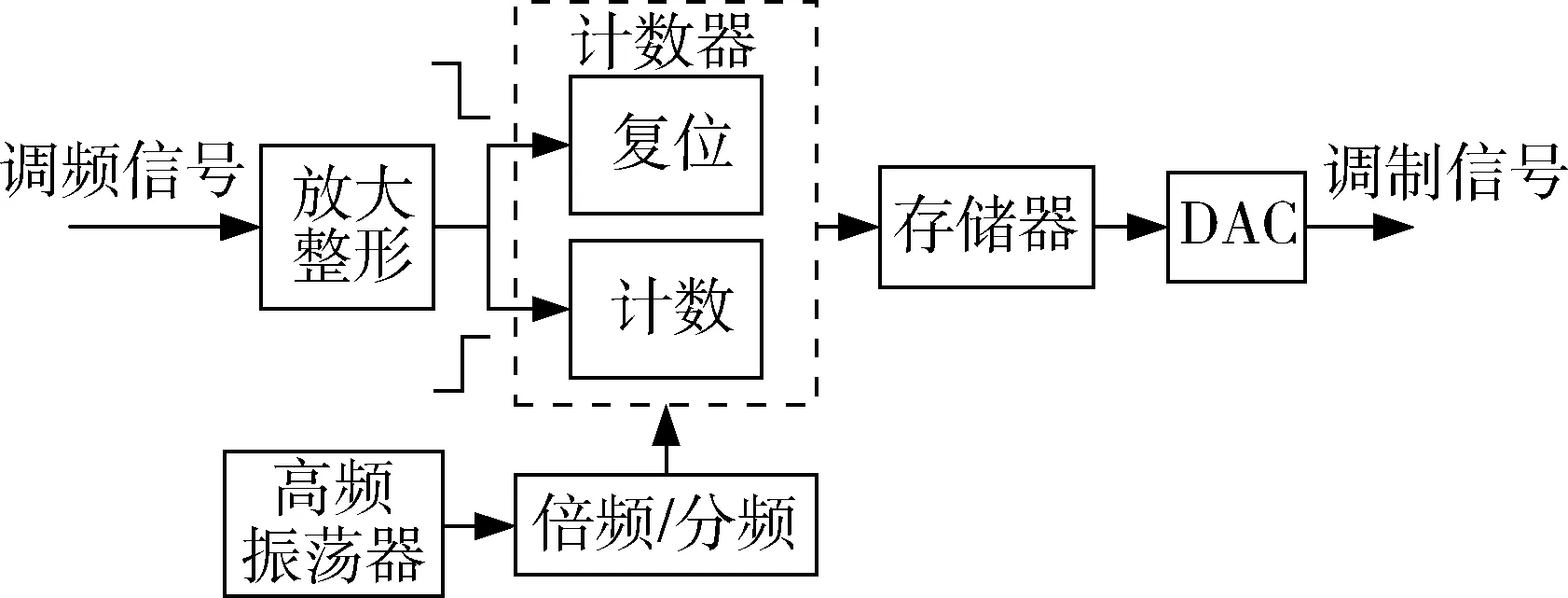

在方波信号的上升沿启动计数器计数,同时在上升沿输出计数器计数值并复位计数器。计数器输出值用于检索存储器,存储器中存储有相应的信号幅度信息,存储器输出连接D/A转换器,则可得到幅度随输入信号频率变化的输出信号。系统原理框图如图2所示。

图2 系统原理框图

其中计数器主要完成对信号周期的计数,对于调频信号来说,信号瞬时周期反比与信号瞬时频率,因此计数值可实时反映信号频率的变化,经过存储器的映射关系得到调制信号的幅度值,经DAC变换后输出。

其中高频振荡器用于产生高频震荡信号,经倍频或分频后得到与调频信号频率相匹配的计数时基。

2 系统分析

2.1 时基电路

由高频振荡器产生震荡信号,经过倍频或者分频之后得到计数时基信号,时基信号的选择取决于不同信号的频率范围。时基信号fc的选择通常考虑两方面因素:调频信号的频率上限fmax和调频信号的频率下限fmin。

为了保证对信号的周期计数具有较高的精度,通常要求时基信号频率大于信号频率的50倍[3],即:

fc≥50fmax

(1)

同时,计数器的输出信号作为存储器的地址信号,用于检索相应的调制信号幅度值,因此计数器的输出值vc最大值受到存储器存储深度dm的限制,即:

(2)

即:

fc≤dmfmin

(3)

2.2 计数器

计数器对计数值输出、计数启动、计数复位采用相同的触发源,均在方波信号的上升沿触发。因此计数器每个上升沿的输出值反映的都是信号周期的时间,计数器的计数时基信号频率为fc,因此计数器的输出值vc可表示为:

(4)

计数器的输出值反映的是调制信号的变化规律,当调制信号幅度减小时,计数器的输出值增大,反之,则减小。

2.3 存储器

存储器中存储有调制信号的幅度值,它的主要功能是完成计数值到调制信号幅度值的映射,即以计数器的计数值作为地址信号,检索相对应的幅度值。对于计数器来说,计数值与调制信号幅度是成反比的,因此存储器中高

图4 系统电路原理图

位地址存储的是信号的小幅度值,低位地址则存储信号的大幅度值。因此当输入信号频率降低的时候,在存储器的输出端得到较小的信号幅度值,反之则得到较大的信号幅度值。经过DAC之后就可以得到调制信号。

3 误差分析

由以上分析可知,计数值反映的是信号频率的变化规律,因此式(4)可以表示为:

则信号频率的相对误差可以表示为:

则极限情况下的最大误差为:

(5)

图3 计数误差原理

由图3可以看出,采用计数器对信号周期进行计数,总会存在一个±1个计数周期的误差,则有:

(6)

显然,增大计数时基频率与信号频率之间的差别可以有效地减小系统误差。

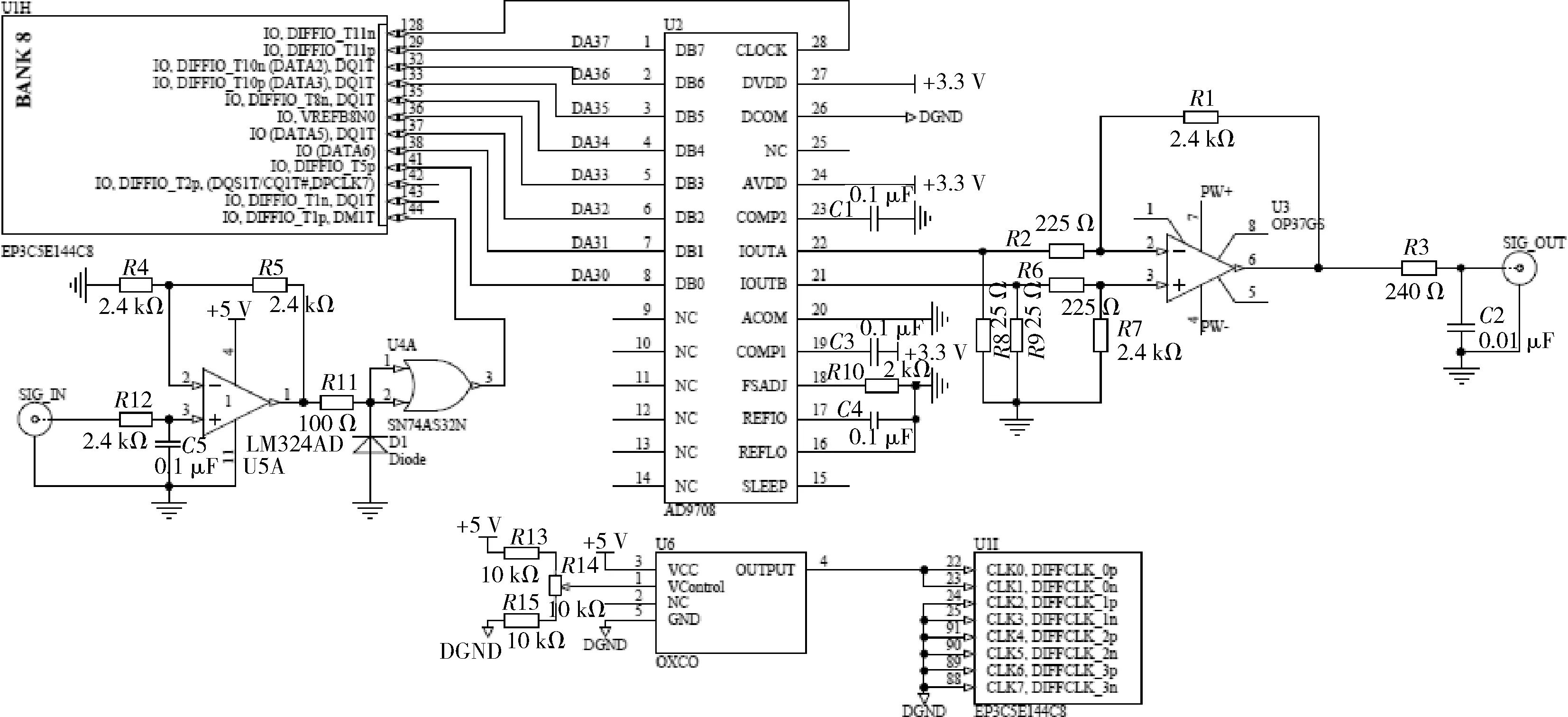

4 电路实现

随着电子技术的不断发展,以FPGA为核心的各种信号处理系统不断涌现,由于丰富的片上资源,使得系统极大地简化[5]。在该系统中,FPGA实现倍频/分频、计数器以及存储器的功能,系统电路原理如图4所示。

由图4可以看出,前端模拟电路实现信号的放大整形,即将输入信号转换成能被FPGA接收的方波信号,在FPGA中以一定的计数时基完成对信号周期的计数,并以计数结果作为存储器的地址信号读出存储在存储器中的调制信号幅度,最后经过DAC将离散的调制信号幅度值转换成模拟的调制信号,从而完成对信号的解调。

5 结论

由以上分析可知,只要针对输入信号的频率范围选取合适的计数时基,就可以以较高的精度实现对调频信号的解调,而且通过增大存储器的存储深度可以从整体上提高系统的精度。该系统使用方便,参数修改灵活,可以在不做硬件改动的情况下适应不同频段信号的解调。

[1] 陈科山, 王燕. 现代测试技术[M]. 北京:北京大学出版社, 2011.

[2] 田坦, 刘国枝, 孙大军. 声呐技术[M]. 哈尔滨:哈尔滨工程大学出版社, 2006.

[3] 王绍卿. 鱼雷近炸引信原理与设计[M]. 西安:西北工业大学出版社, 1992.

[4] 申忠如, 郭福田, 丁晖. 现代测试技术与系统设计[M]. 西安:西安交通大些出版社, 2014.

[5] 朱明程. FPGA原理及应用[M]. 北京:电子工业出版社, 1994.

The demodulation of frequency modulated signal based on counter

Tang Bo,Huang Wenling,Zhang Jingyuan

(Department of Weaponry Engineering, Naval University of Engineering, Wuhan 430033, China)

Based on the counter, this paper presents the demodulation of frequency modulation signal which uses the FPGA, amplifying and shaping circuits, high-frequency oscillator and DAC. Firstly it counts the signal period used to index the memory of signal amplitude. Then DAC can convert the output of memory to modulation signal.

counter; frequency modulation signal; demodulation; FPGA

国家自然科学基金项目(11602300)

TN76

A

10.19358/j.issn.1674- 7720.2017.08.023

唐波,黄文玲,张静远.基于计数器原理的调频信号解调方法[J].微型机与应用,2017,36(8):73-75.

2016-10-23)

唐波(1980-),男,博士研究生,讲师,主要研究方向:兵器科学与技术。

________________________