基于FPGA控制的高速大容量NAND FLASH存储模块设计

彭卓文,杨新民,王胜红(.南京理工大学 江苏 南京0094;.淮海工业集团 山西 长治046000)

基于FPGA控制的高速大容量NAND FLASH存储模块设计

彭卓文1,杨新民1,王胜红2

(1.南京理工大学 江苏 南京210094;2.淮海工业集团 山西 长治046000)

为了实现对于炮弹弹道测试系统采集数据实时存储,本文设计了一种存储模块。该模块由XILINX公司的XC3S1600E和意法半导体公司的NAND512W3A构成,通过对FPGA进行硬件编程实现对NANDFLASH的读写控制[1]。针对NANDFLASH存在坏块的缺点,提出了相应的管理方法,保证了数据的可靠性。通过实时更新并存储NAND FLASH操作地址来保证存储模块重新上电之后可以继续存储。

FPGA;NANDFLASH;大容量存储;坏块管理

目前最新型的弹载黑匣子在实时性、大容量、高可靠性、高速率等方面又有了新的要求,炮弹弹道实验中姿态、轨迹、旋转速率等参数在被采集后需要及时存入存储模块中。传统的数据存储模块多用ARM作为其控制核心,但是由于ARM的时钟频率较低且需用软件实现数据存储,这使得存储的速度和效率较低,在整个存储周期中大多为软件的运行时间。而FPGA有ARM无法比拟的优势,FPGA时钟频率高、内部延时小,全部控制逻辑由硬件完成,速度快、效率高。在此技术基础上,为了满足数据存储对速度的要求,本文将介绍一种基于FPGA,采用VerilogHDL硬件描述语言设计实现的高速数据存储模块[2]。存储芯片采用意法半导体公司的NAND512W3A,利用FPGA构建读写FIFO缓存、硬件擦除和读写以及坏块屏蔽NANDFLASH,从而加快了黑匣子数据存储的速度和可靠性[3]。

1 存储模块硬件设计

本论文设计的存储模块由 XILINX公司的XC3S1600E[4]和意法半导体公司的NAND512W3A[5]构成。FPGA通过I/O引脚与NANDFLASH进行数据传递,通过片选信号和NANDFLASH返回的信号对NANDFLASH进行控制。地址存储空间与数据存储空间分别存放NANDFLASH操作地址和外围设备采集的数据[6]。

NANDFLASH和FPGA相连接的部分包括:8个I/O口,锁存信号线,状态信号线。锁存信号线包括:地址锁存(ALE),指令锁存(CLE),写使能(WE)以及读使能(RE)。状态信号线包括:片选信号(CE)和状态位信号 (R/B)。其中,状态位信号高电平时表示NANDFLASH空闲,低电平时表示NANDFLASH忙碌。存储模块结构由框图1所示。

图1 存储模块结构框图

2 存储模块的基本原理

ALE和CLE分别为地址锁存和命令锁存,因为FPGA与NANDFLASH之间的所有通信都是通过8 个I/O口进行的,通过ALE和CLE的状态来区分通信的具体内容。当ALE高电平时表示传输的内容为地址信息,当CLE高电平时表示传输的内容为指令信息,当两个都为低电平时则表示通信内容为数据。RE和WE分别为读写使能端,低电平有效。其中,片选信号低电平有效,状态位信号高电平就绪(Ready),低电平忙碌(Busy)。FPGA自带的I/O引脚数量很多,通过对FPGA进行编程使其能向NANDFLASH发出片选和使能信号[7]。FPGA将采集到的数据分类进行存储。NANDFLASH的操作主要包含擦除、编程和读取,由NANDFLASH的内部硬件结构决定了其擦除操作是以块(Block)为单位进行的,编程和读取操作是以页(Page)为单位进行的。实现整个存储功能的基本要求是必须要保证编程操作的过程中数据的可靠性和完整性。由于在写入过程中存在页寄存器(Page register),这个页是专门用来存放将要写入的数据,其本质相当于页缓存,当缓存的数据收集满一页后再传输给后续的物理存储单元[8]。

3 FPGA对NANDFLASH的烧写

NAND512W3A芯片的各种操作必须写入相应的命令才能顺利执行,由于命令、地址、数据共用I/O,所以要通过命令锁存信号和地址锁存信号共同控制而分时复用[9]。其中NANDFLASH的引脚命令很丰富,下面是NANDFLASH的主要操作简介。

3.1 擦除操作

器件的擦除操作是以块为单位的。加载块地址时先输入60h建立擦除命令,然后再输入确认命令D0h,执行内部擦除过程。先建立再擦除的两步命令时序可以保证存储数据不会被外部干扰所影响导致误擦除。擦除操作流程图如图2所示。

图2NANDFLASH擦除操作流程图

3.2 写入操作

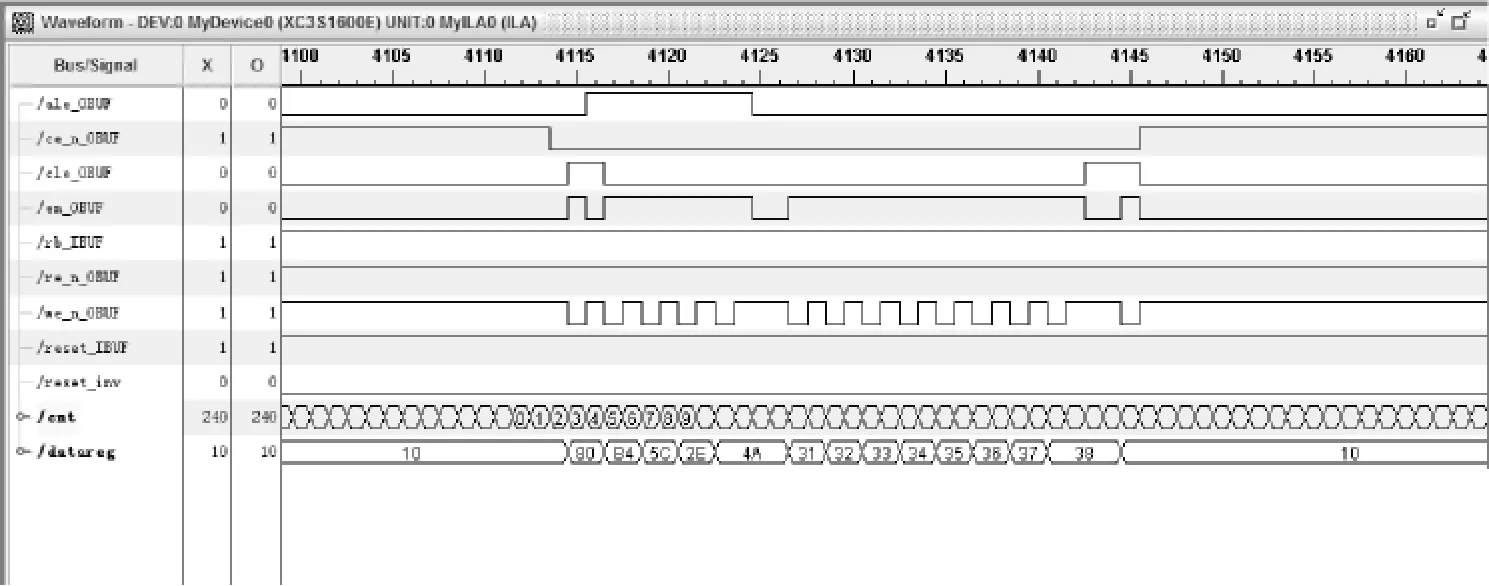

在编写NANDFLASH的控制程序时器件的编程以页为单位,一个页编程周期中可以对一个或者多个连续的字节进行编程。一个页编程周期包括串行数据加载阶段和编程阶段组成。数据在加载阶段被加载至数据寄存器中,在数据编程阶段被写入存储单元。写操作的过程为:1)发送写开始指令80h;2)发送第1个cycle地址;3)发送第2个cycle地址;4)发送第3个cycle地址;5)发送第4个cycle地址;6)写入数据至页末;7)发送写结束指令10h。具体仿真波形如图3和图4所示。

3.3 读取操作

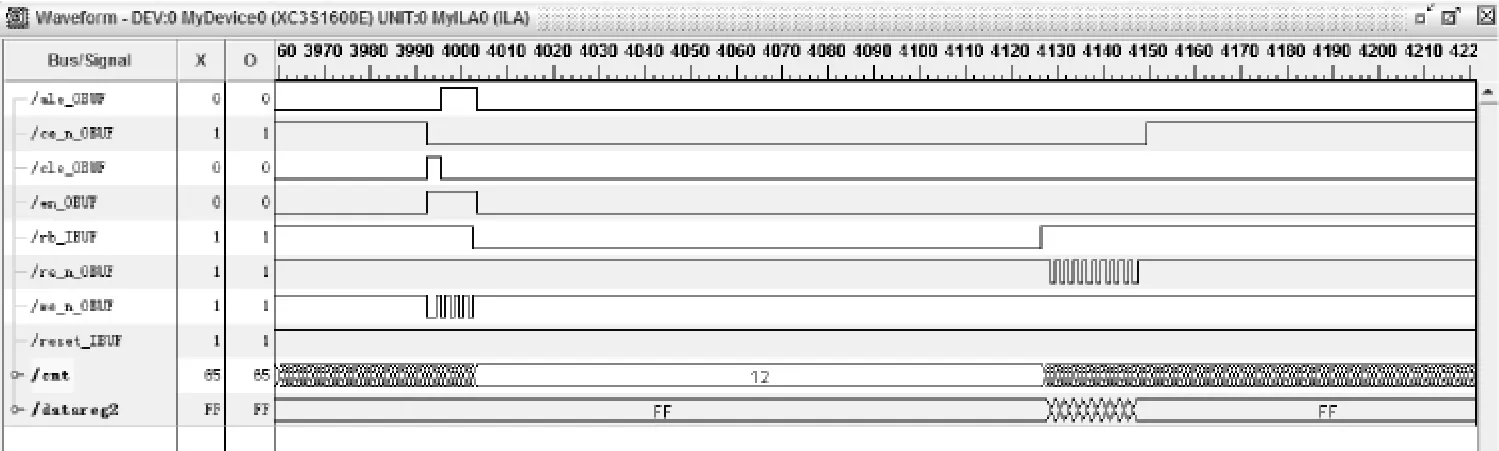

NANDFLASH的数据读取操作包括NANDFLASH 的READ ID操作和读取片内数据操作。其中READ ID操作是读操作的基础操作,NANDFLASH器件ID包括:Manufacture ID和Device ID,这些信息是判断NANDFLASH的重要凭证。具体操作为:在CLE为高点平且WE_n的下降沿,在IO输入90h命令让NANDFLASH进入读ID状态,接着在ALE为高电平且WE_n的下降沿时,在IO输入00h地址,等待tALLRL1的时间后RE_n由高置低,在之后RE_n的两个下降沿将ID读出。其结果Manufacture ID为20h,Device ID为76h,板级验证图5所示。

NAND512W3A每页分为A,B,C 3个区,总共528字节。其中A区256字节,B区256字节,C区16字节,A区和B区的读取时序一致,读取时要分三步读取。在A区读取完毕后可以通过将片选信号暂时拉高来中断读操作,将片选信号再次拉低即可进行B区的读取操作NAND512W3A的寻址分为4个cycle。分别是:A[0:7]、A[9:16]、A[17:24]、A[25: 26]。 读操作的过程为:1)发送读取指令;2)发送第1个cycle地址;3)发送第2个cycle地址;4)发送第3个cycle地址;5)发送第4个cycle地址;6)等待信号变回高电平;7)读取数据至页末。图6和图7为具体的读取A区操作仿真波形图。

图3NANDFLASH写操作ModelSim仿真波形图

图4 NANDFLASH写操作ChipScope仿真波形图

图5 READ ID ChipScope仿真图

4 创建初始化坏块表

坏块问题一直是NANDFLASH存储过程中的基本问题,坏块的种类分为出厂坏块和使用过程中的新增坏块,一般生产NANDFLASH的厂家会有标记出出厂坏块的个数和存在的位置,烧写时应当避开这些出厂坏块进行烧写。而在存储过程中出现的新增坏块则需要进行ECC校验。创建坏块信息表的存储方式是在系统接收到了NANDFLASH的擦除命令后,先读取NANDFLASH中的固有坏块信息并且对有效块进行两次擦除操作,同时建立逻辑块地址和有效块标识表[10]。擦除操作完毕后,将该表同时写入到NANDFLASH前3块有效块中,这样可以防止因某一块的损坏而使坏块信息丢失,不能正确判断出有效块,从而导致存储数据出现偏差商确保每个坏块的第一或者第二页的列地址 2048处[11]。这样在每次上电过程中将3块中的好坏块标识信息都读出并对比,如有某一块存储坏块信息不正确,则立即将信息表转存到有效块中,做好备份工作。具体实现操作首先是NANDFLASH出厂时厂是非FFh数据。由于初始坏块信息在某些情况下是可擦除的,因此在使用之前应该依据初始坏块信息建立初始化坏块表,本设计中初始化坏块表是在记录NANDFLASH里创建的,创建初始化坏块表[12]。具体操作如图8所示。

图6 NANDFLASH A区读操作仿真波形图

图7 NANDFLASH A区读操作结果放大图

图8 创建初始化坏块表流程图

5 NANDFLASH的断电保护问题

为了使NANDFLASH在断电再上电后仍能继续之前的操作,地址缓存在每次NANDFLASH读写操作后都会更新当前地址,更新的地址将被存入NANDFLASH的地址存储空间。在下一次NAND FLASH操作开始之前,再把之前存入的地址读出并当作这次工作的操作地址[13-14]。这样就可以保证NANDFLASH在重新上电之后,操作地址可以再从NANDFLASH的地址存储空间读出,从而继续工作。在烧写过程中,当一个片选的容量存满之后,需要自动切换到下一个片选信号,进而继续工作。对NANDFLASH的每次操作都涉及到对应的操作地址,即页地址、块地址和片选号(从页首开始操作,不考虑页内地址)。一次操作完成后,应该更新操作地址并进行相应的判断[15]。地址更新时,依次更新页地址、块地址和片选信号,当一个地址达到最大值时,该地址归零同时高阶地址加一。

6 结束语

文中针对炮弹弹道测试系统存储模块进行了设计,具体使用方案为FPGA搭载大容量NANDFLASH。主要完成的工作有:1)对FPGA擦除、读取和写入NANDFLASH的步骤做了简单的介绍。2)针对NANDFLASH出现坏块的情况给出了相应的解决方案。3)对NANDFLASH操作地址实时更新,并将操作地址进行存储,重新上电后读出地址继续操作。最终实现系统所需要求,性能稳定。

[1]任勇峰,张凯华,程海亮.基于FPGA的高速数据采集存储系统设计[J].电子器件,2015,38(1):135-139.

[2]黄辉.基于FPGA的数据记录仪NANDFLASH读写模块研制[J].科技创新导报,2012,12:13-14.

[3]常璐,蒲南江.一种基于FPGA的高速数据记录系统的设计[J].电脑学习,2011,4(2):132-134.

[4]XILINX.Spartan3E Platform FPGA handbook[EB/ OL].

[5]ST.NAND01GW3A0CV1 datasheet[EB/OL].

[6]张博,段哲民.基于FPGA的数据采集系统设计[J].电子设计工程,2012,20(7):86-88.

[7]刘东海,任永峰,储成君.基于FPGA控制的NAND FLASH存储设计[J].科学技术与工程,2013,34(13): 10349-10353.

[8]张峰.基于NANDFLASH阵列的高速存储技术[J]..电讯技术,2013,53(1):68-70.

[9]赵榉云,张敬帅.基于NANDLFLASH的数据存储系统设计[J].单片机与嵌入式系统应用,2012(6): 71-73.

[10]舒文丽,吴云峰,赵启义,等.NANDFLASH坏块存储办法[J].电子仪器,2011,34(5):580-583.

[11]乔立岩,李元亨,王戈.一种NANDFLASH坏块管理优化方法的实现 [J].电子测量技术,2015,38 (7):19-21.

[12]贾源泉,肖侬,欧洋,等.基于NANDFLASH的多路并行存储系统中坏块策略的研究[J].计算机研究与发展,2012(49):68-72.

[13]李槐生.基于FPGA的NANDFLASH控制器的设计[J].科学之友,2011(11):146-149.

[14]吴凡.基于FPGA和NANDFLASH的嵌入式存储系统设计[J].电子科技,2016,29(3):97-101.

[15]邢亮,黄晖,田丹.机载系统NANDFLASH存储技术[J].航空计算技术,2014,44(1):123-125.

Design of nandflash memory module with high speed and large capacity based on FPGA

PENG Zhuo-wen1,YANG Xin-min1,WANG Sheng-hong2

(1.National Key Laboratory of Transient Physics,Nanjing University of Science and Technology,Nanjing 210094,China;2.Huaihai Industrial Group,Changzhi 046000,China)

In order to achieve the storage of Ballistic test system’s real-time data,this article designs a storage module.The module consists of XILINX XC3S1600E and STMicroelectronics NAND512W3A,which controls the read&white operation of NANDFLASH by programing the FPGA.Aiming at the problems that NANDFLASH contains bad block,this paper proposes for a corresponding management measure and secures its data’s reliability.As well,the memory module could continue work when it is reenergized though updating and saving the operation address in real time.

FPGA;NANDFLASH;large storage;bad block management

TN98

A

1674-6236(2017)07-0111-04

2016-04-22稿件编号:201604222

彭卓文(1992—),男,湖北十堰人,硕士。研究方向:FPGA的数据采集和记录。