MicroBlaze软核处理器的SPI控制器设计

张荣刚,顾强

(中北大学 机电工程学院,太原 030051)

MicroBlaze软核处理器的SPI控制器设计

张荣刚1,顾强2

(中北大学 机电工程学院,太原 030051)

设计了一种基于Xilinx公司提供的MicroBlaze微处理器的SPI控制器。该SPI具有可配置的分频器、三线-四线转换功能,同时可以根据外接的芯片SPI总线需求配置其数据发送的方式。该SPI控制器的逻辑功能在Modelsim下仿真结果正确,并且在Virtex-7芯片上运用此控制器配置多款高速数据转换器、时钟芯片等。验证结果表明,该SPI控制器具有使用灵活、便于移植、易于使用、可以同时配置多片器件等优点。

串行外设总线;MicroBlaze;FPGA;Vivado

引 言

现代通信系统中很多集成电路的配置总线大多为I2C、SPI等低速总线,这类总线速度从几十kbps到几十Mbps不等。常用的设计方案是用一颗微控制器芯片来控制这些外设器件,采用FPGA传输高速数据,这样的设计对于硬件工程师来说无疑加大了工作量和设计成本,得不偿失。

MicroBlaze软核是一款针对Xilinx FPGA器件而优化的功能强大的32位微处理器,支持用于嵌入式处理器的标准AXI总线外设集合,具有兼容性和可重复利用性,最精简的核只需要将近400个Sclice[1]。利用适当的技术,用户可以开发构造简单的预配置MicroBlaze微控制器,并方便快捷地将其添加到任何FPGA设计中,还可将控制器的实例直接加入HDL。用户能在标准的FPGA设计流程中直接使用,无须特殊的脚本或复杂的步骤,仅需三个文件即可启动设计工作,包括两个硬件实施文件和一个软件定义文件。这种方法使工程师不用学习或者只需很少量的学习就能快速启动FPGA嵌入式设计工作。同时Xilinx公司提供了与标准的Eclipse一致的软件工具SDK,以及大量可用户定制的驱动程序,符合 POSIX 规范的内核库、网络和文件处理库,可以简单地通过MicroBlaze与外设进行通信。

SPI(串行外设接口)总线是Motorola公司推出的一种高速、同步、全双工的通信总线。它只需要4条线就可以完成MCU与各种外围器件的通信,正是由于这种简单易用的特性,越来越多的芯片集成了这种通信协议。许多高速模/数转换器、高频PLL时钟芯片等,通常使用SPI接口配置其寄存器。该设计使用Xilinx公司的Virtex-7系列FPGA芯片,利用Verilog HDL语言编写SPI模块,并封装成IP核添加到MicroBlaze的AXI总线上。

1 MicroBlaze 软核处理器

MicroBlaze是一款基于构造的嵌入式微处理器,其结构如图1所示,它的显著优势在于能满足复杂应用的需求,除了运行简单的通用应用以外,还能运行操作系统[6]。MicroBlaze 是高度可配置的 IP 核,支持 70 多种配置选项。用户可使用高度灵活的可配置内核,能够实现几乎任何处理器的使用案例,从极小型状态机或微控制器到运行 Linux 的高性能计算密集型微处理器系统,无所不能。

图1 MicroBlaze 处理器结构

该IP既可配置为在三级管线模式下工作(针对尺寸进行优化),也可配置为在五级管线模式下工作(针对速度进行优化),因而可提供比其他任何 FPGA 软处理解决方案更快的 DMIP 性能。

该设计采用的FPGA为XC7V485T芯片,拥有75 900个Slices,485 760个逻辑单元,片内RAM共37 080 KB,14个时钟CMT模块,2 800个DSP Slices,56个GTX(最高12.5 Gb/s)高速收发器,4个PCIE GEN2模块。同时此芯片内集成的MicroBlaze软核处理器最高工作频率可达到389 MHz,对于不同的应用情况,可以选择minimum area、maximum performance、maximum frequency、linux with MMU、typical、frequency optimized等配置模式,各种模式占用的资源也不尽相同[6]。

2 SPI总线接口

SPI总线是Motorola公司提出的一个同步串行外设接口,具有接口线少、通信效率高等特点。该设计中用于验证的外设器件为ADI公司的AD9265模数转换器,接口实现方案与业界标准SPI端口兼容,并且至少采用双线式模式和可选的芯片选择引脚[7]。

ADI公司高速转换器的SPI端口由3个引脚组成:串行时钟引脚(SCLK)、串行输入/输出引脚(SDIO)和片选引脚(CSB)。

串行时钟(SCLK):该引脚为串行移位时钟输入引脚。为降低该引脚对视中线路上噪声的敏感度,采用施密特触发器实现,并且通过50 kΩ电阻下拉到地。SCLK的最低保证频率为25 MHz,输入数据在上升沿有效,输出数据在下降沿有效。保持时间(tDH)典型值为0 ns,SCLK与SDIO之间要求最短5 ns的建立时间(tDS)。

串行数据输入/输出(SDIO):该引脚具有双重用途。通常用作输入或输出,具体取决于所发送的指令(读或写),以及时序帧中的相对位置(指令周期或数据周期)。在写或读操作的第一阶段,该引脚用作输入,将该信息传递到内部状态机。如果该命令被确定为读命令,状态机将把该引脚(SDIO)变为输出;如果该命令被确定为写命令,则在指令周期内,SDIO引脚始终为输入。

芯片选择(CSB):该引脚是一种低电平有效控制,用来选通读写周期,CSB可以在多种模式下工作。当该线为低电平时,器件被选择,SCLK和SDIO线路上的信息便会得到处理;该引脚为高电平时,器件会忽略SCLK和SDIO线路上的所有信息。在一些配置中,CSB可以停止在高电平,即在多个时钟周期内保持高电平,如果传输三个字节或更少的字节(不包含指令信息),则CSB可以在字节(包括指令信息的字节)之间停止在高电平。

3 SPI控制器结构设计

该SPI控制器主要分为SPI配置模块、SPI控制模块、SPI输出模块。首先由spi_ff_i[31:0]、spi_fe_i[31:0]、spi_fd_i[31:0]三个寄存器将SPI的时钟分频、传输地址、数据长度等参数以及操作开始请求信号送入配置模块,然后配置模块将各项参数从寄存器中读出并送入控制模块,最后由输出模块将数据与SCLK时钟同步输出到MOSI和MISO端口。

由于SPI总线工作频率从几Mbps到二十几Mbps不等,因此在此SPI控制器中需要分频模块将处理器工作频率降低到低速范围才能满足一些高性能时钟芯片、ADC、DAC芯片的微总线时序要求。图2所示为该SPI控制器的分频器模块分为CLK_IDLE(6’h01)、 CLK_CNT_OP(6’h02)、CLK_HALF_PERIOD(6’h04)、CLK_FULL_PERIOD(6’h08)、CLK_END_PERIOD(6’h10)、CNT_END(6’h20)共6个状态。当检测到cfg_op_req信号置1后,分频模块启动,当时钟计数器达到half_sclk_period-1和sclk_period-2时,分别进入下一状态,当处于CLK_END_PERIOD时,如果检测到主状态机的op_done信号置1,则分频器停止运行。

图2 分频模块状态机

图3和图4为Modelsim对分频模块的仿真波形,sclk_period为24,经过验证与设计一致。

图3 分频模块仿真图

图4 系统时钟与SCLK仿真

如图5所示, SPI主状态机模块分为SPI_IDLE(7’h01)、SPI_INSTRUCTION_LOAD(7’02)、SPI_CS_SU(7’h04)、SPI_WRITE(7’h08)、SPI_READ(7’h10)、SPI_OP_RECOVERY(7’h20)、SPI_OP_DONE(7’h40)共7个状态。

图5 SPI主状态机

当cfg_op_req信号置1后,SPI控制器开始启动,读取SPI控制器的各项参数后,进入地址传输状态,当sck_cnt寄存器的值达到addr_size后,根据命令类型spi_cfg_type值,分别进入读或写状态,最后当sck_cnt达到addr_size与transfer_size的和后,进入最后一个SPI_OP_DONE状态,将op_done寄存器置1,SPI控制器返回IDLE状态。

SPI控制器主状态机仿真波形如图6和图7所示。

图6和图7分别为SPI_WRITE跳转到SPI_RECOVERY、SPI_OP_DONE状态和SPI_CS_SU跳转到SPI_WRITE,由于SCLK每次前半周期为低,后半周期为高,因此每次当sck_ne为1时,主状态机才进行跳转。SPI一次完整操作仿真如图8所示。

该SPI控制器的cs_n寄存器宽度为8位,因此SPI master控制器可以同时配置8片slave器件。当cs_n置0时,片选信号选中,SCLK、SDIO信号则开始配置该选中的器件。

4 FPGA验证与调试

Virtex-7系列的工程文件需要在Xilinx公司提供的工具Vivado下进行编译、综合、实现、下载、调试等流程。Vivado Design Suite 可提供业界首款即插即用型 IP 集成设计环境并具有IP 集成器特性,从而解决了 RTL 设计生产力问题。Vivado IP 集成器可提供基于 Tcl、设计期正确的图形化设计开发流程。IPI 特性可提供具有器件和平台意识的互动环境,能支持关键 IP 接口的智能自动连接、一键式 IP 子系统生成、实时 DRC 和接口修改传递等功能,此外还提供强大的调试功能。

在 IP 之间建立连接时,设计人员工作在“接口”而不是“信号”的抽象层面上,从而大幅提高了生产力。这通常采用业界标准的 AXI4 接口,不过 IP 集成器也支持数十个其他接口。

创建嵌入式处理器硬件设计时,可以在IP 集成器环境中实例化、配置和组装处理器内核及其接口。该工具能执行基于规则的连接功能,并提供设计辅助。设计通过实现完成编译后被导出到Xilinx软件开发套件(SDK) 中,用于软件开发与验证流程。仿真与调试功能使工程师可以跨两个域对设计进行仿真和验证。

IP集成器中可以设置4~256个32位宽的寄存器,并可以通过AXI4总线设置寄存器的值。在IP设计时,可以选择AXI4_Lite、AXI4_Stream、AXI4三种:AXI4用于高性能内存映射要求;AXI4-Lite用于简单、低吞吐量的内存映射通信(例如与控制和状态寄存器之间的通信);AXI4-Stream用于高速流数据。

图6 主状态机仿真a

图7 主状态机仿真b

图8 SPI一次完整操作仿真

由于该SPI控制器与MicroBlaze软核的交互数据主要为低速,少量数据,故可以选择AXI4_Lite模式。

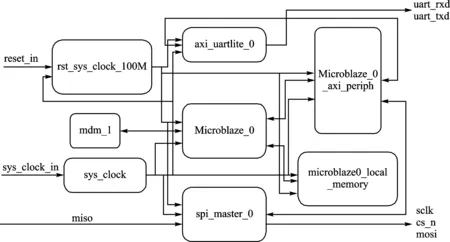

该SPI控制器封装成IP核时,共需要5个32位寄存器,spi_ff_i、spi_fe_i、spi_fd_i、读写请求request寄存器,以及一个回读寄存器read_back_reg 。图9所示adc16_spi_0即为该SPI控制器。

图9 MicroBlaze嵌入式设计

为了节省引脚,AD9265的SPI总线采用三线模式,即MOSI和MISO信号合并成SDIO端口。INOUT在具体实现上一般用三态门来实现。三态门的第三个状态就是高阻'Z'。当INOUT端口不输出时,将三态门置高阻。该端口为INOUT信号,当SDIO为输出时,MISO为高阻态1’bz,这就是所说的高阻输入;同样当SDIO读取从slave器件进来的数据时,mosi为高阻态1’bz。

如图9所示,该设计选用的MicroBlaze为typical模式,设计中除了SPI控制器还有uartlite、clock_module、reset_module、axi_connector,以及MicroBlaze_debug_module和一个64 KB的local_bram作为MicroBlaze的数据和指令缓存。

完成综合、实现并生成bit文件后可以将硬件信息导入SDK中,利用封装SPI控制器时Xilinx自动生成的driver函数来启动SPI控制器。

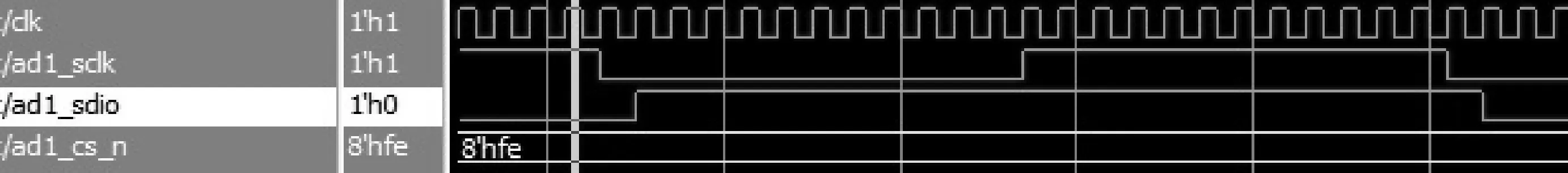

在ISE中可以捕捉信号的chipscope工具,同样到了Vivado下可以使用与其功能相似的debug工具捕捉信号,图10为调试SPI控制器时捕捉到的sclk、miso、mosi、cs_n等信号,并且与图8中通过Modelsim仿真得到的波形一致。

图10 Debug捕捉到的SPI信号

结 语

该SPI控制器设计在某公司开发的芯片测试系统中已经得到运用,运用该控制器已经对各类使用SPI总线的芯片成功调试。结果表明,该SPI控制器使用灵活,并且可以根据实际芯片的需求改变其输出模式。同时该控制器可配置多片器件,并且减少了硬件工程师的设计工作,对于高速数据传输和低速、小吞吐量控制通信功能,只用一颗FPGA器件即可完成。对于整个系统来说精简了很多不必要的模块,节省了成本。

[1] 王尔申,张淑芳,张芝贤.基于Xilinx MicroBlaze的嵌入式GPS接收机研究[J].通信技术,2010,43(10):28-30.

[2] 张斌,刘宇,荣金峰.通用型SPI总线的IP设计与实现[J].中国集成电路,2011,20(7):43-47.

[3] 阮芳,冯永新.基于Xilinx MicroBlaze的嵌入式I/O系统设计与实现[J].电子器件,2008,31(2):626-630.

[4] 龙霞飞,李仁发.MicroBlaze微处理器IP Core的结构及应用[J].微处理器,2004,25(6):6-9.

[5] Xilinx corporation.ug473 7Series Memory Resources(v1.10)[EB/OL].[2016-12].https://www.xilinx.com/support/documentation/user_guides/ug473_7Series_Memory_Resources.pdf.

[6] Xilinx corporation.ug984 vivado MicroBlaze ref(v2016.3)[EB/OL].[2016-12].https://www.xilinx.com/support/documentation/sw_manuals/xilinx2016_3/ug984-vivado-MicroBlaze-ref.pdf.

[7] ADI corporation.AN-877_cn 通过SPI与高速ADC接口[EB/OL].[2016-12].http://www.analog.com/media/cn/technical-documentation/application-notes/AN-877_cn.pdf.

[8] 杨定定,施慧彬.基于AXI总线的MicroBlaze双核SoPC系统设计[J].电子产品世界,2012,19(1):76-77.

[9] 张松,李筠.FPGA的模块化设计方法[J].电子测量与仪器学报,2014,28(5):560-565.

[10] 刘永健.软核嵌入处理器MicroBlaze[J].计算机与网络,2012,38(15):64-66.

[11] 张桂兴,张英敏,张鹏.基于IP核与ModelSim的正弦波发生器仿真平台建立[J].测控技术,2011,30(1):28-31.

[12] 顾颉,胡生亮,李朝旭.基于SPI接口ADC和FPGA的并行多通道同步采样系统设计[J].舰船电子工程,2011,31(12):146-149.

张荣刚(研究生),主要研究方向为混合信号芯片测试系统研究;顾强(教授),主要从事机电系统设计与分析、引信技术研究。

SPI Controller Design Based on Soft-core Processor MicroBlaze

Zhang Ronggang1,Gu Qiang2

(North Central University,School of Mechanical and Electrical Engineering,Taiyuan 030051,China)

In the paper,a SPI controller is designed which is based on MicroBlaze microprocessor provided by Xilinx.The SPI has a configurable divider,three-wire-to-four-wire conversion,and can configure the data transmission way according to the requirements of the external chip SPI bus.The logic of the SPI controller simulation results in Modelsim are correct,and can use the controller to configure a variety of the high-speed data converters,the clock chips in the Virtex-7 chip.The verification results show that the SPI controller has the advantages of flexibility,portability,easy to use and multiple devices configuration at the same time.

SPI controller;MicroBlaze;FPGA;Vivado

TP368

A

士然

2016-12-16)