一种基于FPGA的高效安全配置模式的设计

庄雪亚,王兴宏,闫 华

(1.中国电子科技集团公司第58研究所,江苏无锡214072;2.无锡中微亿芯有限公司,江苏无锡214072)

一种基于FPGA的高效安全配置模式的设计

庄雪亚1,王兴宏1,闫 华2

(1.中国电子科技集团公司第58研究所,江苏无锡214072;2.无锡中微亿芯有限公司,江苏无锡214072)

随着FPGA的应用场合不断扩展,对安全可靠下载比特流的研究也在不断深入和扩展。基于AES算法,采用SRAM和EFUSE两种存储器存储Encryption KEY,并配合两种解密电路,完成了基于FPGA的高效安全配置模式电路设计。该设计实现了将Encrypted比特流更高效、更安全、更灵活地下载到FPGA内的配置SRAM中。经过数字仿真波形分析,验证了设计方法的可行性和正确性。

AES算法;SRAM;EFUSE;FPGA;配置;加密

1 引言

随着网络技术的飞速发展,数据存储的容量也呈几何倍数增长,所以海量数据对信息的安全性、可靠性提出了更高的要求。2000年10月,美国国家标准技术研究所NIST宣布AES取代1977年定制的DES标准,作为新一代的数据加密标准,其汇聚了强安全性、高性能、高效性、易用灵活等优点,根据使用的密码长度,一般AES设计时采用128、192、256位宽[5]。由于FPGA在配置的过程中容易被非法攻击,检测下载数据线,非法得到bitstream,导致用户不必要的损失,本文在基于现有的AES加密方法的基础上设计了一个更便捷、更高效的解密结构。

2 加密解密流程

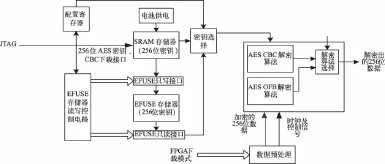

无论是网络传输中使用的安全传输协议还是安全手段或安全措施,它们都需要加密和解密的过程。本文中AES系统通过软件工具产生Encryption Key,连接JTAG下载至SRAM存储逻辑单元中,通过配置来选择解密逻辑,输出比特流,这一过程在本文中为通用加解密流程,不论是在加密还是解密中,当系统遇到不可恢复操作引起重启时存储在SRAM中的数据会因断电而丢失,因此需要通过电源供电维持SRAM存储单元来确保所下载密钥不丢失,如图1所示。本文改进了传统的通用存储方式[1]。同时图中也提供了另外一种加解密流程,Encryption Key通过JTAG写入SRAM中,同时可选择进入安全存储模式,将Encryption Key写入EFUSE中,更高效地利用其断电不丢失存储的特点,解密时可通过配置寄存器COR (Configuration Operation Register)选择不同的解密模式,分别从SRAM存储和EFUSE存储单元中选择通用CBC解密还是专用OFB解密。

图1 加解密设计流程

3 设计与实现

高效安全配置模式的设计是在普通AES加解密设计基础上,采用EFUSE可实现断电不丢失存储,突破SRAM电池供电的缺陷;采用新型解密电路,实现高安全性、强兼容性的解密功能[2]。在整个系统上电复位之后,通过JTAG下载由软件产生的加密数据Encryption Key,这时有两种存储单元可供选择,如图2所示,设计具有两个存储结构的加解密逻辑。SRAM静态存储器需要使用电池供电才能起到存储的功能,为了具有很好的兼容性,这里仍然保留SRAM进行存储[3];EFUSE区别于普通的SRAM阵列,其采用I/O电路的片上电压,仅仅一个持续200 μs的10 mA直流脉冲就足以编程单根熔丝[4]。其最大的优点是可以在断电情况下不丢失保存Encryption KEY,这样设计可以更好地满足用户的需求,用户可以选择一种适合自己的存储模式。在用户需要完成解密算法的设计中,通过配置又提供了CBC解密结构和OFB解密结构。

图2 加解密结构

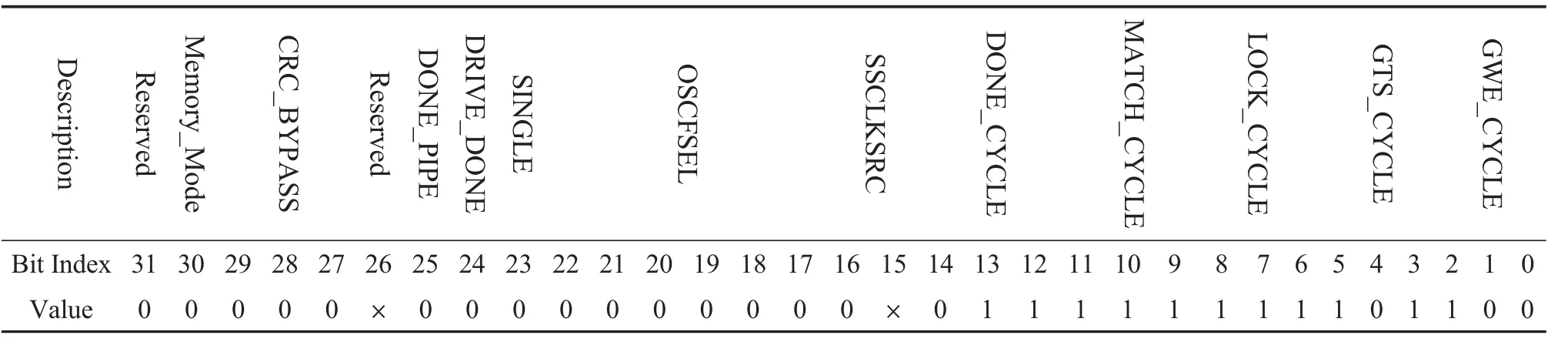

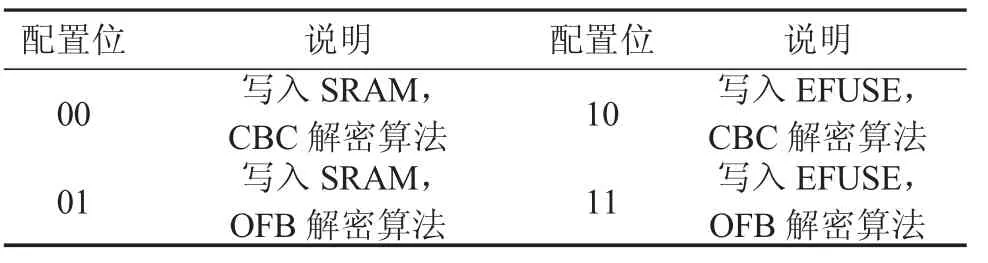

FPGA配置寄存器共有32位,在未分配功能的最高3位中,巧妙利用第29、30两位来控制下载数据模式选择和解密模式选择。默认情况下值都是0,配置寄存器的分配情况如表1所示,表2指出了每个状态的配置说明。

表1 配置寄存器

表2 配置寄存器说明

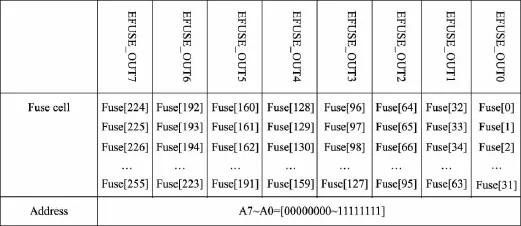

EFUSE阵列如图3所示,256个EFUSE存储单元分别分配在A0~A7这8个地址中,一次32 bit数据写入,分8次完成写256 bit加密数据。从存储阵列设计到解密的实现,都紧紧围绕数据的写入与读出,通过EFUSE_OUT0~EFUSE_OUT7读出数据,开始进入数据的解密过程。高级加密标准AES算法大致可分为电码本模式(ECB)、密码分组链接模式(CBC)、计算器模式(CTR)、密码反馈模式(CFB)、输出反馈模式(OFB)。通常在AES中用到的算法为密码分组链接模式(CBC),这种模式是先将明文切分成若干小段,然后每一小段与初始块或者上一段的密文段进行异或运算后再与密钥进行加密。这种模式的优点是不容易主动攻击,安全性好于ECB,适合传输长度长的数据。缺点是不利于并行计算,误差传递,需要初始化密钥向量。此加密已经通过软件应用于FPGA下载bitstream中,在本文中将此加密模式的反过程称为CBC解密。下面同样也从加密原理讨论OFB解密。输出反馈模式(OFB)解密可以将块密码变成同步的流密码,并形成密钥流的块逻辑,然后将其与明文块逻辑进行异或,得到密文。与其他流密码一样,解密时密文中一个位的翻转会使明文中同样位置的位也产生翻转。这种特性使得许多错误校正码可以得出正确的结果,例如奇偶校验位。每个使用OFB的输出块与其前面所有的输出块相关,因此不能进行并行化处理。然而,由于明文和密文只在最终的异或过程中使用,因此可以事先对密钥初始向量进行加密,最后将明文或者密文进行并行的异或处理。可以利用输入全0的CBC模式产生OFB模式的密钥流。这种方法十分实用,因此可以利用快速的CBC硬件实现来加速OFB模式的加密过程,OFB模式的优点是相对于CBC模式减少了初始化密钥向量。

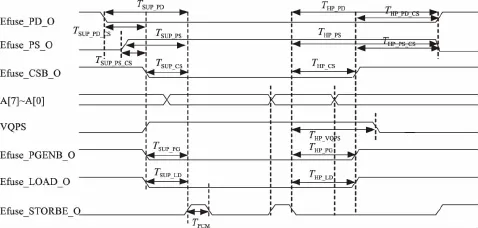

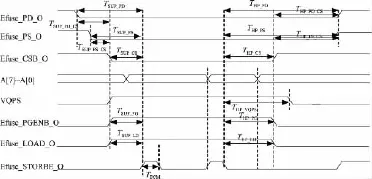

图4、图5分别为EFUSE写过程、读过程的时序图,图中对信号的建立时间和保持时间都进行了标注。其中Efuse_pd_o为下电过程,只有当此信号为低电平时才开始读写操作;Efuse_ps_o在写过程中为高,表示满足写操作的电压;Efuse_csb_o为片选使能;A[7]~A[0]为地址线;VQPS为2.5 V电压;Efuse_pgenb_o为写使能信号;Efuse_load_o为数据放大器开启使能;Efuse_storbe_o为读写操作使能端。

4 仿真验证

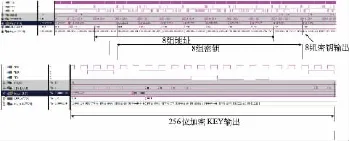

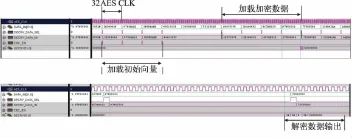

采用基于verilog行为级描述的RTL代码建立整个仿真验证环境,利用Cadence公司仿真工具NC[3]进行设计仿真验证。图6通过仿真介绍了加密KEY的下载过程,可以看出,密钥是通过每32位一个地址并行加载密钥,分8次完成,并将256位加密KEY完整地输出。图7仿真介绍了在下载bitstream之前需要加载加密初始向量,在完成初始向量加载之后开始下载加密数据,每4组32 bits数据进行解密一次。图7为将密文解密输出放大图,例如当加载的密文为F7F66641时,可以看出解出的明文为00000000,完成数据解密。

图3 EFUSE存储阵列

图4 EFUSE写接口时序

图5 EFUSE读接口时序

图6 加载加密KEY

图7 解密数据

5 小结

本文基于AES算法,设计了高效安全的配置模式,分别采用SRAM和EFUSE两种存储器存储Encryption KEY,实现高效存储;采用不同解密模式对加密数据进行更安全的解密处理,将 Encrypted bitstream更灵活地下载到FPGA内的配置SRAM中,实现了具有高效、安全、兼容性强等特点的FPGA配置模式。

[1]Joan Daemen,Vincent Rijmen.高级加密标准(AES)算法——Rijndael的设计[M].谷大武,徐胜波,译.北京:清华大学出版社,2003:65-72.

[2]胡向东,魏琴芳,著.应用密码学教程[M].北京:电子工业大学,2005:78-94.

[3]Rabaey,JM.数字集成电路——电路、系统与设计 (第二版)[M].周润德,等译.北京:电子工业出版社,2004: 319-357.

[4]VAND G.Using march test to test SRAM[J].IEEE Design &Test,1993,10(1):8-14.

[5]崔建双,李铁克,张文新.对称加密算法Rijndael及其编程实现[J].计算机工程,2004,13:5-10.

Design of an FPGA-based Efficient and Safe Configuration Mode

ZHUANG Xueya1,WANG Xinghong1,YAN Hua2

(1.China Electronics Technology Group Corporation No.58 Research Institute,Wuxi214072,China;2.East Technologies,inc.Wuxi214072,China)

With the application field of FPGA constantly expanding,researches of downloading bitstream securely and reliably are also expanding.In the paper develops an FPGA-based circuit based on AES algorithm using SRAM and EFUSE storage to store Encryption KEY and two kinds of decryption circuits.The new design downloads the encryption bitstream to SRAM within the FPGA more efficiently,securely and flexibly.The new design is proved to be feasible and practical after the analysis of corresponding digital simulation waveform.

AES algorithm;SRAM;EFUSE;FPGA;configuration;encryption

TN402

A

1681-1070(2017)04-0020-04

庄雪亚(1986—),男,江苏江阴人,本科,工程师,研究方向为千万门级FPGA设计与验证。

2016-12-02