野战有线远传接口测试信号源的设计与实现

孙慧贤,李召瑞,谭月辉,袁 扬,尹文龙(军械工程学院,石家庄 050003)

野战有线远传接口测试信号源的设计与实现

孙慧贤,李召瑞,谭月辉,袁 扬,尹文龙

(军械工程学院,石家庄 050003)

针对野战有线远传通信接口的测试需求,设计了一种基于xDSL技术的接口测试信号源。以可编程数字器件(FPGA)为核心,配合通用模拟前端,构建可编程和可重配置的硬件接口电路。利用硬件描述语言,完成成帧解帧、加扰解扰、编码解码、滤波等功能,实现HDSL接口电路功能。实验结果表明,设计的HDSL接口功能实现正常,允许用户通过修改程序代码和系统输入来实现对接口的动态配置和维护更新,有效地解决了以集成芯片为基础的传统HDSL接口灵活性差和维护成本高的问题,并为其他信号接口系统的设计实现提供了有益的参考。

野战有线远传,接口测试,信号源,xDSL技术

0 引言

通信接口测试是指挥控制系统通信设备基层级维修保障的重要组成部分。现役指挥控制系统装备具有种类多、型号多、多种技术体制并存的特点,导致系统传输接口种类繁多。现有接口测试设备主要采用专用芯片构建与被测接口相同的硬件电路的方法,只能实现对某一型号接口收发功能测试,专用性强,功能单一,测试效率低。

基于xDSL技术的有线远传通信是目前野战有线传输的主要方式[1]。在xDSL技术中,高比特率数字用户线(High Bit Rate Digital Subscriber Line,HDSL)是野战通信系统中使用最多的通信接口[2]。目前国内外对HDSL信号接口的实现方法大多是以高度集成化的专用DSL收发芯片为核心来构建硬件电路,虽然实现过程简单,但是远离了对HDSL接口底层技术的分析与实现,接口灵活性、通用性不足,无法完成对多种具有专用协议的军用通信接口测试。

研究在通用硬件平台上对指挥控制系统装备多种通信接口测试信号源的可重构设计与实现方法,可增强通信接口测试的通用型和灵活性,可提高测试设备的测试效率。基于此,本文针对野战有线远传通信接口可重构测试需求,以HDSL接口测试为例,设计了一种通信接口测试信号源。该信号源的总体设计采用模块化思想,以FPGA为核心,配合通用模拟前端,构建硬件平台,在此基础上,利用硬件描述语言,完成成帧解帧、加扰解扰、编码解码、滤波等功能。

1 系统总体设计

系统设计过程中,首先分析HDSL接口标准及其工作的基本原理,然后结合国际标准(ITU-T G. 991.1)规范[3]要求,采用模块化设计思路,设计了接口测试信号源。

按照ITU-T G.991.1标准,HDSL链路以网络终端单元(NTU)和线路终端单元(LTU)为核心,辅以信号再生器(REG)和数字本地线(DLL),构成了完整的HDSL链路,其链路模型如图1所示。

图1HDSL链路模型图

从图1中可看出,HDSL接口系统的核心部分主要包括用户/网络接口、映射和维护模块、公共电路和HDSL收发器,分别完成信号的成帧与解帧、扰码与解扰码、编码与解码和滤波等功能,实现用户数据和HDSL信号之间的转换与HDSL信号的发送与接收。

为了增强HDSL接口系统的灵活性和重配置能力,根据HDSL链路结构特点,HDSL接口测试信号源分为FPGA信号处理单元和模拟前端两部分实现,其中FPGA信号处理单元实现对HDSL数字数据的处理,模拟前端实现数模/模数转换和相应的滤波功能,接口总体设计如图2所示。

2 FPGA信号处理单元设计

FPGA是当前实现快速数字系统的主流硬件平台,具有强大的数字信号处理能力和可重配置能力,能够实现复杂时序逻辑功能,以FPGA为硬件平台可大大提高HDSL接口的可重配置能力和灵活性,降低接口实现和升级成本[4]。本文以Xilinx Spartan-6 FPGA为硬件开发环境,将FPGA信号处理单元分为发送端和接收端两部分以模块化进行设计实现,下面进行详细讲述。

图2 HDSL接口测试信号源总体设计图

2.1 FPGA信号处理单元发送端设计

FPGA信号处理单元发送端主要功能模块包括核心帧成帧器、扰码器、HDSL帧成帧器、2B1Q编码器和FIR滤波器,负责对用户数据实现成帧、扰码、编码和低通滤波等功能,将用户数据转换成符合HDSL标准的格式,并配合AFE1230模拟前端生成最终的HDSL信号。

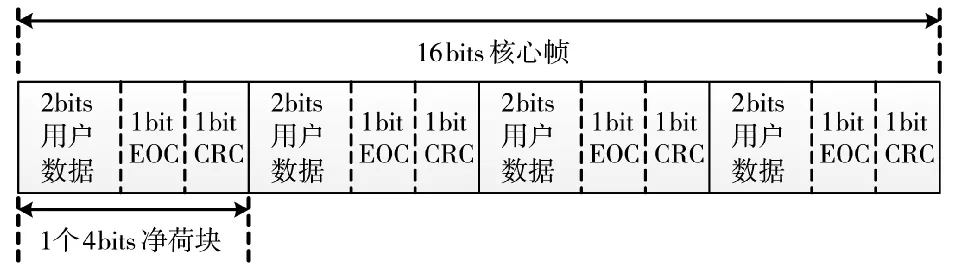

2.1.1 核心帧成帧器

核心帧是HDSL帧的核心部分,是HDSL信息的主要承载者,其帧结构如图3所示。本文设计的16 bits核心帧包括4个4 bits HDSL净荷块,每个净荷块由2个用户数据比特、1个循环冗余校验比特(Cyclic Redundancy Check,CRC)和1个嵌入操作通道比特(Embedded Operation Channel,EOC)组成,在传递数据的同时可实现HDSL信号的校验和对HDSL通信链路的控制,提高了HDSL信号的传输性能。

图3 核心帧结构图

核心帧成帧器负责先将8 bits用户数据分为4组,然后在每组的末尾插入CRC比特和EOC比特,将用户数据封装为HDSL核心帧。本文设计的核心帧成帧器设有专门的CRC比特和EOC比特输入端口,用户可随时通过更改核心帧的CRC比特和EOC比特实现对HDSL信号的校验和对HDSL通信链路的控制,提高了接口系统的灵活性和可重配置能力。

2.1.2 扰码器和HDSL帧成帧器

为了防止因为核心帧中连“0”码或连“1”码过长而影响位同步的建立和保持,从而降低接收端信号接收的性能[5],本文设计了16阶并行扰码器对核心帧进行扰码,减少了核心帧中连“0”码和连“1”码的数量,扰码多项式为:

HDSL帧成帧器负责对扰码后的核心帧添加帧头和填充比特,将核心帧封装为最终的HDSL帧格式。本文选择4位巴克码“1110”作为HDSL帧头,配合扰码器提高了接收端帧定位的准确性,并在HDSL帧尾添加2个填充比特以满足接收端HDSL接收时序特性。

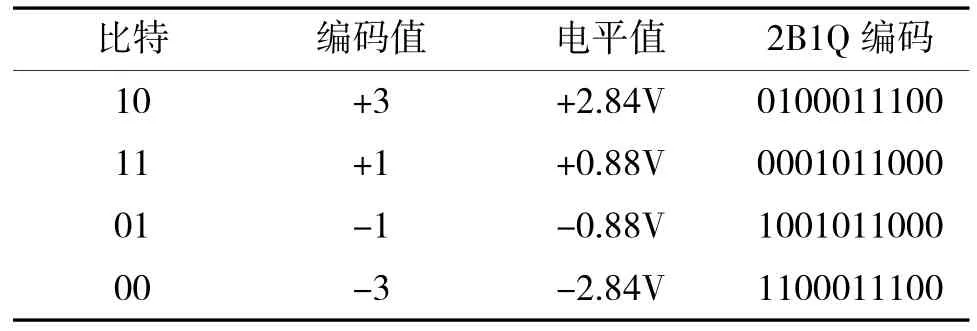

2.1.3 2B1Q编码器

ITU-T G.991.1标准中推荐采用2B1Q线路编码方式,将HDSL帧编码为无冗余度的4电平脉冲幅度调制码,每两比特对应一个有符号浮点数电平值。由于FPGA不能进行浮点数处理,本文先将有符号浮点数电平值放大100倍,并用10位有符号二进制代码表示,实现了浮点数到定点数的转换,其映射关系如表1所示。

表1 2B1Q编码映射表

本文设计的2B1Q编码器先将接收到的HDSL帧进行缓存,并分为每两比特为一组,然后以11倍的HDSL帧速率按照表1中的映射关系将22位HDSL帧编码为10位有符号电平值,实现对核心帧的2B1Q编码。

2.1.4 FIR滤波器

有限长冲激响应(Finite Impulse Response,FIR)滤波器是数字信号处理的基本模块之一,可以在保证满足滤波器幅频响应的同时,获得严格的线性相位特性,在现代数字信号处理领域得到了广泛应用[6]。本文结合MATLAB的FDAtool工具和ISE14.6开发套件的IP核,设计了符合HDSL接口传输特性的FIR滤波器,滤波器的幅频响应曲线如图4所示。

图4 FIR滤波器幅频响应曲线图

为保证FIR滤波器对HDSL信号的低通滤波性能,本文设计的FIR滤波器阶数为147,并以23.2 Mbit/s采样速率对HDSL帧进行10倍过采样。经过滤波后,数据以10个点表示一个电平值,每个点用29位数据表示,大大提高了HDSL帧传输的准确性和传输性能。

2.2 FPGA信号处理单元接收端设计

FPGA信号处理单元接收端是发送端的逆过程,配合AFE1230模拟前端实现对HDSL信号的接收并将其转换为用户数据。FPGA接收端主要包括FIR滤波器、2B1Q解码器、HDSL帧判决器、HDSL解帧器、解扰器和核心帧解帧器,实现了对AFE1230发送过来的HDSL信号的低通滤波、2B1Q解码、HDSL帧解帧、解扰码和核心帧解帧等功能,下面对2B1Q解码器和HDSL帧判决器进行讲述,其他模块与发送端对应模块实现理论相似,在此不作赘述。

2.2.1 2B1Q解码器

FPGA信号处理单元接收端的2B1Q解码器是发送端2B1Q编码器的逆过程,负责按照和表1相反的映射关系将FIR滤波器传输过来的10位电平值转换为2 bits信息,并发送到HDSL判决器,是接收端功能实现的基础。

2.2.2 HDSL帧判决器

HDSL帧的判决负责在位同步信息的基础上识别出数字信息帧的起止时刻,是FPGA信号处理单元接收端准确实现HDSL帧解帧的基础[7]。

本文设计的HDSL帧判决器在已知HDSL帧头的前提下,采用逐项相关法,通过缓存器、逐项相关器和比较器等模块,实现对2B1Q解码后的HDSL数据的缓存、逐项相关、门限判决和HDSL帧生成等功能,配合FPGA信号处理单元发送端的扰码器完成了HDSL帧的正确识别,提高了HDSL帧解帧的准确性。

3 模拟前端设计

HDSL信号的数模/模数转换由模拟前端部分实现,直接影响HDSL信号的发送接收性能。传统HDSL接口通过使用基础元器件制作电路板来实现模拟前端功能,此方法虽然能在一定程度实现模拟前端功能,但是电路板设计周期长、成本高、稳定性差。

AFE1230芯片是德州仪器公司制造的模拟前端芯片,配合上层FPGA数字信号处理部分和OPA2677线路驱动器可在135 Ω负载线路上生成17.3 dBm功率的HDSL信号。AFE1230模拟前端稳定性好,可实现信号的数模/模数转换、滤波和回拨抵消等功能,大大降低HDSL设备的尺寸和成本,有效地提高了HDSL信号的发送和接收性能。

如下页图5所示,AFE1230芯片通过5路串行信号接口实现与上层FPGA数字信号处理单元的通信。其中MCLK、txData、txBaud和rxBaud由FPGA 向AFE1230发送,实现FPGA对AFE1230的控制。

MCLK是 AFE1230的内部主时钟;txBaud、rxBaud分别控制发送端和接收端数据波特的传输,帮助AFE1230对数据帧的识别和发送,两者必须相同且和MCLK同步,每周期包含48个MCLK周期,与MCLK共同实现对AFE1230的时序控制;每一个txBaud周期txData包含2个16位数据字和2个8位控制字,其中2个16为数据字用于实现帧定位和传输数据,2个8位控制字实现对AFE1230芯片内部功能单元参数的设定。AFE1230通过rxData向FPGA发送数据,与txData结构相似,但一般仅考虑其数据传输功能。

图5 AFE1230与FPGA数字接口连接图

4 实验结果与分析

本文采用Verilog语言对上述HDSL接口测试信号源的功能模块进行了编程实现,并利用Xilinx14.6软件的ISim模块进行了仿真实验,仿真实验结果如图6所示。

图6 HDSL接口信号源FPGA仿真实验结果图

FPGA系统主时钟为clk,复位信号为reset, clk11和clk110是主时钟频率的11倍和110倍,分别是2B1Q编码器和FIR滤波器的时钟,core_frame [7:0]是系统用户数据的输入,在不影响实验效果的基础上,本仿真实验中将CRC位和EOC位全设为1。由图6可看出,用户数据先经过核心帧成帧器、扰码器和HDSL成帧器的处理生成了符合HDSL标准帧格式的信号hdsl_frame2[21:0],2B1Q编码器对 HDSL帧进行编码生成 10位电平值frame_2b1q[9:0],然后FIR滤波器以10倍过采样对frame_2b1q[9:0]进行低通滤波,最后将滤波后的信号整理格式后发送到AFE1230模拟前端,实现了HDSL信号的生成和发送。

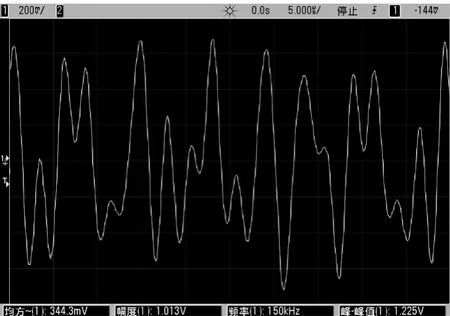

图7所示为野战有线远传接口测试信号源输出的HDSL接口信波形,从中可看出,该接口可输出符合HDSL技术要求的测试波形。

图7 HDSL接口信号源输出波形

5 结论

本文针对野战有线远传通信接口测试需求,设计了一种HDSL接口测试信号源,仿真实验结果表明,该方法设计的HDSL接口功能正常、稳定性良好,并允许用户通过软件编程或修改系统输入实现对接口的动态配置和维护更新,有效地解决了以集成芯片为基础实现的传统HDSL接口灵活性和扩展性差的问题,大大降低了接口系统的构建和维护成本。这种采用可编程数字器件配合通用模拟前端构建的接口测试信号源,易于通过功能扩展用于其他野战有线远传通信接口的测试,从而实现通信接口的可重构测试。

[1]李大芳.一种高可靠性的保密野战通信系统方案[J].电讯技术,2013,53(6):704-706.

[2]韩鹰,王武斌,岳涛.基于xDSL技术的被复线有线远传组网技术[J].火力与指挥控制,2013,38(6):163-165.

[3] ITU-T.High bit rate digital subcriber line(HDSL)transceivers.G.991.1[S].1998.10:1-20.

[4]裴劲涛,王育荣,陆海伟.用FPGA实现ISDN-U接口设计[J].无线电工程,2007,37(12):46-48.

[5]田松,刘皓,李少谦.并行扰码器设计与FPGA实现[C]// 2006中国西部青年通信学术会议论文集,2006:421-424.

[6]郭继昌,向晖,滕建辅,等.基于FPGA的FIR滤波器的实现[J].电子技术应用,2000,26(5):60-62.

[7]胡莉,张力伟,周希元.帧同步检测技术的研究进展[J].无线电工程,2009,39(2):12-15.

Design and Implementation of Signal Generator in Field Wired Far-distance Transmission Interface Testing

SUN Hui-xian,LI Zhao-rui,TAN Yue-hui,YUAN Yang,YIN Wen-long

(Ordnance Engineering College,Shijiazhuang 050003,China)

According to the test requirements of field wired remote communication interface,an interfacetestsignalsourcebased on xDSL technologyisdesigned.Theprogrammable and reconfigurable hardware interface circuit is constructed with the core of FPGA and the universal analog front end.Using the hardware description language,functions of framing and de-framing,scrambling and descrambling,encoding and decoding,and filtering are realized,which achieves the function of HDSL interface circuit.Through the experiment result,it is shown that the function of the HDSL interface designed in this paper is normal,and allows users to achieve the dynamic configuration and maintenance of the interface by modifying the program code and the system input,which can effectively solve the problem of traditional HDSL interface based on integrated chip with poor flexibility and high cost of maintenance,and provides a useful reference for the design and implementation of other signal interface systems.

field wired far-distance transmission,interface testing,signal generator,xDSL

TP336

A

1002-0640(2017)03-0179-04

2016-02-25

2016-03-28

孙慧贤(1980- ),男,内蒙古临河人,博士,讲师。研究方向:指挥控制系统工程。